# GENERAL DESCRIPTION

NOTES

#### **GENERAL DESCRIPTION**

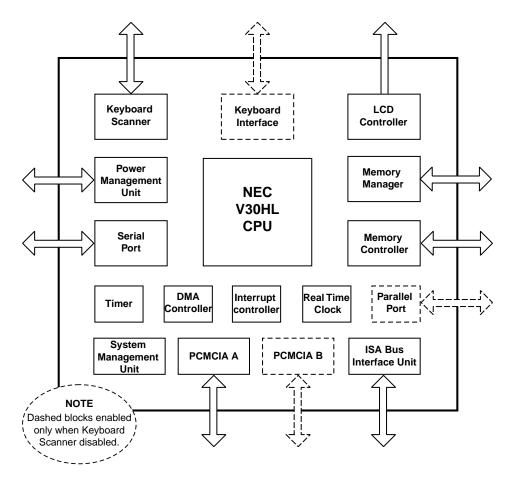

The Vadem VG230 is a one-chip PC platform which provides a highly battery-efficient basis for OEMs to develop cost sensitive, DOS-based personal electronic products. The chip contains all standard XT peripherals, additional high-value peripherals and an ISA bus. For long battery life, the VG230 offers extensive and proven power management capability. In addition to a +5V version, a version is offered which operates at +3V.

The VG230 contains the 8086-compatible 16 MHz NEC V30HL processor. It also embodies a standard XT architecture combined with hardware and software features facilitating the rapid design of products with extensive ROM-based software. PC Card mass storage and miniature peripherals (I/O cards) following the PCMCIA 2.1 (JEIDA 4.1) standard are supported. The VG230 is packaged in a single 160-pin CMOS chip and handles all PC functions including 16-bit CPU, XT core logic, LCD controller, keyboard scanner and PC Card controller. All that is required for a basic system is the VG230, memory, power supply, display and associated packaging.

#### **PRODUCT OVERVIEW**

- Single-chip permits glueless implementation of a fully compatible PC-XT.

- Standard-design 16-bit, 16 MHz NEC V30HL processor core integrated on-chip.

- Complete hardware and firmware support for memory-saving "execute-in-place" ROM applications.

- Field-proven, industry standard power management based on activity monitoring lengthens battery life.

- Scans up to 101 keys without an external keyboard controller.

- Integrated CGA LCD controller and 640x400 AT&T standard controller. Supports a wide variety of panel resolutions from below CGA to 400-line displays.

- LCD controller supports hardware "ink plane" for pen-based applications.

- Dual PCMCIA 2.1 (JEIDA 4.1) PC Card slot support allowing "hot" insertion/removal (with external buffers).

- Integrated serial port, real-time clock, programmable interrupt controller, DMA controller and internal timer.

- Deactivating keyboard scan enables a second PCMCIA card slot, a bi-directional parallel. port and a standard XT keyboard interface.

- Support for DRAM, SRAM and PSRAM memory.

- Supports up to eight 8-bit RAM banks and up to six 16-bit RAM banks.

- ICE support simplifies debugging of system designs.

- 8250 compatible UART.

- XT keyboard interface.

- EMS 4.0 compatible memory subsystem, supports up to 64Mbytes.

- Real Time Clock with CMOS RAM

- Vadem Power Management Unit (PMU)

- Optionally combines with external VG-660 single-chip LCD VGA controller to drive 640x480 and lower resolution VGA compatible LCD panels.

#### **VG230 BLOCK DIAGRAM**

# CONNECTION AND PIN DESCRIPTIONS

NOTES

#### CONNECTION AND PIN DESCRIPTIONS

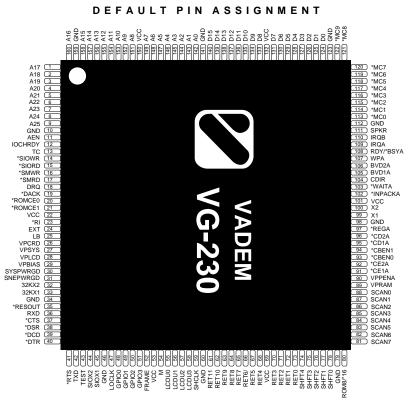

#### VG230 PIN ASSIGNMENT

#### ALTERNATIVE PIN DEFINITIONS

| PIN # | DEFAULT | ALTERNATIVE(S)   |

|-------|---------|------------------|

| 48    | GPIO0   | LCDL0, *DACK0    |

| 49    | GPIO1   | LCDL1, ALE       |

| 50    | GPIO2   | LCDL2, SYSCLK    |

| 51    | GPIO3   | LCDL3            |

| 54    | м       | *DACK0           |

| 61    | RET11   | PDOE             |

| 62    | RET10   | VPPENB           |

| 63    | RET9    | AFD              |

| 64    | RET8    | SLCT             |

| 65    | RET7    | *ERR             |

| 66    | RET6    | SEL              |

| 67    | RET5    | PE               |

| 68    | RET4    | ACK              |

| 70    | RET3    | BUSY             |

| 71    | RET2    | *RDY/BSYB, IREQB |

| 72    | RET1    | WPB              |

| 73    | RET0    | *WAITB           |

| PIN # | DEFAULT   | ALTERNATIVE(S)  |

|-------|-----------|-----------------|

| 74    | SHFT4     | *CD1B           |

| 75    | SHFT3     | *CD2B           |

| 76    | SHFT2     | BVD1B, *STSCHGB |

| 77    | SHFT1     | BVD2B, *SPKRB   |

| 78    | SHFT0     | *INPACKB        |

| 81    | SCAN7     | KBCLK           |

| 82    | SCAN6     | KBDAT, IRQ1     |

| 83    | SCAN5     | *CE1B           |

| 84    | SCAN4     | *CE2B           |

| 85    | SCAN3     | *REGB           |

| 86    | SCAN2     | PDCLKU, PDCLKB  |

| 87    | SCAN1     | INIT            |

| 88    | SCAN0     | STB             |

| 105   | BVD1A     | STSCHGA         |

| 106   | BVD2A     | *SPKRA          |

| 107   | WPA       | *IOIS16A        |

| 108   | RDY/*BSYA | *IREQA          |

NOTE: The VG-230 does not contain pull-up/pull-down resistors. All unused inputs should be terminated.

#### **PIN DESCRIPTIONS**

The VG 230 Pin Descriptions Table contains the VG230 pin definitions in alphabetical order by pin name. Pins which have alternative functions are listed under each function's symbol. Alternative functions are enabled and disabled by setting various VG230 registers. These are:

- Keyboard Mode Register (08H)

- GPIO Mode Register (32H)

- PC Card Slot 0 Control Register (21H)

- PC Card Slot 1 Control Register (27H)

- LCD Configuration Control Register (07H)

- PIO Mode Register (18H)

| Symbol    | Туре | Pin Number               | Description                                                                                                                                                                                                                        |

|-----------|------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32KX[2:1] | XTL  | 32,33                    | 32.768 KHz crystal connection.                                                                                                                                                                                                     |

| A[25:0]   | 0    | 9-1, 158-151,<br>149-142 | System Address Bus. All external memory and I/O devices attach to this common address bus. The function of this bus is dynamically set according to the device type addressed: DRAM, SRAM, PC Card, ROM, I/O, or Expansion memory. |

| *ACK      | Ι    | 68                       | Parallel port *ACK input (when keyboard scanner disabled by Keyboard Mode Register, 08H). The default definition of this pin is RET4.                                                                                              |

| AEN       | Ο    | 11                       | Address Enable. Output from 8237A DMA<br>Controller Macro.                                                                                                                                                                         |

| AFD       | 0    | 63                       | Parallel port AFD control output (when keyboard scanner disabled by Keyboard Mode Register, 08H).<br>AFD must be inverted using a 74XX05-type open collector device. The default definition of this pin is RET9.                   |

| ALE       | 0    | 49                       | Address Latch Enable signal (when enabled by<br>GPIO Mode Register, 32H). Alternatively, LCDL1<br>for 400-line LCD panels may be enabled using this<br>register. The default definition of this pin is GPIO1.                      |

#### VG230 Pin Descriptions Table

# CONNECTION AND PIN DESCRIPTIONS

| Symbol     | Туре | Pin Number | Description                                                                                                                                                                                                                                                                                                                                |

|------------|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSY       | Ι    | 70         | Parallel port BUSY input (when the keyboard<br>scanner disabled by Keyboard Mode Register, 08H).<br>The default definition of this pin is RET3.                                                                                                                                                                                            |

| BVD[2:1]A  | Ι    | 106,105    | Battery voltage status inputs for slot 'A' PC memory<br>cards. May be re-defined for I/O cards to *SPKRA<br>and STSCHGA respectively by the PC Card Slot 0<br>Control Register (21H).                                                                                                                                                      |

| BVD[2:1]B  | I    | 77,76      | Battery voltage status inputs for slot 'B' PC memory<br>cards (when keyboard scanner disabled by Keyboard<br>Mode Register, 08H). Pins [2:1] may be set to<br>*SPKRB and STSCHGB respectively for I/O cards<br>by using the PC Card Slot 1 Control Register (27H).<br>The default definitions of these pins are SHFT[1:2]<br>respectively. |

| *CBEN[1:0] | 0    | 94,93      | Enable signal for PC Card Odd and Even Byte data buffers.                                                                                                                                                                                                                                                                                  |

| CDIR       | 0    | 104        | Direction control for PC Card Odd and Even Byte data buffers.                                                                                                                                                                                                                                                                              |

| *CD[2:1]A  | Ι    | 96,95      | Card detect status inputs from slot 'A' PC Card.                                                                                                                                                                                                                                                                                           |

| *CD[2:1]B  | Ι    | 75,74      | Card detect status inputs from slot 'B' PC Card<br>(when keyboard scanner disabled by Keyboard Mode<br>Register, 08H). The default definitions of these pins<br>are SHFT[3:4] respectively.                                                                                                                                                |

| *CE[2:1]A  | Ο    | 92,91      | PC Card Even/Odd byte chip select signals for slot 'A.'                                                                                                                                                                                                                                                                                    |

| *CE[2:1]B  | 0    | 84,83      | PC Card Even/Odd byte chip select signals for slot<br>'B' (when keyboard scanner disabled by Keyboard<br>Mode Register, 08H). The default definitions of<br>these pins are SCAN[4:5] respectively.                                                                                                                                         |

| *079       | т    | 27         | Savial Dart algor to good                                                                                                                                                                                                                                                                                                                  |

| *CTS       | I    | 37         | Serial Port clear to send.                                                                                                                                                                                                                                                                                                                 |

# CONNECTION AND PIN DESCRIPTIONS

# VADEM VG230

| Symbol  | Туре | Pin Number          | Description                                                                                                                                                                                                      |

|---------|------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[15:0] | I/O  | 140-133,<br>131-124 | Bi-directional System Data Bus. All external<br>memory and I/O devices attach to this common data<br>bus. 8 bit devices will reside on the D[7:0] half of<br>the system data bus.                                |

| *DACK   | 0    | 19                  | DMA Acknowledge. Output from 8237A DMA<br>Controller Macro. Selected from one of<br>*DACK[3:1] depending upon which of DRQ[3:1] is<br>programmed by user.                                                        |

| *DACK0  | 0    | 48                  | Internal *DACK0 signal REFRESH (when enabled<br>by GPIO Mode Register, 32H). Alternatively,<br>LCDL0 for 400-line LCD panels may be enabled by<br>this register. The default definition of this pin is<br>GPIO0. |

| *DACK0  | 0    | 54                  | Internal *DACK0 signal REFRESH (when LCD controller disabled by LCD Configuration Control Register, 07H). The default definition of this pin is M.                                                               |

| *DCD    | Ι    | 39                  | Serial Port data carrier detect.                                                                                                                                                                                 |

| DRQ     | I    | 18                  | DMA Request. Input to 8237A DMA Controller<br>Macro. User programmable to be one of DRQ[3:1].                                                                                                                    |

| *DSR    | I    | 38                  | Serial Port data set ready.                                                                                                                                                                                      |

| *DTR    | 0    | 40                  | Serial Port data transmit ready.                                                                                                                                                                                 |

| *ERR    | I    | 65                  | Parallel port *ERR input (when keyboard scanner<br>disabled by Keyboard Mode Register, 08H). The<br>default definition of this pin is RET7.                                                                      |

| EXT     | I    | 24                  | External switch input. To activate SUSPEND/RESUME.                                                                                                                                                               |

| FRAME   | 0    | 52                  | Frame clock to LCD.                                                                                                                                                                                              |

# CONNECTION AND PIN DESCRIPTIONS

| Symbol    | Туре | Pin Number | Description                                                                                                                                                                                                                                                                                                                                            |

|-----------|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO{3:0] | I/O  | 51-48      | General Purpose Input/Output signals. Data<br>direction is set by the GPIO Mode Register (32H).<br>This register also enables other definitions for these<br>pins. See LCDL, SYSCLK, ALE and *DACK0 for<br>further information.                                                                                                                        |

| INIT      | Ο    | 87         | Parallel port INIT control output (when keyboard scanner disabled by Keyboard Mode Register, 08H). This output must be inverted using a 74XX05 type open collector device. The default definition of this pin is SCAN1.                                                                                                                                |

| *INPACKA  | Ι    | 102        | Input acknowledge from slot 'A' PC I/O cards.                                                                                                                                                                                                                                                                                                          |

| *INPACKB  | Ι    | 78         | Input acknowledge from slot 'B' PC I/O Cards<br>(when keyboard scanner disabled by Keyboard Mode<br>Register, 08H). The default definition of this pin is<br>SHFT0.                                                                                                                                                                                    |

| IOCHRDY   | Ι    | 12         | I/O Channel Ready. Input OR'ed with internal ready sources to insert CPU wait states.                                                                                                                                                                                                                                                                  |

| *IOIS16A  | Ι    | 107        | Register width status from slot 'A' PC I/O Cards.<br>Enabled by the PC Card Slot 0 Control Register.<br>The default definition of this pin is WPA.                                                                                                                                                                                                     |

| *IOIS16B  | I    | 72         | Register width status from slot 'B' PC I/O Cards<br>(when keyboard scanner disabled by Keyboard Mode<br>Register, 08H and I/O mode enabled using PC Card<br>Slot 1 Control Register, 27H). When the keyboard<br>scanner is disabled, the default definition of this pin<br>is WPB. When the scanner is enabled, the definition<br>of this pin is RET1. |

| IRQ1      | I/O  | 82         | Interrupt signal from external keyboard controller<br>(when reads from VG230 keyboard registers<br>disabled by Keyboard Mode Register, 08H). When<br>reads are enabled, pin definitions SCAN6 (default)<br>or KBDAT may be set by the Keyboard Mode<br>Register.                                                                                       |

# CONNECTION AND PIN DESCRIPTIONS

# VADEM VG230

| Symbol     | Туре | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQA, IRQB | I    | 109,110    | System interrupt request. Interrupt request inputs to internal 8259A Macro. User programmable to be one of IRQ[7:2].                                                                                                                                                                                                                                                                                                                                       |

| KBCLK      | I/O  | 81         | External keyboard KBCLK input (when keyboard scanner disabled by Keyboard Mode Register, 08H). The default definition of this pin is SCAN7.                                                                                                                                                                                                                                                                                                                |

| KBDAT      | I/O  | 82         | External keyboard KBDAT input (when keyboard scanner disabled by Keyboard Mode Register, 08H).<br>The default definition of this pin is SCAN6.                                                                                                                                                                                                                                                                                                             |

| LB         | Ι    | 25         | Low Battery warning input.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LCDL[3:0]  | 0    | 51-48      | Display data for lower half of 400 line LCDs (when<br>enabled by GPIO Mode Register, 32H). This register<br>may also be used to select other definitions for these<br>pins. See LCDL, SYSCLK, ALE, *DACK0 and<br>GPIO (default) for further information.                                                                                                                                                                                                   |

| LCDU[3:0]  | О    | 58-55      | Display data for 200-line LCDs or for the upper half of 400 line LCDs.                                                                                                                                                                                                                                                                                                                                                                                     |

| LOCLK      | 0    | 47         | Load clock to LCD.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| М          | 0    | 54         | Low frequency clock to LCD. When the LCD controller is disabled by the LCD Configuration Control Register (07H), this pin becomes *DACK0.                                                                                                                                                                                                                                                                                                                  |

| *MC[9:0]   | 0    | 122-113    | System RAM control. Outputs defined in Table 1-2.                                                                                                                                                                                                                                                                                                                                                                                                          |

| *PDCLKB    | 0    | 86         | Active low bidirectional parallel port data clock<br>(when keyboard scanner disabled by Keyboard<br>Mode Register, 08H and bidirectional operation<br>enabled by PIO Mode Register, 18H). Asserted<br>during accesses to the Parallel Port Data Register.<br>*PDCLKB must be qualified externally with<br>*SIOWR using a 74XX32 'R' gate to write data and<br>with PDOE to control a 74XX244 to read data. The<br>default definition of this pin is SCAN2. |

# CONNECTION AND PIN DESCRIPTIONS

| Symbol    | Туре | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDCLKU    | 0    | 86         | Unidirectional parallel port data clock (when<br>keyboard scanner disabled by Keyboard Mode<br>Register, 08H). Internally qualified with *SIOWR to<br>drive directly the CLK pin of an external 74XX374<br>octal D F/F for latching printer data. When the PIO<br>Mode Register (18H) enables bidirectional<br>operation, this pin becomes *PDCLKB. The default<br>definition of this pin is SCAN2. |

| PDOE      | Ο    | 61         | Parallel Port Output Enable (when keyboard scanner<br>disabled by Keyboard Mode Register, 08H and<br>bidirectional operation enabled by PIO Mode<br>Register, 18H). The default definition of this pin is<br>RET11.                                                                                                                                                                                 |

| PE        | I    | 67         | Parallel port PE input (when keyboard scanner<br>disabled by Keyboard Mode Register, 08H and<br>bidirectional operation enabled by PIO Mode<br>Register, 18H). The default definition of this pin is<br>RET5.                                                                                                                                                                                       |

| RDY/*BSYA | Ι    | 108        | Ready/*Busy status input from slot 'A' PC memory<br>cards. PC Card Slot 0 Control Register (21H) may<br>be used to redefine this pin as *IREQA for I/O<br>cards.                                                                                                                                                                                                                                    |

| RDY/*BSYB | I    | 71         | Ready/*Busy status input from slot 'B' PC Memory<br>Card (when keyboard scanner disabled by Keyboard<br>Mode Register, 08H). PC Card Slot 1 Control<br>Register (27H) may be used to redefine this pin as<br>*IREQB for I/O cards. The default definition of this<br>pin is RET2.                                                                                                                   |

| *REGA     | 0    | 97         | PC Card register select signal for slot 'A.'                                                                                                                                                                                                                                                                                                                                                        |

| *REGB     | 0    | 85         | PC Card register select signal for slot 'B' (when<br>keyboard scanner disabled by Keyboard Mode<br>Register, 08H). The default definition of this pin is<br>SCAN3.                                                                                                                                                                                                                                  |

| *RESOUT   | 0    | 35         | Active low system RESET output.                                                                                                                                                                                                                                                                                                                                                                     |

# CONNECTION AND PIN DESCRIPTIONS

# VADEM VG230

| Symbol      | Туре | Pin Number      | Description                                                                                                                                                                                                                                                      |

|-------------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RET[11:0]   | I    | 61-68,<br>70-73 | Return inputs from external key matrix. The<br>Keyboard Mode Register (08H) also enables other<br>definitions for these pins. See PDOE, VPPENB,<br>AFD, SLCT, *ERR, SEL, PE, *ACK, BUSY,<br>RDY/*BSYB, *IREQB, WPB, *IOIS16B and<br>*WAITB for more information. |

| *RI         | Ι    | 23              | Serial Port ring indicator.                                                                                                                                                                                                                                      |

| ROM8/*16    | Ι    | 80              | Strap pin option. Allowing selection of BIOS ROM width. When strapped low, BIOS ROM is 16 bits wide.                                                                                                                                                             |

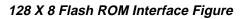

| *ROMCE[1:0] | Ο    | 21,20           | ROM chip enable outputs. *ROMCE0 is always<br>asserted for memory accesses to the BIOS ROM<br>(address range F000:0-FFFF:F). Assertion of ROM<br>chip enable outputs [1:0] for other address ranges<br>may be specified using the VG230's EMS<br>addressing.     |

| *RTS        | 0    | 41              | Serial Port request to send.                                                                                                                                                                                                                                     |

| RXD         | Ι    | 36              | Serial Port receive data.                                                                                                                                                                                                                                        |

| SCAN[7:0]   | I/O  | 81-88           | Scan outputs for external key matrix. The Keyboard<br>Mode Register (08H) also enables other definitions<br>for these pins. See KBCLK, KBDAT, *CE[2:1]B,<br>*REGB, PDCLKB, *PDCLKU, INIT and STB for<br>more information.                                        |

| SEL         | Ι    | 66              | Parallel port SEL input (when keyboard scanner<br>disabled by Keyboard Mode Register, 08H). The<br>default definition of this pin is RET6.                                                                                                                       |

| SHCLK       | 0    | 59              | Shift clock to LCD.                                                                                                                                                                                                                                              |

| SHFT[4:0]   | I/O  | 74-78           | Shift key return inputs from external key matrix.<br>The Keyboard Mode Register (08H) also enables<br>other definitions for these pins. See *CD[2:1]B,<br>BVD[2:1]B, *STSCHGB, *SPKRB and *INPACKB<br>for more information.                                      |

# CONNECTION AND PIN DESCRIPTIONS

| Symbol    | Туре | Pin Number | Description                                                                                                                                                                                                                                                                                                          |

|-----------|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *SIORD    | 0    | 15         | System I/O Read strobe. This output is used to<br>inform external I/O devices to put their data onto the<br>data bus. The VG230 may be programmed to inhibit<br>this output during I/O read cycles to the VG230<br>internal devices.                                                                                 |

| *SIOWR    | 0    | 14         | System I/O Write strobe. This output is used to<br>inform external I/O devices that data is available on<br>the data bus. The VG230 may be programmed to<br>inhibit this output during I/O write cycles to the<br>VG230 internal devices.                                                                            |

| SIOX[2:1] | XTL  | 44,45      | Serial Port crystal input/output.                                                                                                                                                                                                                                                                                    |

| SLCT      | 0    | 64         | Parallel port SLCT control output (when keyboard scanner disabled by Keyboard Mode Register, 08H). This output must be inverted using a 74XX05-type open collector device. The default definition of this pin is RET8.                                                                                               |

| *SMRD     | Ο    | 17         | System Memory Read strobe. This output is used to<br>inform external memory devices to put their data on<br>the data bus. *SMRD is not asserted during reads<br>from system RAM, ROM, or PC Cards.                                                                                                                   |

| *SMWR     | 0    | 16         | System Memory Write strobe. This output is used to<br>inform expansion memory devices that data is<br>available on the data bus. *SMWR is not asserted<br>during writes to system RAM, ROM, or PC Cards.                                                                                                             |

| SNEPWRGD  | I    | 31         | VG230 power good input. This pin should be driven<br>low when power to the VG230 falls below the<br>recommended operating thresholds. SNEPWRGD is<br>used to initialize the internal registers, peripherals,<br>RTC, and microprocessor of the VG230. It will also<br>generate a system reset on the *RESOUT output. |

| SPKR      | О    | 111        | Speaker data output. This output should be buffered<br>and then input to a low pass filter. The output of the<br>filter connects to a speaker.                                                                                                                                                                       |

# CONNECTION AND PIN DESCRIPTIONS

# VADEM VG230

| Symbol   | Туре | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                |

|----------|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *SPKRA   | Ι    | 106        | Speaker signal from slot 'A' PC I/O cards. Enabled<br>by the PC Card Slot 0 Control Register (21H). The<br>default definition of this pin is BVD2A.                                                                                                                                                                                                        |

| *SPKRB   | I    | 77         | Speaker signal from slot 'B' PC I/O cards (when<br>keyboard scanner disabled by Keyboard Mode<br>Register, 08H, and I/O mode enabled by PC Card<br>Slot 1 Control Register, 27H). When the keyboard<br>scanner is disabled, the default definition of this pin<br>is BVD2B. When the scanner is enabled, the<br>definition of this pin is SHFT1.           |

| STB      | 0    | 88         | Parallel port STB control output (when keyboard<br>scanner disabled by Keyboard Mode Register, 08H).<br>The default definition of this pin is SCAN0.                                                                                                                                                                                                       |

| *STSCHGA | Ι    | 105        | Status changed signal from slot 'A' PC I/O cards.<br>Enabled by the PC Card Slot 0 Control Register<br>(21H). The default definition of this pin is BVD1A.                                                                                                                                                                                                 |

| *STSCHGB | Ι    | 76         | Status changed signal from slot 'B' PC I/O cards<br>(when keyboard scanner disabled by Keyboard Mode<br>Register, 08H, and I/O mode enabled using PC Card<br>Slot 1 Control Register, 27H). When the keyboard<br>scanner is disabled, the default definition of this pin<br>is BVD1B. When the scanner is enabled, the<br>definition of this pin is SHFT2. |

| SYSCLK   | 0    | 50         | XT Bus Clock signal (when enabled by GPIO Mode<br>Register, 32H). Alternatively, LCDL2 for 400-line<br>LCD panels may be enabled by this register. The<br>default definition of this pin is GPIO2.                                                                                                                                                         |

| SYSPWRGD | Ι    | 30         | System Power Good input. This pin should be driven<br>low when the system VCC falls below the<br>recommended operating thresholds. SYSPWRGD is<br>used to initialize the external system peripherals, via<br>the *RESOUT signal, and re-start the internal<br>VG230 clocks.                                                                                |

# CONNECTION AND PIN DESCRIPTIONS

| Symbol | Туре | Pin Number | Description                                                                                                                                                                               |

|--------|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TC     | 0    | 13         | Terminal Count. Output from 8237A DMA<br>Controller Macro.                                                                                                                                |

| TEST   | Ι    | 43         | Test Mode.                                                                                                                                                                                |

| TXD    | 0    | 42         | Serial Port transmit data.                                                                                                                                                                |

| VPBIAS | 0    | 29         | BIAS power gate for LCD panel.                                                                                                                                                            |

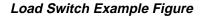

| VPCRD  | 0    | 26         | VCC power gate for PC Cards.                                                                                                                                                              |

| VPLCD  | 0    | 28         | VCC power gate for LCD panel.                                                                                                                                                             |

| VPPENA | 0    | 90         | Program Voltage Enable for slot 'A' PC Card.                                                                                                                                              |

| VPPENB | 0    | 62         | Program Voltage Enable output to power source for<br>slot 'B' PC Card (when keyboard scanner disabled<br>by Keyboard Mode Register, 08H). The default<br>definition of this pin is RET10. |

| VPRAM  | 0    | 89         | VCC power gate for RAM array.                                                                                                                                                             |

| VPSYS  | 0    | 27         | Main System power gate for system power supply.                                                                                                                                           |

| *WAITA | Ι    | 103        | Extend bus cycle for slot 'A' PC Cards.                                                                                                                                                   |

| *WAITB | I    | 73         | Wait status input from slot 'B' PC Card (when<br>keyboard scanner disabled by Keyboard Mode<br>Register, 08H). The default definition of this pin is<br>RET0.                             |

| WPA    | I    | 107        | Write protect input from slot 'A' PC memory cards.<br>PC Card Slot 0 Control Register (21H) may be used<br>to redefine this pin as *IOIS16A for I/O cards.                                |

| Symbol | Туре | Pin Number | Description                                                                                                                                                                                                                                                                            |

|--------|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WPB    | Ι    | 72         | Write protect status input from slot 'B' PC memory<br>Cards (when keyboard scanner disabled by Keyboard<br>Mode Register, 08H). PC Card Slot 1 Control<br>Register (27H) may be used to redefine this pin as<br>*IOIS16B for I/O cards. The default definition of<br>this pin is RET1. |

| X[2:1] | XTL  | 100,99     | Main clock crystal inputs. X1 is an input for a passive crystal circuit. X1 may be driven at either 32.215905 MHz or 28.63636 MHz. X2 is the inverted output of X1.                                                                                                                    |

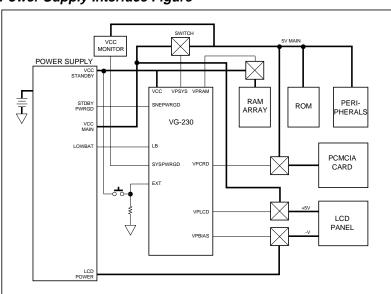

#### **OVERVIEW**

This section describes the main functional blocks of the VG230 Single-Chip PC Platform. The VG230 is designed for easy development of cost-sensitive, battery operated products which contain substantial amounts of ROM-based software. In addition to the functional blocks which support basic XT compatibility, also provided are a matrix keyboard scanner, a CGA/AT&T LCD controller, a sophisticated memory manager which is programmed using a compatible superset of LIM 4.0 registers, PCMCIA 2.1 controllers, an industry-proven power management unit, a system management unit to aid in integration of non-standard peripherals, a serial port and a parallel port. Standard V30H ICE support for faster debugging is also integrated.

#### SINGLE-BUS ARCHITECTURE

The VG230 Single-Chip PC Platform embodies a Single Bus Architecture (pat. pend.). All external memory and I/O devices share the same address bus and data bus. A control bus is reserved for interfacing Expansion Memory and Expansion I/O devices. Expansion in this case means memory or I/O devices not directly controlled by the VG230 Single-Chip PC Platform. The single bus architecture minimizes cost and power requirements while still providing high performance. The single bus architecture minimizes cost and power requirements while significantly boosting video performance.

The Address Bus operates in 5 modes depending upon the device type accessed. Logic internal to the VG230 Single-Chip PC Platform enables the appropriate addressing mechanism for the selected device. The addressing modes are in the VG230 Addressing Modes Table.

The Single Bus supports 8 or 16 bit memory, 8 bit I/O, 16 bit PC memory cards and 8 or 16 bit PC I/O cards. The data width of System RAM and System ROM are set by VG230 Single-Chip PC Platform register bits and a configuration pin. When 8-bit system RAM or 8-bit system ROM configurations are selected, these devices are installed on the lower half of the data bus, D[7:0].

| Device Type      | Address Format         | Address Type                      |

|------------------|------------------------|-----------------------------------|

| System RAM       |                        |                                   |

| DRAM             | Multiplexed Row/Column | Mappable RAM Memory Address       |

| SRAM/PSRAM       | Latched                | Mappable RAM Memory Address       |

| System ROM0      | Latched                | Mappable ROM0 Memory Address      |

| System ROM1      | Latched                | Mappable ROM1 Memory Address      |

| PC Memory Card 1 | Latched                | Mappable PC Card 1 Memory Address |

| PC Memory Card 2 | Latched                | Mappable PC Card 2 Memory Address |

VG230 Addressing Modes Table

#### PROCESSOR

The VG230 Single-Chip PC Platform is built around a standard, fully 8086-compatible NEC V30HL CPU macro. With its maximum clock rate of 16 MHz, the V30HL rivals all industry standard processors in speed. It is especially designed for low power consumption, and supports complete clock stoppage under power management. The V30HL is designed to operate over a range including +3V (reduces maximum clock rate to 8MHz) and +5V.

#### **Basic Peripherals and Core Logic**

The VG230 Single-Chip PC Platform contains the following PC Core logic and other peripherals:

- Serial Port

- Parallel Port

- Real Time Clock (RTC)

- Standard PC Core logic peripherals

- DMA Controller

- Interrupt Controller

- Timer

- Keyboard Interface

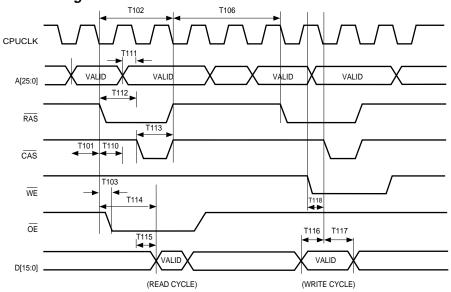

## **Bus Cycle Generator (BCG)**

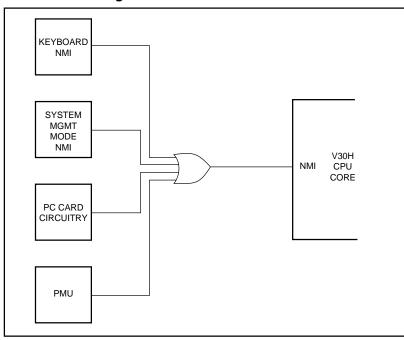

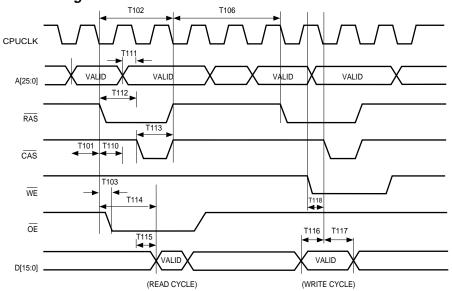

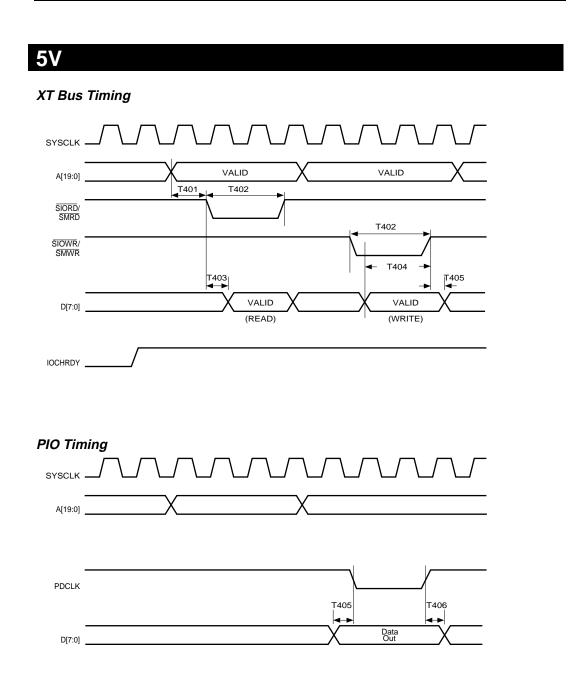

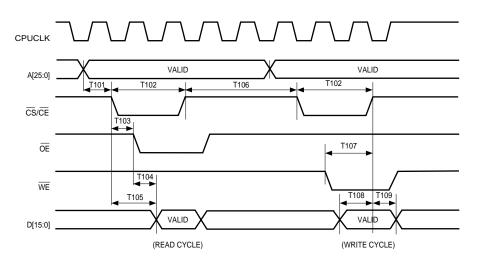

The Bus Cycle Generator (BCG) controls the system timing for all I/O and memory accesses. The BCG can be configured for various memory and I/O wait states through registers located in the VG230's configuration space.

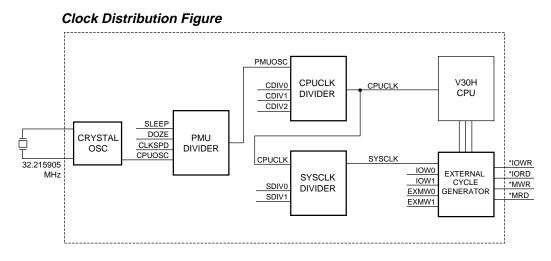

CPUOSC is the frequency of the crystal oscillator connected to the X1 and X2 pins. There are two possible frequencies at which the VG230 can run, 32.215905 MHz and 28.63636 MHz. CPUOSC is routed through the PMU to the CPUCLK divider. The PMU will divide the clock from 1 to 8 times depending on its state and the CLKSPD bit. PMUOSC is divided from 2 to 8 times to create CPUCLK. CPUCLK is used as the timebase for all VG230 controlled RAM and ROM accesses. SYSCLK is generated from CPUCLK and can equal CPUCLK or be divided 2, 3 or 4 times. SYSCLK is used for all I/O cycles and expansion memory cycles. The Clock Distribution Figure illustrates the clock divider circuitry in the VG230.

CPUCLK is derived from CPUOSC, and is configured through the BCG mode register at offset 01H. CDIV[2:0] select the divisor for CPUCLK. The default is CPUOSC/4.

CLK14/\*16 selects the CPUOSC frequency of 32.21 MHz or 28.63 MHz. This option configures the internal divider chain to provide a PC-compatible 1.19MHz timer clock.

The LTCHADR bit enables address latching for certain cycles. Latching of the address reduces switching on the external address bus. Reduced switching reduces the power consumption.

The BINH bit disables bus cycles for internal I/O accesses. This reduces activity on the external bus, thereby reducing power consumption.

SYSCLK is generated from CPUCLK and can equal CPUCLK or be divided 2, 3 or 4 times. SYSCLK is used for all I/O cycles and expansion memory cycles. The SDIV[1:0] bits control the generation of SYSCLK. Divisors of 1, 2, 3 and 4 are selectable. The default is CPUCLK/2.

The BCG Wait State Control 1 Register selects the number of wait states for the various I/O and memory subsystems. ROMW[1:0] control the number of wait states for ROMs connected to \*ROMCE0 and \*ROMCE1. RAMW[1:0] control the number of wait states for all RAM. IOW[1:0] control the number of SYSCLK wait states for all I/O cycles. EXMW[1:0] control the number of SYSCLK wait states for all expansion memory cycles. *For Register Description, see Index 02H*.

#### Clocks

The VG230 Single-Chip PC Platform requires three clock sources:

- Main clock 32.215905 MHz or 28.63636 MHz

- SIO clock 3.6864 MHz

Power Management Unit/

- RTC clock 32.768 KHz

The Main clock generates the processor clock (CPUCLK), the LCD Controller's clock (VIDCLK) and the Timer clock (TCLK). The RTC and PMU share the same time base, which is the only oscillator running when the VG230 Single-Chip PC Platform is in the SUSPEND or OFF Power Management modes.

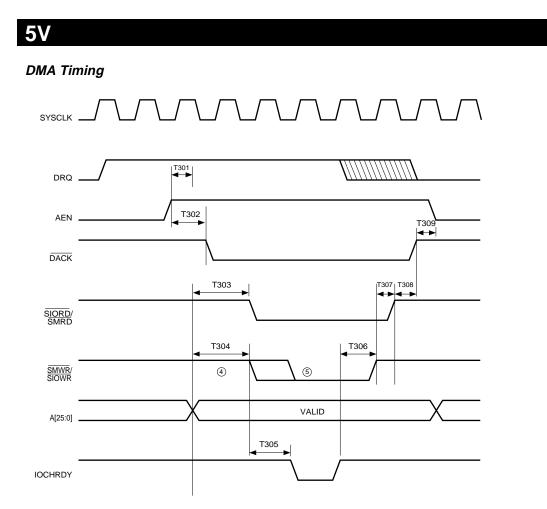

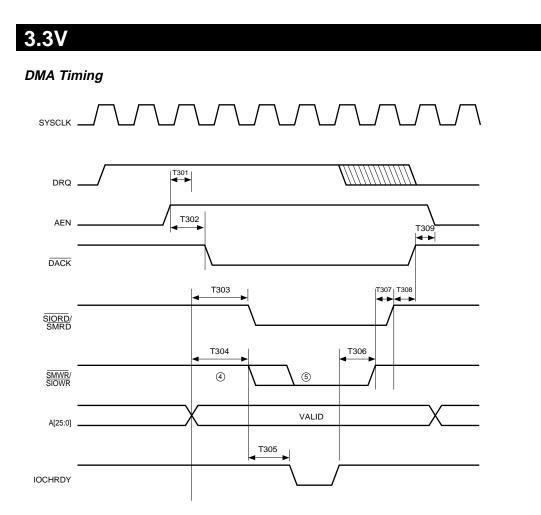

#### DMA

The VG230 provides two pins for DMA support. Because of pin limitations, only a single DMA channel is supported. The DMA pins, DRQ and \*DACK are configurable for DRQ/\*DACK[1:3]. Selection of the desired DMA channel is made through bits DRQS[1:0] in the DMA mode register located at index 0EH.

# **DMA Controller**

An 8237A PC/XT compatible DMA Controller is included. One DMA channel is provided for the external system bus. System software may configure this channel to be one of DRQ/\*DACK1, DRQ/\*DACK2 or DRQ/\*DACK3. Channel 0 (DRQ/\*DACK0) of the DMA controller is reserved by the VG230. When setting up refresh, Port 42H of the 8254 timer must be initialized before refresh will begin.

## Command Delay and DMA Clock Control

In some applications it may be desirable to delay the \*IOWR and \*MWR strobes during DMA. These strobes may be delayed from 0 to 3 SYSCLK cycles. Command delay is programmed through WDLY[1:0] in the DMA mode register.

To reduce current consumption, the VG230 has a provision to disable the internal 8237's clock during idle times. When the STPDCLK bit in the DMA mode register is cleared (0), the internal DMA clock always runs. When set, the clock is enabled only during DMA cycles.

# **General Purpose I/O Pins (GPIO)**

The VG230 provides up to 4 GPIO pins when 200 line or smaller LCD panels are used. The LCDL[3:0] pins are only used when 400 line panels are used. When configured for GPIO these pins can provide general purpose input or output bits which can be used to control peripherals or monitor status. Some examples of possible uses include:

- LCD backlight control

- Additional low battery monitoring

- LED indicator control

- Serial EEPROM interface

- FLASH EPROM programming voltage control

The GPIO is enabled through the GPIO mode register at index 32H. Each of the LCDL[3:0] pins can be individually programmed as LCDL bits, GPIO bits or one of the listed internal signals. The default configuration is GPIO configured as input.. Each pin must first be configured for GPIO through the GPIO mode register. Control of the state of the pins is through the GPIO control register at index 33H.

Also, the Parallel Port (available when the VG230's internal keyboard scanner is disabled) may be configured to appear at a non-standard address. This allows use of the port's pins by dedicated applications for general purpose input and general purpose output (GPI and GPO).

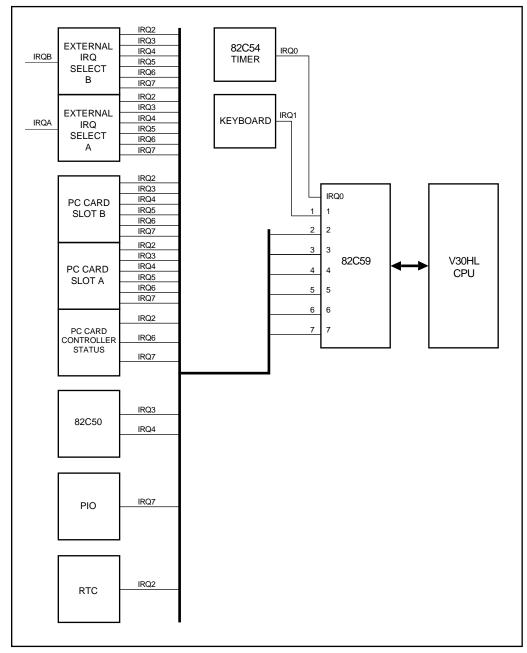

## **Interrupt Controller**

The Interrupt Controller is PC/XT compatible and based upon the 8259 PIC. The VG230 provides two external interrupt request inputs, IRQA and IRQB. System software may assign each of these lines to any of IRQ2 through IRQ7 using the ICU Mode Register (0DH).

The remaining interrupt lines are inputs internally assigned as follows:

- IRQ0 System Timer Interrupt

- IRQ1 Keyboard

- IRQ2 RTC Alarm

- IRQ3 SIO programmed to appear at 2F8H-2FFH

- IRQ4 SIO programmed to appear at 3F8H-3FFH

- IRQ7 Parallel Port

# Interrupts

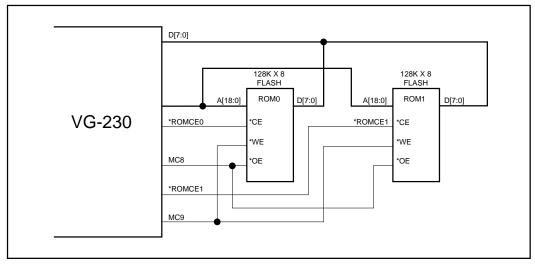

The VG230 has many sources of internal interrupts in addition to two external interrupt sources. The Internal Interrupt Configuration Figure illustrates the sources of the internal and external interrupts. The following table lists the internal interrupts and the control/status register associated with each.

| Source          | Levels (IRQ) | Control   | Status         |

|-----------------|--------------|-----------|----------------|

| Internal COM1   | 4            | 3F9       | 3FA            |

| Internal COM2   | 3            | 2F9       | 2FA            |

| Parallel Port   | 7            | 37A       | 379            |

| 82C54 Timer     | 0            | 20,21H    | 20H            |

| Keyboard        | 1            | 20,21H    | 20H            |

| IRQA            | 2-7          | Index 0DH | 20H            |

| IRQB            | 2-7          | Index 0DH | 20H            |

| PCCARD Status   | 2,6,7        | Index 20H | Index 22H, 28H |

| PCCARD A I/O    | 2-7          | Index 21  | 20H            |

| PCCARD B I/O    | 2-7          | Index 27H | 20H            |

| Real Time Clock | 2            | Index 79H | Index 7AH      |

Internal Interrupts and Their Control/Status Registers Table

## **FUNCTIONAL DESCRIPTION**

#### Internal Interrupt Configuration Figure

Two pins, IRQA and IRQB, provide support for the standard IRQ inputs. Each one of these inputs can support IRQ2-IRQ7. The selection of which IRQ input level is gated to the IRQA or IRQB inputs is controlled through the ICU mode register at index 0DH.

#### Keyboard

The VG230 Single-Chip PC Platform provides two types of Keyboard interfaces:

- Internal Keyboard Scanner to control switch matrix

- PC/XT serial keyboard interface to connect to a stand-alone PC/XT keyboard subsystem.

When the Keyboard Scanner is enabled, it supports an external key matrix composed of up to 101 keys. Of these keys, 96 are organized in an 8 x 12 matrix and 5 are dedicated shift keys. When the Keyboard Scanner is disabled, some of the pins it controls are assigned to other internal functions. These functions are the Parallel Port, the PC/XT serial Keyboard interface, and control for a second PC Card Slot. The PC/XT Serial Keyboard Interface itself may also be disabled, allowing use of a separate keyboard controller. In this mode the KBDAT pin is defined as IRQ1. *For Register Description, see Index 08H.*

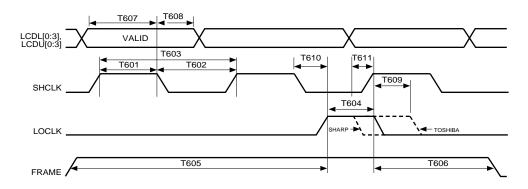

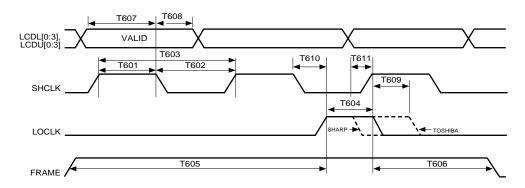

# LCD Controller

The LCD Controller supports all CGA Text and Graphics display modes as well as AT&T 640x400 two-color graphics mode. AT&T "double-scanning" of 200 line text and graphics is also supported. For lower-resolution panels, the controller provides hardware support for windowing into the CGA or AT&T frame. This allows software to utilize 200 or 400 line display modes regardless of panel size.

For 200 line panels or smaller, an Ink Plane feature useful for pen-based applications is supported. A separate 200 line buffer receives ink traces which are superimposed on the main display buffer.

The LCD Controller supports a global enable/disable function. While disabled, all clocks within the LCD Controller are stopped to reduce power consumption, and the LCD Controller will not respond to either I/O or memory operations, except accesses to the LCD Configuration Control Register.

The LCD Controller uses main system memory. This provides very high video performance and eliminates the need for a separate display memory. The uppermost bank of RAM is used as the display buffer. CPU accesses to B800:0H are mapped by the VG230 hardware to this bank. *For Register Description, see Index COH.*

| 640x400 | Sharp      | LM64060F           |

|---------|------------|--------------------|

|         | Optrex     | DMF666AN           |

|         | Hitachi    | LMG6111XTFR        |

| 640x200 | Casio      | MD232TS01-00       |

|         | Epson      | TCMA9108 9043D     |

|         | Hitachi    | LMG6273XNFR        |

|         | Matsushita | EDMDG648A 33D      |

|         | Sanyo      | LCM5205            |

| 640x100 | Hitachi    | LM266XW            |

| 480x128 | Toshiba    | TLX1241            |

| 320x200 | Epson      | EG7500B-LS         |

| 320x240 | Optrex     | DMF5008IN          |

|         | Sharp      | LM320081           |

| 240x128 | Optrex     | DMF66ON            |

|         | Sharp      | LM24009W, LM24010Z |

| 240x64  | Optrex     | LM24013W           |

|         | Sharp      | LM258XB            |

| 128x128 | Optrex     | DMF6116            |

| 128x64  | Optrex     | DMF697N            |

#### VG230 Examples of Supported LCDs Table

Note: For unlisted panels or sizes, please contact Vadem.

#### Memory Controller and Memory Manager

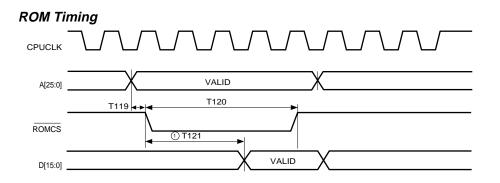

The VG230 supports DRAM, SRAM, PSRAM, ROM and FLASH memory devices. Timing for accesses to memory is based on the processor clock, CPUCLK.

In general, memory device types and sizes cannot be mixed. FLASH banks, however, can be installed above SRAM or PSRAM banks as long as data width and device sizes are consistent. The memory controller automatically allocates memory from the uppermost RAM bank for LCD video memory functions.

Memory management hardware is provided which facilitates the use of large ROMs, PCMCIA 2.1 (JEIDA 4.1) compatible cards, and expanded memory. As a compatible superset of LIM 4.0, its command set is easy to support. The memory manager is also compatible with the PCMCIA 2.1 LIM XIP ("execute-in-place") specification for applications which execute directly out of ROM.

- Over and above base memory, five categories of memory are addressable.

- Expanded memory (64MB address space).

- Heavy-access ROM (highly power efficient, 1MB address space limitation).

- Normal-access ROM (64MB address space).

- PCMCIA 2.1 Card A (64MB address space).

- PCMCIA 2.1 Card B (64MB address space).

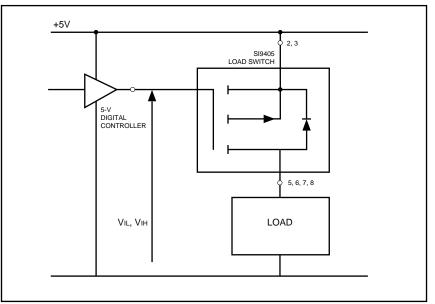

- Addressing is paged, via 26 mapping registers.

- Except for the non-mappable 32KB display memory (B800:0H-BFFF:FH), each 16KB "page" of the 1MB 8086 address space between 8000:0H and EFFF:FH is represented by its own mapping register.

- Each mapping register includes a memory type specifier, which determine what memory category (expanded memory, heavy-access ROM, normal-access ROM, PC Card A or PC Card B) is being mapped to its page.

- Mapping may be enabled/disabled globally, or on a page-by-page basis.

- Two ROM Chip Select outputs, \*ROMCE0 and \*ROMCE1, are available.

- \*ROMCE0 (heavy-access ROM) is always generated during BIOS ROM accesses (addresses F000:0H through FFFF:FH) and may also be generated during accesses to the ROM0 memory address space as specified in the Memory Mapping Registers.

- \*ROMCE1 (normal-access ROM) is an optional ROM Chip Select which may be used to implement ROM disks, ROMDOS, or embedded XIP applications.

| RAM Device Size    | 32K | <b>X X 8</b>             | 128  | Kx 8                     | 5121 | X x 8                    |

|--------------------|-----|--------------------------|------|--------------------------|------|--------------------------|

| Bus Bit Width      | 8   | <b>16</b> <sup>(1)</sup> | 8    | <b>16</b> <sup>(1)</sup> | 8    | <b>16</b> <sup>(1)</sup> |

| SRAM (bytes/bank)  | 32K | 64K                      | 128K | 256K                     | 512K | 1M                       |

| PSRAM (bytes/bank) | 32K | 64K                      |      |                          | 512K | 1M                       |

| PSRAM (bytes/bank) |     |                          | 128K | 256K                     |      |                          |

| Max #               |   |  |  |  |

|---------------------|---|--|--|--|

| RAM Banks           |   |  |  |  |

| 8 16 <sup>(1)</sup> |   |  |  |  |

| 8                   | 6 |  |  |  |

| 7                   | 6 |  |  |  |

| 6                   | 4 |  |  |  |

<sup>(1)</sup>Bus bit width of 16 utilizes two 8bit parts in parallel.

VG230 Memory Combinations Table

| DRAM Device Size                      | Bus Bit Width    |                   |  |  |  |

|---------------------------------------|------------------|-------------------|--|--|--|

|                                       | 8                | 16                |  |  |  |

| 256K x 1 (bytes/bank)                 | 256K             | 512K              |  |  |  |

|                                       | (8 devices wide) | (16 devices wide) |  |  |  |

| 256K x 4 (bytes/bank)                 | 512K             | 1M                |  |  |  |

| -                                     | (2 devices wide) | (4 devices wide)  |  |  |  |

| 512K x 8 (bytes/bank)                 | 512K             | 1M                |  |  |  |

|                                       | (1 device wide)  | (2 devices wide)  |  |  |  |

| 1M x 1 (bytes/bank)                   | 1 <b>M</b>       | 2M                |  |  |  |

|                                       | (8 devices wide) | (16 devices wide) |  |  |  |

| 1M x 4(bytes/bank)                    | 1M               | 2M                |  |  |  |

|                                       | (2 devices wide) | (4 devices wide)  |  |  |  |

| 4M x 1 (bytes/bank)                   | 4M               | 8M                |  |  |  |

| -                                     | (8 devices wide) | (16 devices wide) |  |  |  |

| 4M x 4 (bytes/bank)                   | 4M               | 8M                |  |  |  |

|                                       | (2 devices wide) | (4 devices wide)  |  |  |  |

| 256K x 16 (bytes/bank) <sup>(2)</sup> |                  | 512K              |  |  |  |

| -                                     |                  | (1 device)        |  |  |  |

| Max # |                  |  |  |  |  |  |

|-------|------------------|--|--|--|--|--|

| RAM   | RAM Banks        |  |  |  |  |  |

| 8     | 16               |  |  |  |  |  |

| 6     | 5                |  |  |  |  |  |

| 6     | 5                |  |  |  |  |  |

| 6     | 5                |  |  |  |  |  |

| 6     | 5                |  |  |  |  |  |

| 6     | 5                |  |  |  |  |  |

| 6     | 5                |  |  |  |  |  |

| 6     | 5                |  |  |  |  |  |

|       | 6 <sup>(2)</sup> |  |  |  |  |  |

<sup>(2)</sup>Extra bank with x16 DRAM.

**NOTE:** The above table describes RAM that is directly supported by the VG230. External logic can be used to utilize the full 64Mbyte of address space.

Software may open a window into any of the five VG230 memory categories using Memory Mapping Registers. Each Mapping Register controls a 16 Kbyte page in the 1MB memory address space which is directly addressed by the 8086-compatible V30 CPU (see diagram on next page). Memory Mapping Registers may also be disabled. In this case, the 16KB page controlled by the Register directly addresses the standard 1MB V30/8086 memory address space.

Each Memory Mapping Register pair is composed of 16 bits. Of these, 12 bits define the offset into the memory space and are used to generate the memory address on the A25 - A14 lines, 3 bits define which of the five memory spaces will be accessed, and 1 bit acts as a page map enable/disable.

Accessing the VG230 Memory Mapping Registers involves three bytes in the CPU I/O address space. A particular Memory Mapping Register is accessed by first writing its CPU segment address into the Map Address Register at I/O address 06CH, and then reading from or writing to the Map Low Byte Data Register at I/O address 06EH or the Map High Byte Data Register at I/O address 06FH.

# VADEM VG230

| 101                     | Loo memory map rigare      |   |

|-------------------------|----------------------------|---|

| FFFF:FH<br>F000:0H      | ROM BIOS                   |   |

| EFFF:FH                 |                            |   |

|                         | Mapping Registers 23-26    |   |

| E000:0H                 |                            |   |

| DFFF:FH                 | Mapping Registers 19-22    |   |

| D000:0H                 |                            |   |

| CFFF:FH                 |                            |   |

|                         | Mapping Registers 15-18    |   |

| C000:0H                 |                            |   |

| BFFF:FH                 |                            |   |

|                         | CGA Buffer                 |   |

| B800:0H                 |                            |   |

| B7FF:FH                 |                            |   |

| 2,11,111                | Mapping Registers 13-14    |   |

| B000:0H                 | in apping registers to the |   |

| AFFF:FH                 |                            |   |

|                         | Mapping Registers 9-12     |   |

| A000:0H                 |                            |   |

| 9FFF:FH                 |                            |   |

| <i>J</i> <b>1111111</b> | Mapping Registers 5-8      |   |

| 9000:0H                 | mupping registers 5 0      |   |

| 8FFF:FH                 |                            |   |

| 0111.111                | Mapping Registers 1-4      |   |

| 8000:0H                 | Mapping Registers 1 4      |   |

| 7FFF:FH                 |                            |   |

| /111.111                |                            |   |

| I                       |                            | I |

|                         | Reserved for System RAM    |   |

|                         | 512K                       |   |

| 0000:0H                 |                            | ] |

|                         |                            |   |

#### VG230 Memory Map Figure

Defined as system RAM when Global EMS enable bit (MAPEN) at index 04H is zero.

|                     |                                                                                                                                                                                                                                                                                                                                                      | DRAM  |         | SR   | AM   | PSRAM              |      |        |       |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|------|------|--------------------|------|--------|-------|--|

|                     |                                                                                                                                                                                                                                                                                                                                                      |       |         |      |      | 32Kx8 or<br>512Kx8 |      | 128Kx8 |       |  |

|                     | 8                                                                                                                                                                                                                                                                                                                                                    | 16    | 256Kx16 | 8    | 16   | 8                  | 16   | 8      | 16    |  |

| *MC0                | *CAS0                                                                                                                                                                                                                                                                                                                                                | *CAS0 | *RAS0   | *CS0 | *CS0 | *CS0               | *CS0 | *CS0   | *CS0  |  |

| *MC1                | *CAS1                                                                                                                                                                                                                                                                                                                                                | *CAS1 | *RAS1   | *CS1 | *CS1 | *CS1               | *CS1 | *CS1   | *CS1  |  |

| *MC2                | *CAS2                                                                                                                                                                                                                                                                                                                                                | *CAS2 | *RAS2   | *CS2 | *CS2 | *CS2               | *CS2 | *CS2   | *CS2  |  |

| *MC3                | *CAS3                                                                                                                                                                                                                                                                                                                                                | *CAS3 | *RAS3   | *CS3 | *CS3 | *CS3               | *CS3 | *CS3   | *CS3  |  |

| *MC4                | *CAS4                                                                                                                                                                                                                                                                                                                                                | *CAS4 | *RAS4   | *CS4 | *CS4 | *CS4               | *CS4 | *CS4   | *REFL |  |

| *MC5                | *CAS5                                                                                                                                                                                                                                                                                                                                                | *RASL | *RAS5   | *CS5 | *CS5 | *CS5               | *CS5 | *CS5   | *REFH |  |

| *MC6                | *RASL                                                                                                                                                                                                                                                                                                                                                | *RASH | *CASL   | *CS6 | *OEL | *CS6               | *OEL | *REFL  | *OEL  |  |

| *MC7                | *RASH                                                                                                                                                                                                                                                                                                                                                | *OE   | *CASH   | *CS7 | *OEH | *OEL               | *OEH | *REFH  | *OEH  |  |

| *MC8                | *OE                                                                                                                                                                                                                                                                                                                                                  | *WEL  | *OE     | *OE  | *WEL | *OEH               | *WEL | *OE    | *WEL  |  |

| *MC9                | *WEL                                                                                                                                                                                                                                                                                                                                                 | *WEH  | WE      | *WE  | *WEH | *WE                | *WEH | *WE    | *WEH  |  |

| arrays, a<br>*WEL a | <i>Notes:</i> *RASH, *OEH and *WEH are asserted during Odd Byte and Word accesses for 16 bit RAM arrays, or during accesses to Odd numbered banks (1,3,5) for 8 bit RAM arrays. *RASL, *OEL, and *WEL are asserted during Even Byte and Word accesses for 16 bit RAM arrays, or during accesses to Even numbered banks (0,2,4) for 8 bit RAM arrays. |       |         |      |      |                    |      |        |       |  |

# System RAM Control Outputs Table

For PC memory cards, MC8 is defined as \*OE and MC9 as \*WE.

# VADEM VG230

# DRAM Address Muxing Table 8 BIT BUS

|         | 25 | 6K 512K 1M 4N |    | 512K 1M |    | M  |    |    |

|---------|----|---------------|----|---------|----|----|----|----|

| ADDRESS | R  | С             | R  | C       | R  | C  | R  | С  |

| 0       | 0  | 9             | 0  | 9       | 0  | 9  | 0  | 9  |

| 1       | 1  | 10            | 1  | 10      | 1  | 10 | 1  | 10 |

| 2       | 2  | 11            | 2  | 11      | 2  | 11 | 2  | 11 |

| 3       | 3  | 12            | 3  | 12      | 3  | 12 | 3  | 12 |

| 4       | 4  | 13            | 4  | 13      | 4  | 13 | 4  | 13 |

| 5       | 5  | 14            | 5  | 14      | 5  | 14 | 5  | 14 |

| 6       | 6  | 15            | 6  | 15      | 6  | 15 | 6  | 15 |

| 7       | 7  | 16            | 7  | 16      | 7  | 16 | 7  | 16 |

| 8       | 8  | 17            | 8  | 17      | 8  | 17 | 8  | 17 |

| 9       |    |               | 18 | Х       | 18 | 19 | 18 | 19 |

| 10      |    |               |    |         |    |    | 20 | 21 |

#### DRAM Address Muxing Table 16 BIT BUS

|         | 25 | 6K | 512K |    | 1M |    | <b>4M</b> |    |

|---------|----|----|------|----|----|----|-----------|----|

| ADDRESS | R  | C  | R    | C  | R  | C  | R         | C  |

| 0       | 1  | 10 | 1    | 10 | 1  | 10 | 1         | 10 |

| 1       | 2  | 11 | 2    | 11 | 2  | 11 | 2         | 11 |

| 2       | 3  | 12 | 3    | 12 | 3  | 12 | 3         | 12 |

| 3       | 4  | 13 | 4    | 13 | 4  | 13 | 4         | 13 |

| 4       | 5  | 14 | 5    | 14 | 5  | 14 | 5         | 14 |

| 5       | 6  | 15 | 6    | 15 | 6  | 15 | 6         | 15 |

| 6       | 7  | 16 | 7    | 16 | 7  | 16 | 7         | 16 |

| 7       | 8  | 17 | 8    | 17 | 8  | 17 | 8         | 17 |

| 8       | 9  | 18 | 9    | 18 | 9  | 18 | 9         | 18 |

| 9       |    |    | 19   | Х  | 19 | 20 | 19        | 20 |

| 10      |    |    |      |    |    |    | 21        | 22 |

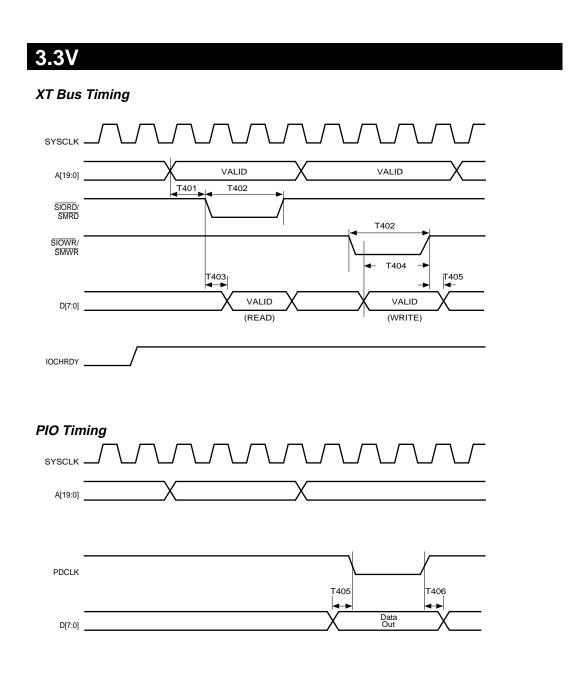

#### **Parallel Port**

The Parallel Port is PC/XT compatible and is only enabled when the Keyboard Scanner is disabled. An external 74XX374 is required for latching parallel data. The parallel port is also software configurable to appear at LPT1, LPT2 or LPT3 and supports the standard PC/XT PIO interrupt (IRQ7). Optionally, the parallel port may be configured for full 8 bit bidirectional capability with the addition of external components.

The Parallel Port may be similarly configured to appear at a non-standard I/O address. This allows use of the port's pins by dedicated applications for general purpose input and general purpose output (GPI and GPO).

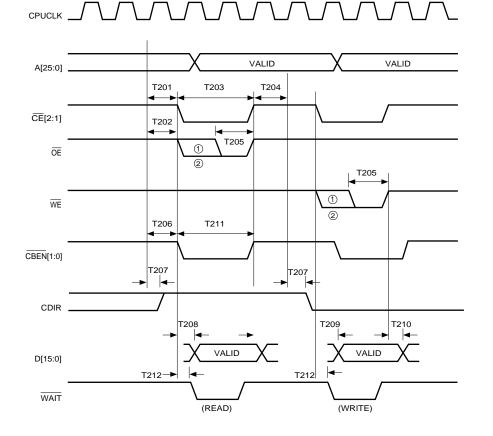

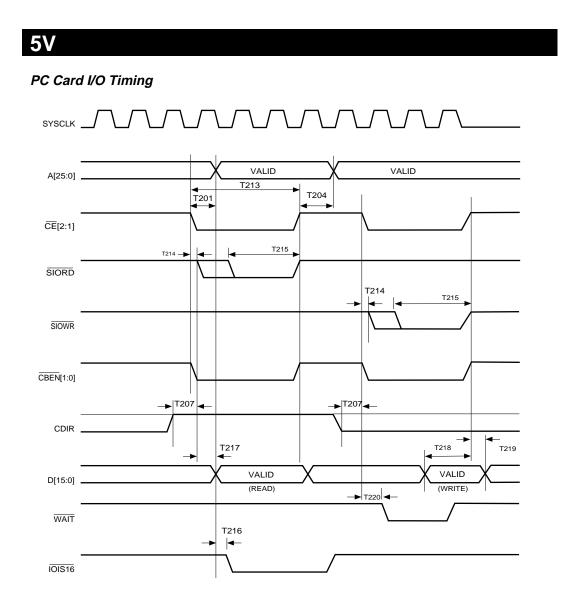

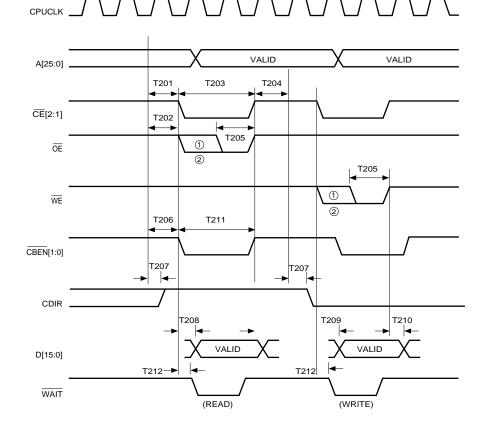

## PC Card Controller

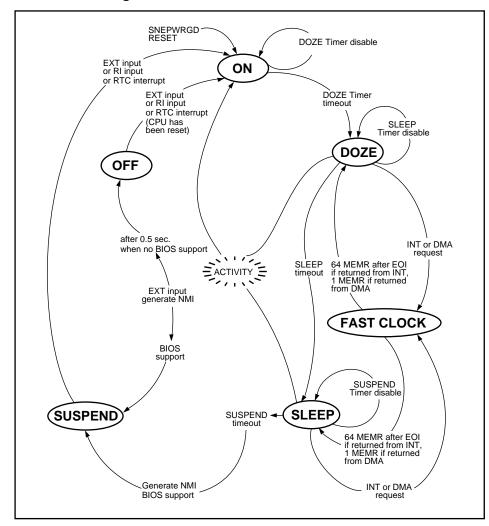

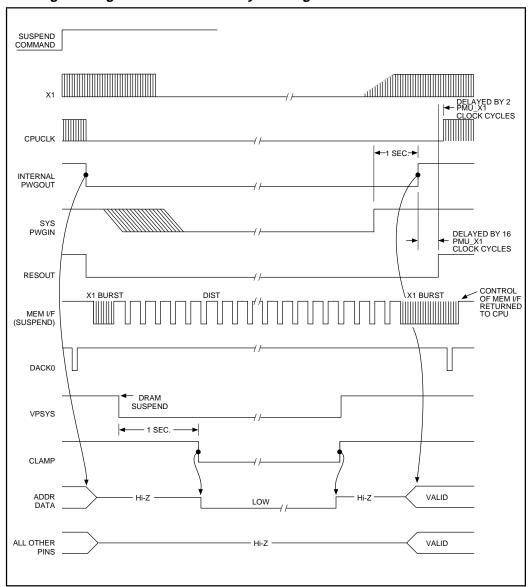

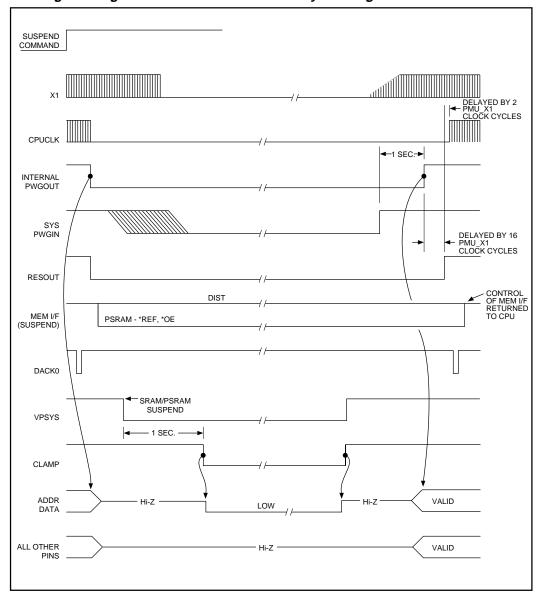

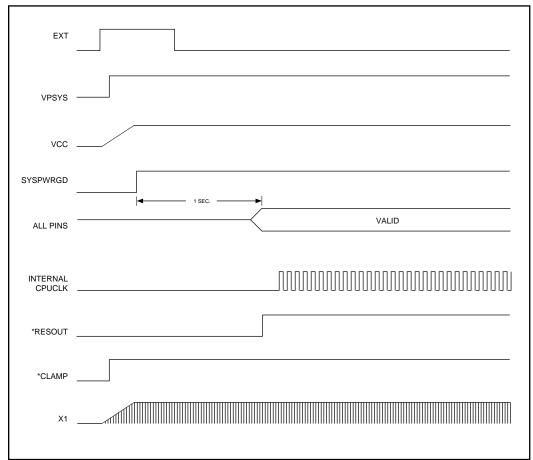

The VG230 Single-Chip PC Platform PC Card Controller provides support for up to two PCMCIA 2.1 (JEIDA 4.1) card slots. Both I/O and memory cards are supported, as is the memory-saving XIP ('execute-in-place') standard. A single PC Card slot is always supported by the VG230. A second PC Card slot is supported when the internal Keyboard Scanner is disabled.