**VG330**

**Single-Chip Platform**

**Data Manual**

**Preliminary**

1960 Zanker Road San Jose, CA 95112 Tel: 408.467.2100 Fax: 408.467.2199

# VG330 Single-Chip Platform Data Manual Document No. DM330001-02

#### Copyright 1996-97 Vadem All Rights Reserved

Information furnished by Vadem is believed to be accurate and reliable. However, no responsibility is assumed by Vadem for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Vadem. Vadem reserves the right to change specifications at any time without notice.

Trademarks mentioned herein belong to their respective companies.

#### **Medical Disclaimer**

Vadem's products are not authorized for use in life support devices or systems or in any medical applications and cannot be used in such applications without the written consent of the President of Vadem.

## **VG330 Data Manual Table of Contents**

|   | List of Figures                                   | . XIII |

|---|---------------------------------------------------|--------|

|   | List of Tables                                    | . XV   |

| 1 | Introduction                                      |        |

|   | General Description                               | .1-1   |

|   | Processor Capabilities                            |        |

|   | Key Features                                      |        |

|   | Architectural Overview                            |        |

|   | Single-Bus Architecture                           |        |

|   | Main Modules                                      |        |

|   | Programmer's Model                                |        |

| 2 | Pins and Signals                                  |        |

|   | Introduction                                      | 2-1    |

|   | Capabilities                                      |        |

|   | Pinout Diagram                                    |        |

|   | Pin Assignments - Summary as Alphabetical Listing |        |

|   | Pin Descriptions                                  |        |

|   | Additional Signals                                |        |

| 3 | Electrical Specifications                         |        |

|   | Maximum Ratings                                   |        |

|   | Recommended Operating Conditions                  |        |

|   | Thermal Characteristics                           |        |

|   | Power                                             |        |

|   | DC Electrical Characteristics                     |        |

|   | Timing                                            |        |

|   | Clock Timing                                      |        |

|   | DRAM Read/Write Timing                            |        |

|   | DRAM Refresh Timing                               |        |

|   | DRAM Video Page Mode Read Timing                  |        |

|   | PSRAM /SRAM CPU Read/Write Timing                 |        |

|   | PSRAM Video Read Timing                           |        |

|   | PSRAM Refresh Timing                              |        |

|   | ROM/FLASH Timing                                  |        |

|   | ISA Timing                                        |        |

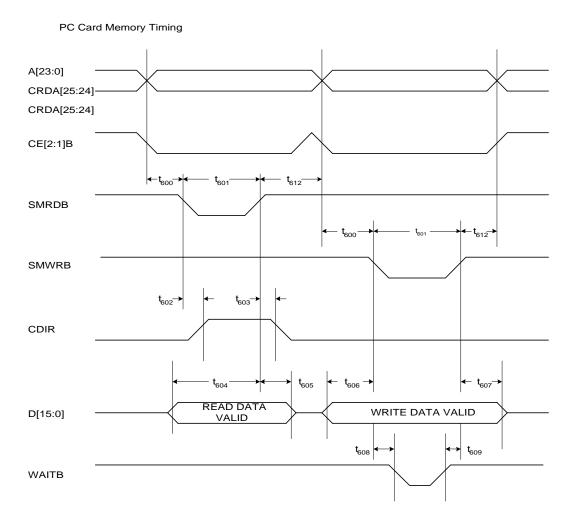

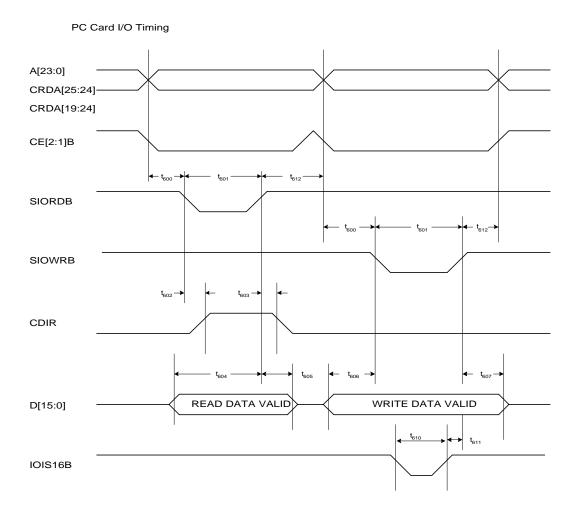

|   | PC Card Timing                                    |        |

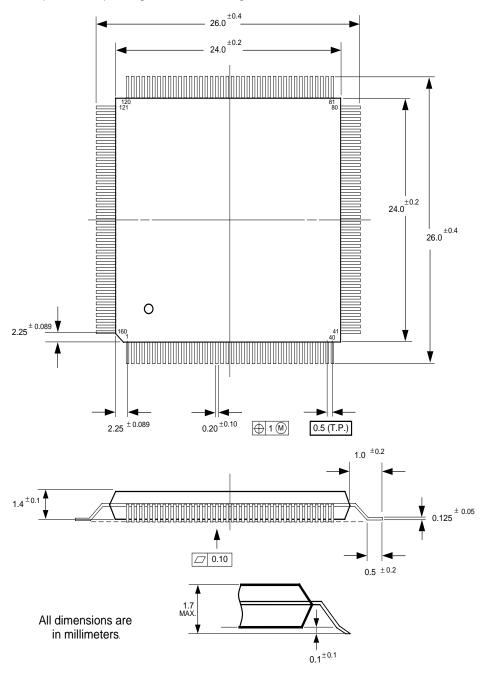

| 4 | Mechanical Data                                   |        |

|   | Package Dimensions                                |        |

|   | Ordering Information                              | 4-2    |

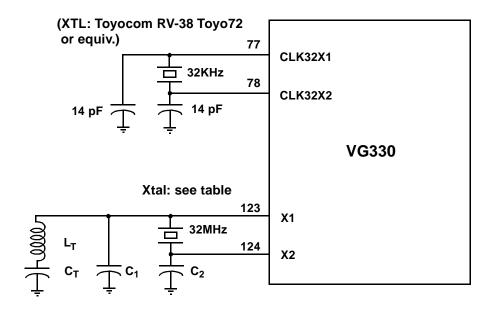

| 5 | System Clocks                                     |        |

|   | Introduction                                      | .5-1   |

|   | Capabilities                                           | . 5-1 |

|---|--------------------------------------------------------|-------|

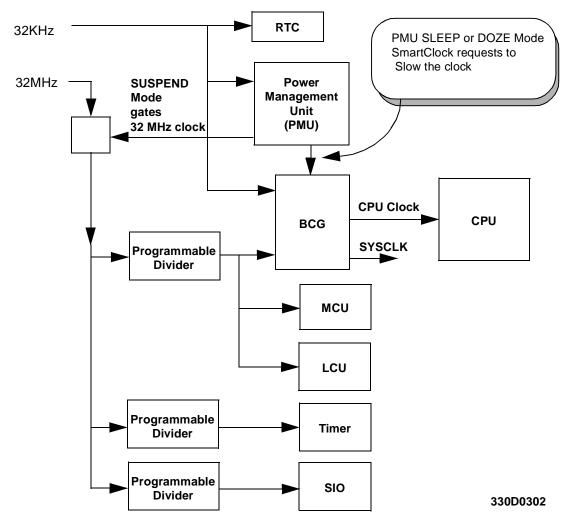

|   | Clocks                                                 | . 5-2 |

|   | Related Pins                                           | . 5-2 |

|   | High Frequency Clock                                   | . 5-3 |

|   | Low Frequency Clock                                    | . 5-3 |

|   | 32 KHz Crystal Parameters                              |       |

|   | Clocks and Power Management States                     |       |

|   | Processor Clock Handling                               |       |

|   | Clock Usage By Function Block                          |       |

|   | Related Registers                                      |       |

|   | Introduction                                           |       |

| 6 | Bus Architecture                                       |       |

|   | Capabilities                                           | 6-1   |

|   | System Memory Organization                             |       |

|   | Bus Architecture                                       |       |

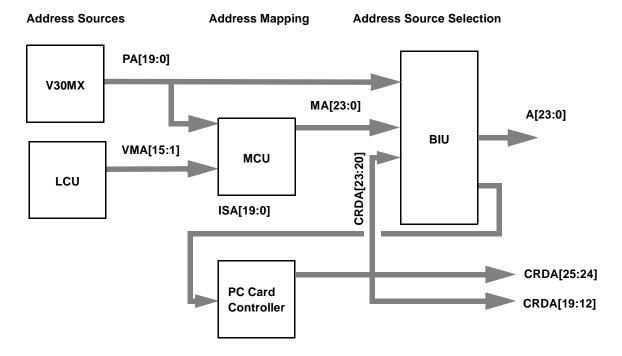

|   | Address Bus Control                                    |       |

|   | Addressing Architecture                                |       |

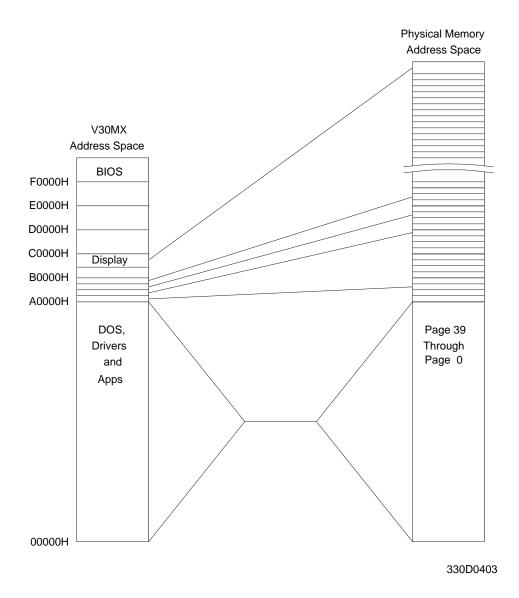

|   | Memory Address Mapping                                 |       |

|   | LIM 4.0 EMS Mapping                                    |       |

|   |                                                        |       |

|   | BIOS ROM Mapping for ROMCEO Cycles                     |       |

|   | Shadow BIOS Memory Mapping                             |       |

|   | Address Generation for DRAM                            |       |

|   | High Address Bits Handling Option                      |       |

|   | Display Buffer Memory Mapping                          |       |

|   | Display Buffer Mapping for Small Memory Configurations |       |

|   | LCD Controller Unit Display Refresh Addressing         |       |

|   | PC Card Memory Mapping                                 |       |

|   | V30MX I/O Addressing                                   |       |

|   | Data Bus Control                                       |       |

|   | Data Bus Sizing                                        |       |

|   | Data Width                                             |       |

|   | Control Signals                                        |       |

|   | RAM and ROM Control                                    |       |

|   | ISA Bus Signals                                        |       |

|   | PC Card Control                                        |       |

|   | Bus-Related Power Saving Features                      |       |

|   | General Bus Activity Control Options                   |       |

|   | Bus Inhibit Mode                                       |       |

|   | Bus Latching Mode                                      |       |

|   | Data Bus Activity Control Options                      |       |

|   | Data Hold and Clamping                                 |       |

|   | Related Registers                                      | 6-12  |

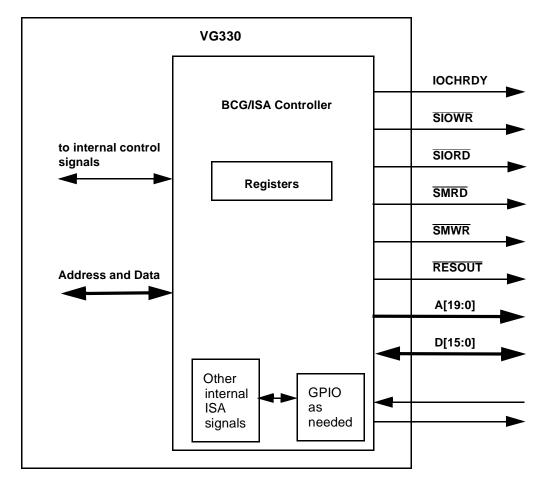

| 7 | ISA Bus Interface                                      |       |

|   | Introduction                                           | 7-1   |

|   | ISA Support                                            |       |

|   | Architecture                                           |       |

|   | ISA Bus Pins and Signals                               |       |

|   | ISA Signals Provided Through Dedicated Pins            |       |

|   | ISA Signals Available Through GPIO Pins                |       |

|   | - 0                                                    |       |

|   | ISA Signals Not Supported by the VG330                   |               |

|---|----------------------------------------------------------|---------------|

|   | System Design Considerations                             |               |

|   | RAM and ROM                                              | 7-6           |

|   | PC Memory Cards                                          |               |

|   | Expansion bus I/O and Memory                             |               |

|   | Interfacing ISA Peripherals to the VG330                 |               |

|   | ISA Cycle Control                                        |               |

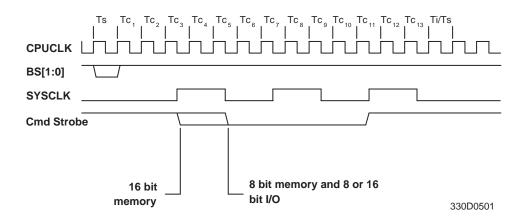

|   | SYSCLK Generation                                        |               |

|   | Divider Settings for SYSCLK                              |               |

|   | Selecting Clocking Mode                                  |               |

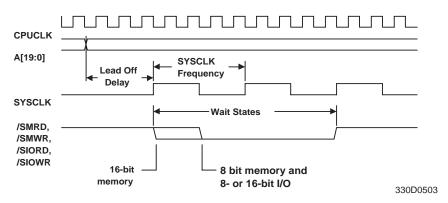

|   | ISA Timing Options                                       |               |

|   | Lead Off Delay                                           |               |

|   | SYSCLK Frequency                                         |               |

|   | Wait States                                              |               |

|   | Related Registers                                        | 7-12          |

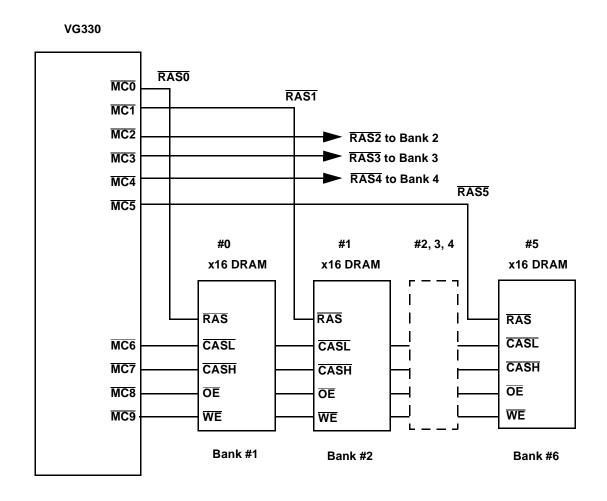

| 8 | Memory Controller Unit                                   |               |

|   | Introduction                                             | 8-1           |

|   | Capabilities Summarized                                  |               |

|   | MCU Architecture                                         |               |

|   | Related Pins                                             |               |

|   | Memory Controller Pin Mapping                            |               |

|   | Memory Type Support                                      |               |

|   | DRAM Support                                             |               |

|   | SRAM/PSRAM support                                       |               |

|   | ROM Support                                              |               |

|   | Flash ROM Support                                        |               |

|   | Shadow BIOS Support                                      |               |

|   | Memory Controller Functional Description                 |               |

|   | Mapping Registers                                        |               |

|   | Upper Address Pin Configuration                          |               |

|   | CPU Read/Write Cycles                                    |               |

|   | Wait States                                              |               |

|   | Flash Cycles                                             |               |

|   | BIOS ROM Cycles                                          |               |

|   | Refresh Cycles                                           | 8-8           |

|   | Enabling and Selecting Refresh Period                    |               |

|   | DRAM Refresh Cycles                                      |               |

|   | PSRAM Refresh Cycles                                     |               |

|   | SUSPEND Mode Refresh Cycles                              |               |

|   | Staggered Cycles and Power Buses                         |               |

|   | Shadow RAM Usage                                         |               |

|   | Display Memory                                           |               |

|   | Effects of RAM Refresh Cycles on Display Refresh         |               |

|   | Related RegistersInitialization, Setup, and Dependencies | 0-10          |

|   | Design Example                                           |               |

|   |                                                          | 0 <b>-</b> 11 |

| 9 | LCD Controller Unit                                      |               |

|   | Introduction                                             |               |

|   | Capabilities Summarized                                  | 9-1           |

|       | Architecture                                          |      |

|-------|-------------------------------------------------------|------|

|       | Related Pins                                          |      |

|       | LCU Control Registers                                 |      |

|       | Memory Assignment                                     |      |

|       | LCD Panel Interface Timing                            | 9-4  |

|       | Clock Prescaler                                       | 9-4  |

|       | LCD Power Control                                     | 9-4  |

|       | Related Registers                                     | 9-4  |

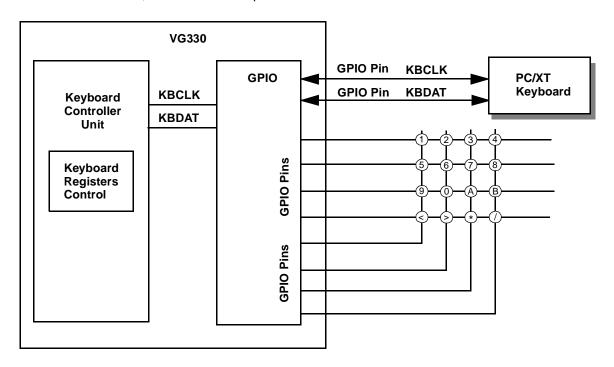

| 10    | Keyboard Controller Unit                              |      |

|       | Introduction1                                         | ı∩₌1 |

|       | Capabilities                                          |      |

|       | Types of Keyboards Supported                          |      |

|       | Types of Keyboard Interfaces Supported                |      |

|       | Keyboard Controller Unit Architecture                 |      |

|       | Related Pins and Signals                              |      |

|       | PC/XT Serial Keyboard Interfacing                     |      |

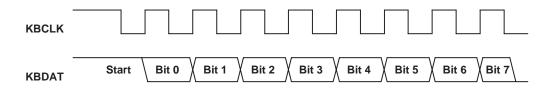

|       | Serial Keyboard Protocol                              |      |

|       |                                                       |      |

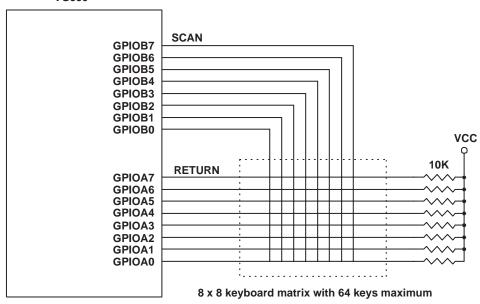

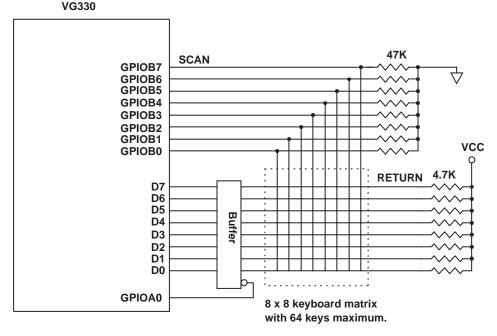

|       | Scanned Matrix Keyboard Interfacing                   |      |

|       | Full Scan Theory of Operation                         |      |

|       | Selecting the KCU's Full Scan Mode                    |      |

|       | SCAN and RETURN Signals and the GPIO                  |      |

|       | Matrix Partial Scan Operation                         |      |

|       | Partial Scan Hardware Configuration                   |      |

|       | Partial Scan Theory of Operation                      |      |

|       | Configuring KCU for Partial Scan Mode                 |      |

|       | Related Registers                                     | )-10 |

| 11    | Serial I/O                                            |      |

| • • • | Serial I/O                                            |      |

|       | Introduction1                                         | 1-1  |

|       | Capabilities 1                                        | 1-1  |

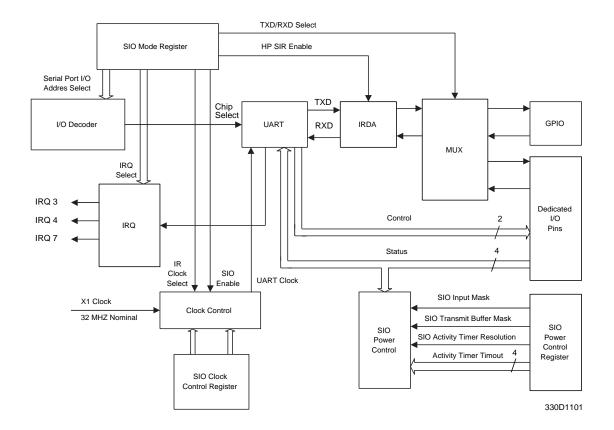

|       | SIO Architecture                                      | 1-2  |

|       | Related Pins 1                                        | 1-2  |

|       | SIO Addressing and Interrupts 1                       | 1-3  |

|       | Addressing 1                                          |      |

|       | Interrupts 1                                          |      |

|       | General Operation Discussion                          |      |

|       | Processing Options 1                                  |      |

|       | HP-IR Processing                                      |      |

|       | Standard Serial Processing 1                          |      |

|       | Routing Options 1                                     |      |

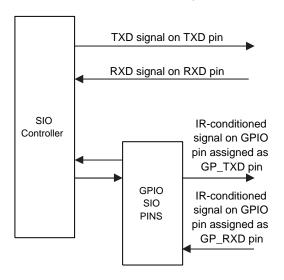

|       | Standard Serial I/O Operation                         |      |

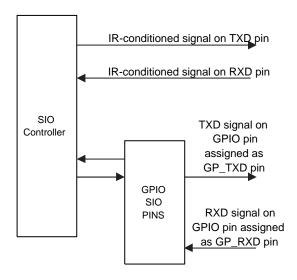

|       | IR-Conditioned Serial I/O                             |      |

|       | Using Both Standard Serial I/O and IR-Conditioned I/O |      |

|       | Additional configurations                             |      |

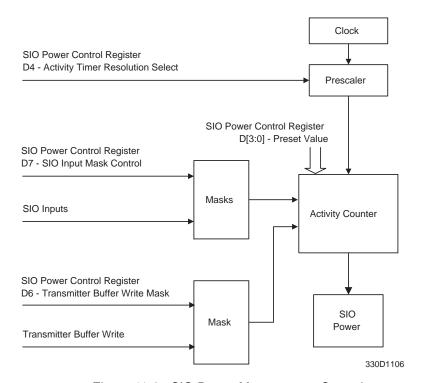

|       | Power Management of SIO                               |      |

|       | Powering SIO ON/OFF                                   |      |

|       | Activity-Based Power Control of SIO1                  |      |

|       | Related Registers                                     |      |

|       | Totalog Toglotoro                                     |      |

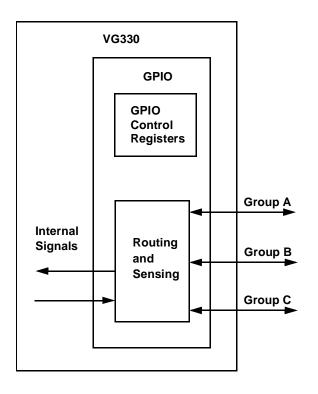

| 12    | GPIO                                                  |      |

|    | Introduction                             | .12-1 |

|----|------------------------------------------|-------|

|    | Capabilities                             | 12-1  |

|    | GPIO Architecture                        | 12-2  |

|    | Functions Available Through GPIO Pins    | 12-2  |

|    | General-Purpose Input and Output         | 12-2  |

|    | Routing of Internal Signals Through GPIO |       |

|    | LB2 Signal Available Through GPIO        |       |

|    | Related Pins                             |       |

|    | Programmable Chip Selects                |       |

|    | I/O Decoding                             |       |

|    | Memory Decoding                          |       |

|    | Data Width Selection 12-4                |       |

|    | Address Range Selection                  | 12-4  |

|    | Type Definition                          |       |

|    | Interrupts and the GPIO Pins             |       |

|    | ·                                        |       |

|    | 16 bit ISA Bus Support                   |       |

|    | Power Management and the GPIO Pins       |       |

|    | Keyboard Functions and GPIO              |       |

|    | Keyboard Interface                       |       |

|    | Serial Infrared Interface and GPIO       |       |

|    | PC Card Buffering                        |       |

|    | Related Registers                        | 12-8  |

| 13 | PC Card/ExCA Controller                  |       |

|    |                                          |       |

|    | Introduction                             |       |

|    | Capabilities                             |       |

|    | PC Card Controller Architecture          |       |

|    | Related Pins                             |       |

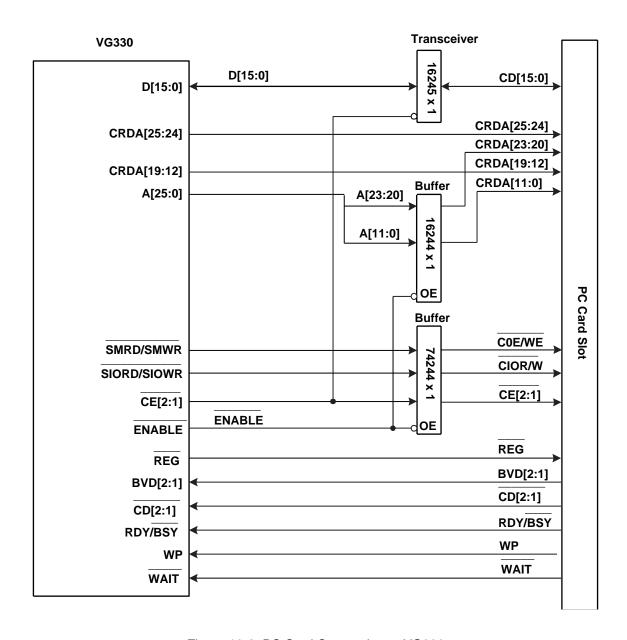

|    | Address, Data, and Command Buffering     | 13-4  |

|    | Address and Data Handling                | .13-4 |

|    | Command Signal Handling                  | 13-4  |

|    | PC Card Memory Mapping                   | 13-4  |

|    | Related Registers                        | 13-6  |

| 14 | Power Management Unit                    |       |

|    | . one management one                     |       |

|    | Introduction                             | .14-1 |

|    | Main Capabilities of PMU                 |       |

|    | PMU Overview                             |       |

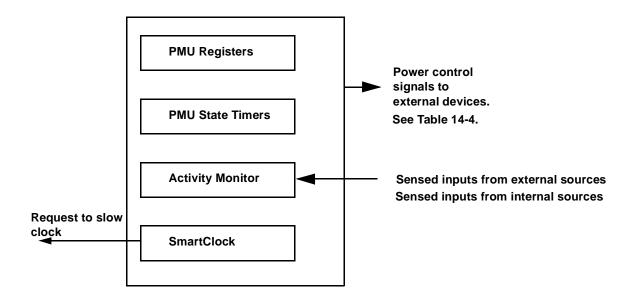

|    | PMU Main Functional Elements             |       |

|    | PMU Registers                            | 14-2  |

|    | State Timers                             | 14-2  |

|    | Activity Monitor                         | 14-2  |

|    | SmartClock                               | 14-2  |

|    | Related Pins                             | 14-3  |

|    | PMU Operating Environment                |       |

|    | PMU Connectivities                       |       |

|    | Activities Monitorable by the PMU        |       |

|    | Monitor for System Activities            |       |

|    | Control Inputs Monitored by PMU          |       |

|    | External Input (EXT)                     |       |

|    | Modem Ring Indicator Input (RI)          |       |

|    | woden ring maleator input (III)          | 10    |

|    | Power Supply Interface Input Pins       |       |

|----|-----------------------------------------|-------|

|    | SYSPWG                                  |       |

|    | Battery Status Monitoring               | 14-7  |

|    | RSTIN Pin                               | 14-7  |

|    | LB1 Pin and LB2 Signal                  |       |

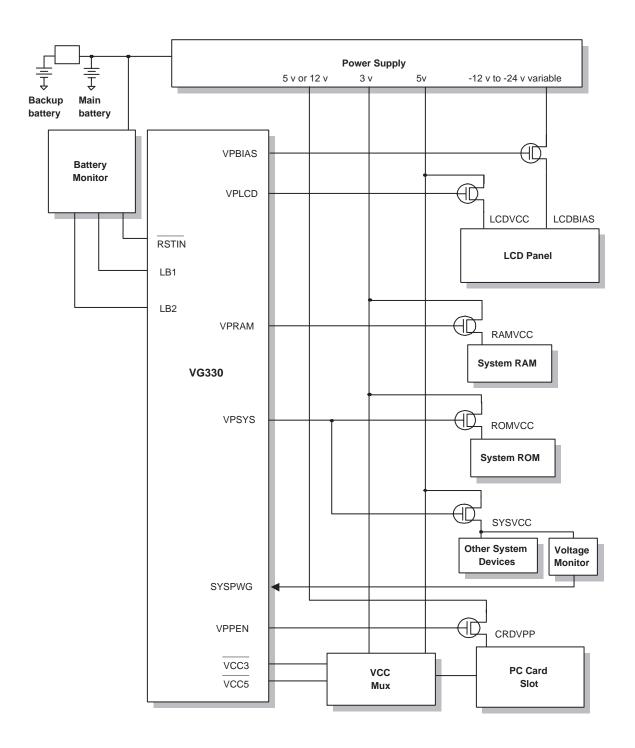

|    | Voltage Control Output Pins             |       |

|    | VPSYS and VPRAM                         |       |

|    | SYSPWG and VPSYS Relationship           |       |

|    |                                         |       |

|    | Power Control Registers                 |       |

|    | LCD Panel Power Sequencing              |       |

|    | VPLCD and VPBIAS Control Pins           |       |

|    | LCD Power-On Sequencing                 | 14-10 |

|    | LCD Power-Down Sequencing               | 14-10 |

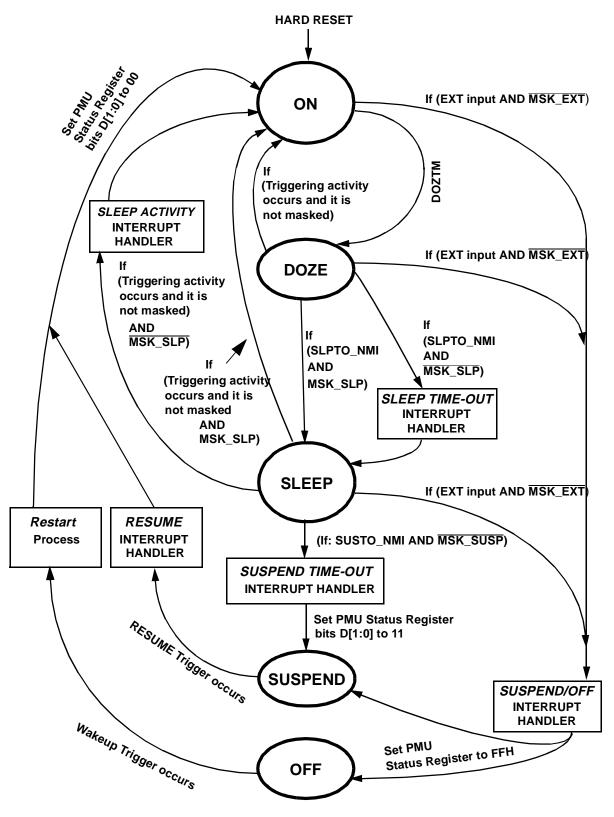

|    | PMU Modes                               | 14-11 |

|    | The Five PMU Power Management Modes     |       |

|    | ON Mode Operating Description           |       |

|    | Entering ON State                       |       |

|    | Exiting ON State                        |       |

|    |                                         |       |

|    | DOZE Mode Operating Description         |       |

|    | Entering DOZE Mode                      |       |

|    | Exiting DOZE Mode                       |       |

|    | SLEEP Mode Operating Description        |       |

|    | Entering SLEEP Mode                     | 14-12 |

|    | Exiting SLEEP Mode                      | 14-12 |

|    | SUSPEND Mode Operating Description      | 14-14 |

|    | Entering SUSPEND Mode                   |       |

|    | Exiting SUSPEND                         |       |

|    | OFF Mode Operating Description          |       |

|    | · · · · · · · · · · · · · · · · · · ·   |       |

|    | Entering OFF Mode                       |       |

|    | Exiting OFF Mode                        |       |

|    | Resumption of Operation                 |       |

|    | RESUME Triggers                         |       |

|    | Aborting a RESUME                       |       |

|    | Status Reporting                        | 14-17 |

|    | NMI Generation                          | 14-17 |

|    | SmartClock                              | 14-18 |

|    | SmartClock and DOZE/SLEEP Clock Control |       |

|    | Activity Monitoring                     |       |

|    | How SmartClock Works                    |       |

|    | SmartClock and APM                      |       |

|    |                                         |       |

|    | Clock Control and Interrupts            |       |

|    | Clock Control and Hold Request          |       |

|    | Static Clock Modes                      |       |

|    | Power Management Status                 |       |

|    | Serial Port Power Management            | 14-20 |

|    | Related Registers                       | 14-20 |

| 15 | RTC, Timer, and Interrupt Controller    |       |

|    | Introduction                            | 15-1  |

|    | Capabilities                            |       |

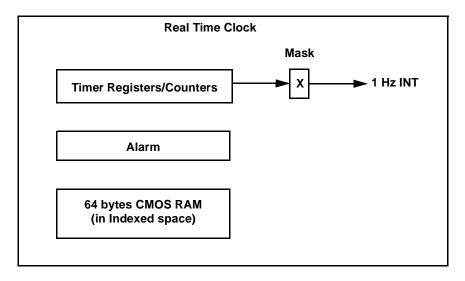

|    | RTC                                     |       |

|    |                                         |       |

|    | Timer                                   |       |

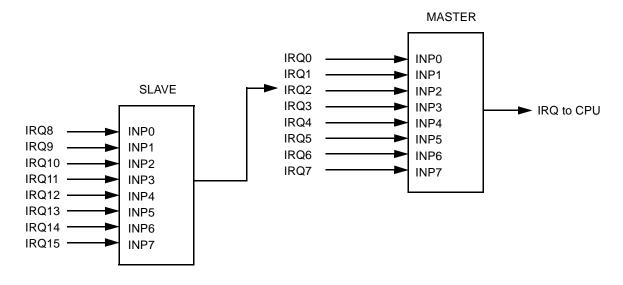

|    | Interrupt Controller Unit               | 75-1  |

|    | Real Time Clock                                   |       |

|----|---------------------------------------------------|-------|

|    | Architecture                                      | 15-2  |

|    | RTC Timers/Counters                               | 15-2  |

|    | RTC RAM                                           | 15-2  |

|    | RTC Alarm                                         | 15-2  |

|    | Related Registers                                 | 15-3  |

|    | Interrupt Controller Unit                         |       |

|    | IRQA and IRQB                                     |       |

|    | IRQ and GPIO Pins                                 | 15-4  |

|    | Interrupt Gating                                  | 15-4  |

|    | Architecture                                      |       |

|    | NMI in the VG330                                  |       |

|    | Related Registers                                 |       |

|    | Timer                                             |       |

| 16 |                                                   |       |

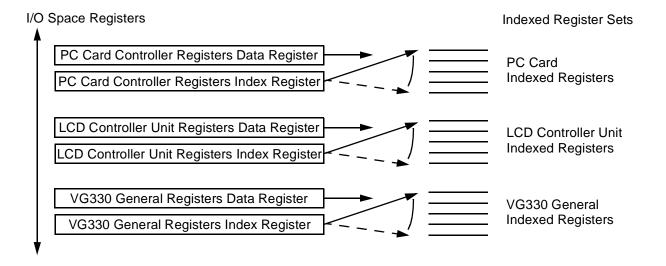

|    | Organization of This Chapter                      | 16-1  |

|    | Register Organization and Mapping                 |       |

|    | I/O Mapped Registers Listed                       |       |

|    | I/O Register Reference                            |       |

|    | 8259-Compatible Interrupt Controller Registers    |       |

|    | VG330 Index Register                              |       |

|    | VG330 Data Register                               |       |

|    | 8254-Compatible Counter/Timer Registers           |       |

|    | PC/XT Compatible PPIA Keyboard Data Register      |       |

|    | PC/XT Compatible PPIB Keyboard Control Register   |       |

|    | PC/XT Compatible PPIC System Status Register      |       |

|    | Mapper Address Register                           |       |

|    | Mapper Low Byte Data Register                     |       |

|    | Mapper High Byte Data Register                    |       |

|    | 16450 Serial Port Registers                       |       |

|    | Indexed Registers                                 |       |

|    | Revision Register                                 |       |

|    |                                                   |       |

|    | BCG Mode Register                                 |       |

|    | Memory Control 1 Register                         |       |

|    | Memory Control 2 Register                         |       |

|    | Alternate Display Buffer Start Address Register   |       |

|    | LCD Configuration Control Register                |       |

|    | ICU Mode Register                                 |       |

|    | SIO Clock Control Register                        |       |

|    | SIO Mode Register                                 |       |

|    | SIO Power Control Register                        |       |

|    | Timer Clock Control 1 Register                    |       |

|    | Timer Clock Control 2 Register                    |       |

|    | Address Pin Configuration Register 1              |       |

|    | Address Pin Configuration Register 2              |       |

|    | Address and Data Pin Control Register 3           |       |

|    | Main NMI Status Register                          |       |

|    | Programmable Chip Select 0 Mode Register          |       |

|    | Programmable Chip Select 0 Address Start Register |       |

|    | Programmable Chip Select 0 Address Stop Register  | 16-42 |

|    | Programmable Chip Select 0 Address High Register  | 16-43 |

|    | Programmable Chip Select 1 Mode Register          | 16-44 |

| Programmable Chip Select 1 Address Start Register    | 16-46  |

|------------------------------------------------------|--------|

| Programmable Chip Select 1 Address Stop Register     | 16-47  |

| Programmable Chip Select 1 Address High Register     | 16-48  |

| Programmable Chip Select 2 Mode Register             | 16-49  |

| Programmable Chip Select 2 Address Start Register    | 16-51  |

| Programmable Chip Select 2 Address Stop Register     | 16-52  |

| Programmable Chip Select 2 Address High Register     | 16-53  |

| Alternate PCS Mode Register                          |        |

| Alternate PCS Address Start Register                 |        |

| Alternate PCS Address Stop Register                  | 16-57  |

| Alternate PCS Address High Register                  |        |

| BIOS Time Base Low Register                          |        |

| BIOS Time Base High Register                         |        |

| Expansion Bus Mode Register                          |        |

| Expansion Bus I/O Wait State Control Register        |        |

| Expansion Bus Memory Wait State Control Register     |        |

| Top of Memory Register                               |        |

| Primary Interrupt Controller - ICU Shadow Register   |        |

| Secondary Interrupt Controller - ICU Shadow Register |        |

| GPIO Group A Mode Register 1                         |        |

| GPIO Group A Mode Register 2                         |        |

| GPIO Group A Mode Register 3                         |        |

| GPIO Group A Mode Register 4                         |        |

| GPIO Group B Mode Register 1                         |        |

| GPIO Group B Mode Register 2                         | 16-77  |

| GPIO Group B Mode Register 3                         | 16-79  |

| GPIO Group B Mode Register 4                         | 16-81  |

| GPIO Group C Mode Register 1                         | 16-83  |

| GPIO Group C Mode Register 2                         | 16-85  |

| GPIO Group C Mode Register 3                         |        |

| GPIO Group C Mode Register 4                         | 16-89  |

| GPIO Group A Data Register                           | 16-91  |

| GPIO Group B Data Register                           | 16-92  |

| GPIO Group C Data Register                           | 16-93  |

| SCAN Control A Register                              | 16-94  |

| SCAN Control B Register                              | 16-95  |

| SCAN Control C Register                              |        |

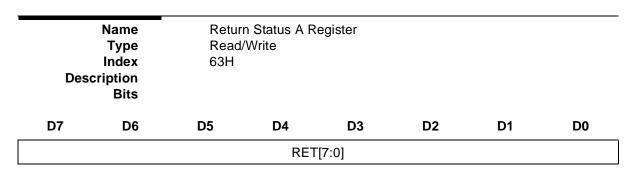

| Return Status A Register                             |        |

| Return Status B Register                             |        |

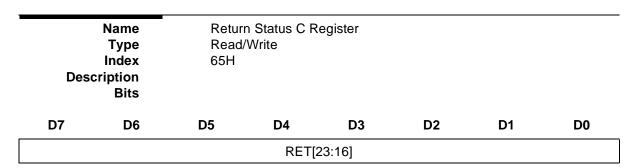

| Return Status C Register                             |        |

| Keyboard Scan Enable Register                        |        |

| Scan NMI Control and Status Register                 | 16-103 |

| Shadow XT Shift Register                             |        |

| RTC Seconds Register                                 |        |

| RTC Minutes Register                                 |        |

| RTC Hours Register                                   | 16-106 |

| RTC Day Low Register                                 |        |

| RTC Day High Register                                |        |

| RTC Alarm Seconds Register                           |        |

| RTC Alarm Minutes Register                           |        |

| RTC Alarm Hours Register                             |        |

| RTC Alarm Day Register                               |        |

| RTC Mode Register                                    |        |

| RTC Status Register                                  | 16-111 |

|      | ROM Wait State Control Register                       | .16-112  |

|------|-------------------------------------------------------|----------|

|      | RAM Wait State Control Register                       |          |

|      | Refresh Timer Register                                | .16-116  |

|      | Refresh Control Register                              |          |

|      | PMU Status Register                                   |          |

|      | PMU Control Register                                  |          |

|      | PMU Activity Mask Register                            |          |

|      | PMU NMI Mask Register                                 |          |

|      | PMU I/O Range Register                                |          |

|      | PMU Output Register                                   |          |

|      | PMU DOZE Timer Register                               |          |

|      | PMU SLEEP Timer Register                              |          |

|      | PMU SUSPEND Timer Register                            |          |

|      | PMU Activity Status Register                          |          |

|      | SmartClock Activity Level Register                    |          |

|      |                                                       |          |

| CLI  | SmartClock Control Register                           |          |

| _CU  | Register Reference                                    |          |

|      | LCU Registers                                         |          |

|      | CGA Index Register                                    |          |

|      | CGA Data Register                                     |          |

|      | CGA Mode Select Register A                            |          |

|      | CGA Mode Select Register B                            |          |

|      | Display Start Address MSB Register                    |          |

|      | Display Start Address LSB Register                    |          |

|      | LCD T1 Register                                       |          |

|      | LCD T2 Register                                       |          |

|      | LCD T3 Register                                       |          |

|      | LCD T4 Register                                       |          |

|      | LCD Horizontal Resolution Register                    |          |

|      | LCD Vertical Resolution Register                      |          |

|      | LCD Mode Register                                     |          |

| PC ( | Card Controller Register Reference                    |          |

|      | Identification and Revision Register                  |          |

|      | Interface Status Register                             |          |

|      | Power and RESETDRV Control Register                   |          |

|      | Interrupt and General Control Register                |          |

|      | Card Status Change Register                           |          |

|      | Address Window Enable Register                        |          |

|      | I/O Control Register                                  |          |

|      | I/O Address Start Low Byte Register                   | . 16-180 |

|      | I/O Address Start High Byte Register                  | . 16-180 |

|      | I/O Address Stop Low Byte Register                    | .16-181  |

|      | I/O Address Stop High Byte Register                   | .16-181  |

|      | System Memory Address Mapping Start Low Byte Register | .16-182  |

|      | PC Card Memory Data Width Register                    |          |

|      | System Memory Address Mapping Stop Low Byte Register  |          |

|      | PC Card Memory Wait State Selection Register          |          |

|      | Card Memory Offset Address Low Byte Register          |          |

|      | Card Memory Offset Address High Byte Register         |          |

|      | Card Detect and General Control Register              |          |

|      | Global Control Register                               |          |

|      | Card Voltage Sense Register                           |          |

|      | Card Voltage Select Register                          |          |

|      |                                                       |          |

## 17 System Design

| Introduction                                | 17-1 |

|---------------------------------------------|------|

| LCD Timing Calculations                     | 17-1 |

| Register Bits [4:0]                         | 17-2 |

| Deriving the Register Programming Values    | 17-3 |

| LCD T4 Register                             | 17-3 |

| LCD T1 Register                             | 17-4 |

| LCD T2 Register                             | 17-6 |

| LCD T3 Register                             | 17-7 |

| LCD T4 Register                             | 17-7 |

| LCD Timing Specifications                   |      |

| Sanyo LCM-5540-22NAK (640x480 Single Panel) |      |

| Optrex DMF-50404 (480x320 1/320 Duty Drive) | 17-9 |

| Optrex DMF-50081 (320x240 1/240 Duty Drive) |      |

## **List of Figures**

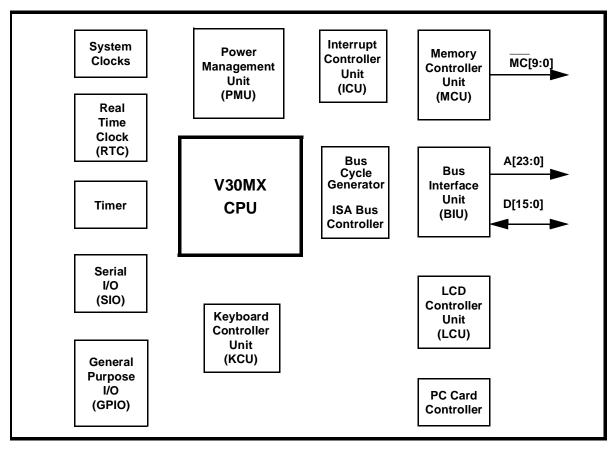

| Figure 1-1. VG330 Block Diagram                                                 | 1-1   |

|---------------------------------------------------------------------------------|-------|

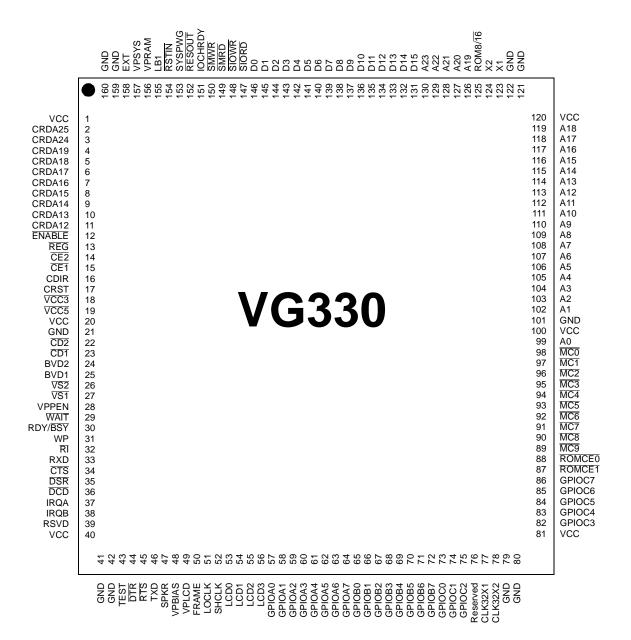

| Figure 2-1. VG330 Pinout Diagram                                                |       |

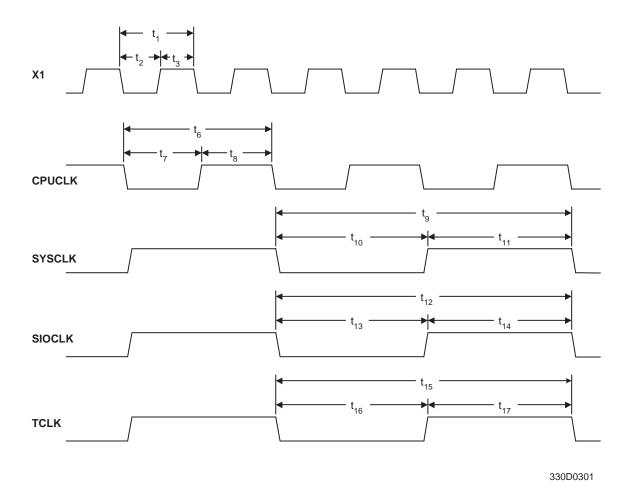

| Figure 3-1. VG330 Clocks Timing                                                 |       |

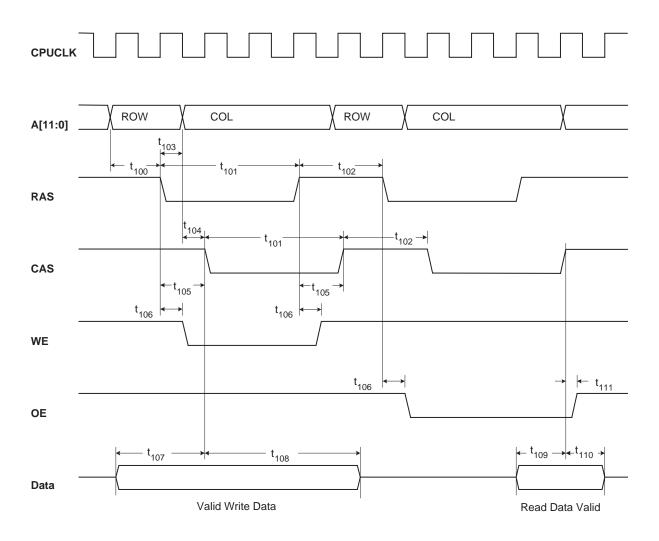

| Figure 3-2. DRAM Read/Write Timing                                              |       |

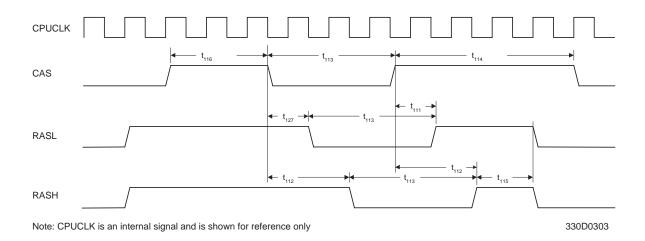

| Figure 3-3. DRAM Refresh Timing                                                 |       |

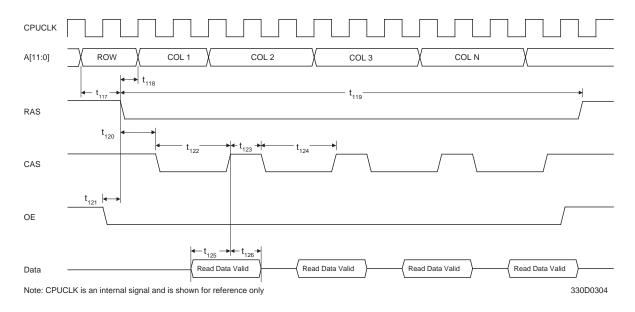

| Figure 3-4. DRAM Video Page Mode Read Timing                                    |       |

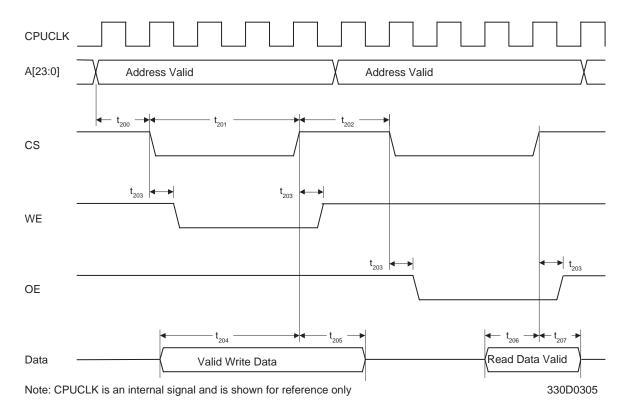

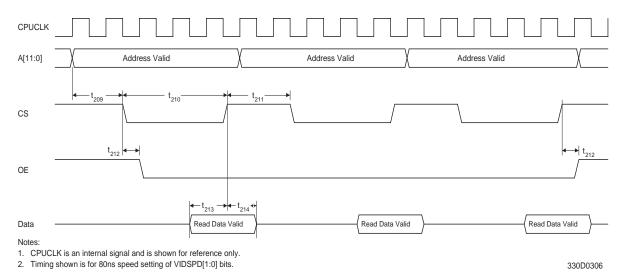

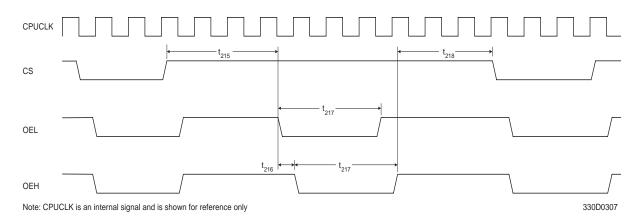

| Figure 3-5. PSRAM CPU Read/Write Timing                                         |       |

| Figure 3-6. PSRAM Video Read Timing                                             |       |

| Figure 3-7. PSRAM Refresh Timing                                                |       |

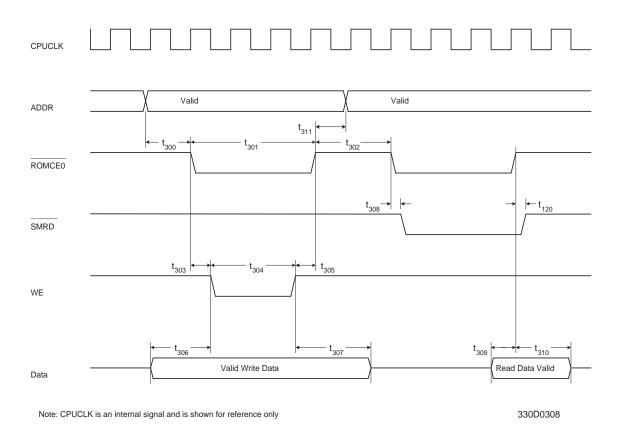

| Figure 3-8. ROM Timing                                                          |       |

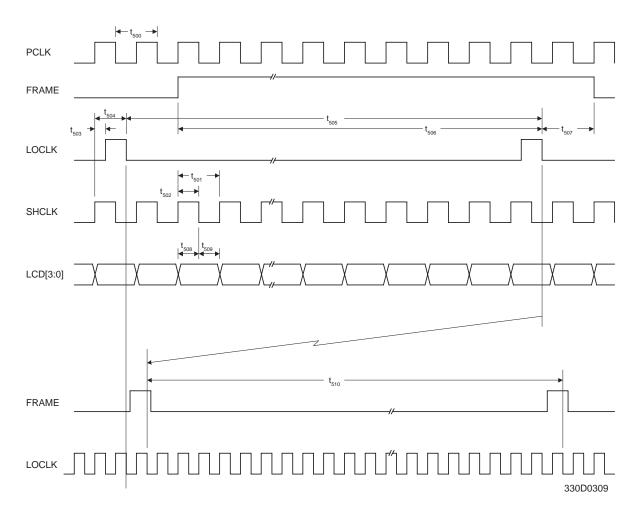

| Figure 3-9. LCD Panel Timing                                                    |       |

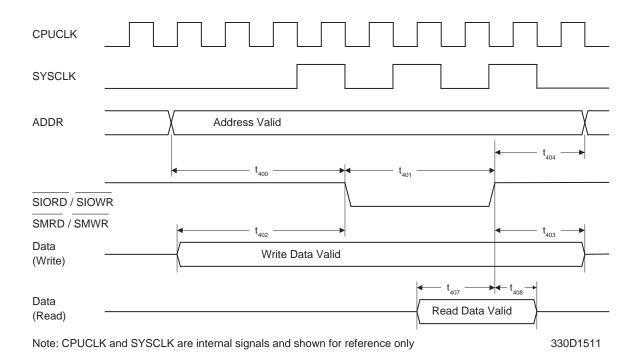

| Figure 3-10. ISA Cycle Timing - 8-Bit I/O or Memory Access                      |       |

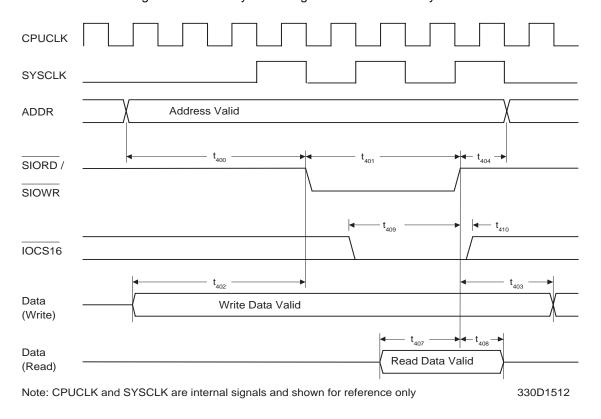

| Figure 3-11. ISA Cycle Timing - I/O Access to 16-Bit Device                     |       |

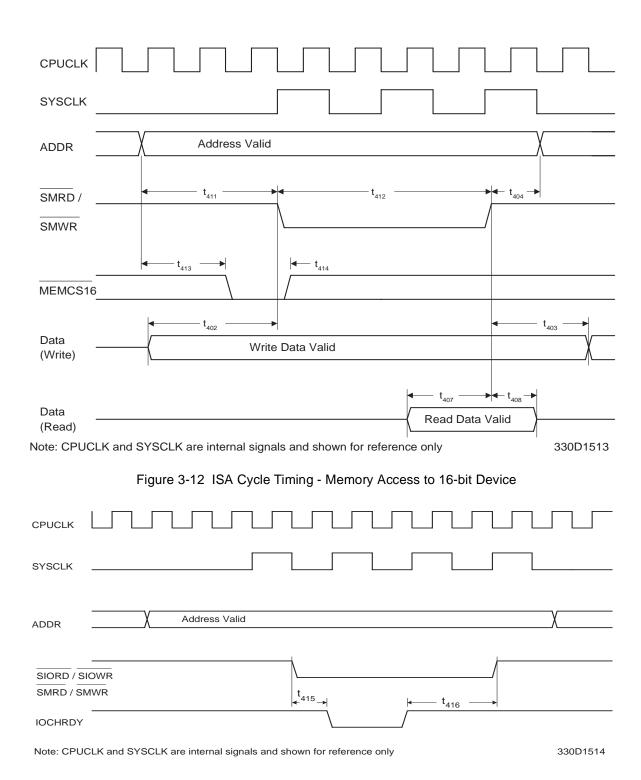

| Figure 3-12. ISA Cycle Timing - Memory Access to 16-bit Device                  |       |

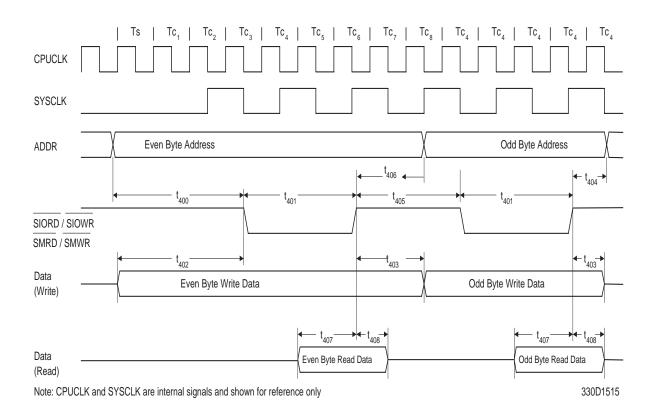

| Figure 3-13. ISA Cycle Timing - IOCHRDY Timing                                  |       |

| Figure 3-14. ISA Cycle Timing - 16-Bit Access to 8-Bit Device                   |       |

| Figure 3-14. ISA Cycle Hilling - To-bit Access to 8-bit Device                  |       |

| , ,                                                                             |       |

| Figure 3-16. PC Card IO Timing                                                  |       |

| Figure 4-1. Package Dimensions                                                  |       |

| Figure 5-1. VG330 Crystal Oscillator Connections                                |       |

| Figure 5-2. VG330 Clock Tree                                                    |       |

| Figure 6-1. System Buses and System Signals                                     |       |

| Figure 6-2. Address Management Components                                       |       |

| Figure 6-3. Memory Mapping Example                                              |       |

| Figure 7-1. VG330 ISA Inputs and Outputs                                        |       |

| Figure 7-2. Clock Stop Mode                                                     |       |

| Figure 7-3. ISA Bus Cycle Programming Options                                   | 7-10  |

| Figure 8-1. Memory Controller Unit                                              |       |

| Figure 8-2. VG330 Memory Mapper Regions Depend on Video Modes                   |       |

| Figure 8-3. x16 DRAM Design Example                                             |       |

| Figure 9-1. LCD Controller Main Elements                                        |       |

| Figure 10-1. Keyboard Controller Unit Block Diagram                             |       |

| Figure 10-2. Serial Keyboard Interface Timing                                   |       |

| Figure 10-3. Configuration for Keyboard Full Scan                               |       |

| Figure 10-4. Configuration for Keyboard Partial Scan                            |       |

| Figure 11-1. SIO Block Diagram                                                  |       |

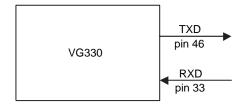

| Figure 11-2. Standard Serial I/O on Dedicated Pins                              |       |

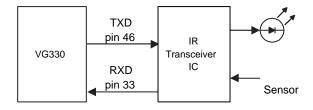

| Figure 11-3. Serial I/O Using Dedicated Pins and IR Conditioning                |       |

| Figure 11-4. Using Dedicated Pins with Standard Serial I/O and GPIO with IR I/O | O11-5 |

| Figure 11-5. Using IR on the Dedicated Serial                                   |       |

| I/O Pins and Standard Serial I/O on the GPIO Pins                               |       |

| Figure 11-6. SIO Power Management Control                                       |       |

| Figure 12-1. General Purpose Input-Output                                       |       |

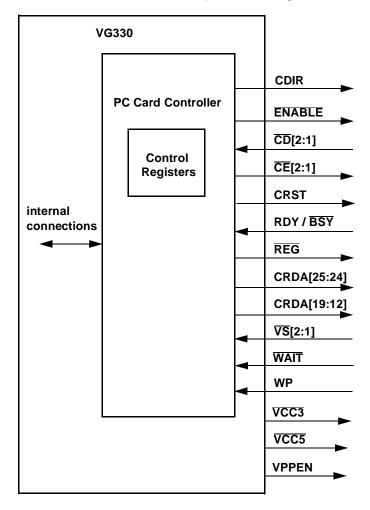

| Figure 13-1. PC Card Interface in VG330                                         | 13-2  |

| Figure 13-2. PC Card Connection to VG330                                        | 13-5  |

| Figure 14-1. Main Elements in the PMU                                           |       |

| Figure 14-2. Power Control Pin Application                                      | 14-6  |

| Figure 14-3. PMU States                                                         |       |

| Figure 15-1. RTC Block Diagram                                                  | 15-2  |

| Figure 15-2. ICU Block Diagram                                                  |       |

| Figure 16-1. Register Organization in the VG330                                 |       |

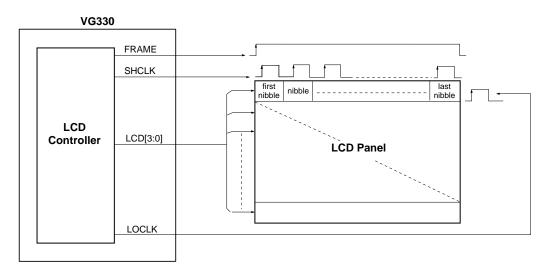

| Figure 17-1. Signal Interface to LCD Panel          | 17-1 |

|-----------------------------------------------------|------|

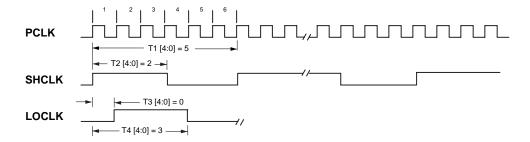

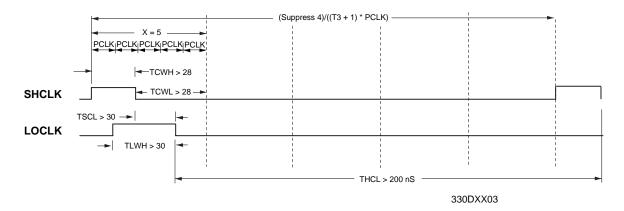

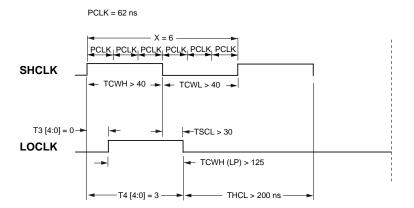

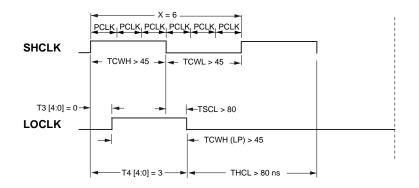

| Figure 17-2. Relationship of PCLK, SHCLK, and LOCLK | 17-2 |

| Figure 17-3. Sanyo LCM-5540-22NAK Timing            |      |

| Figure 17-4. Optrex DMF-50404 Timing                |      |

| Figure 17-5. Optrex DMF-50081 Timing                |      |

## **List of Tables**

| Table 1-1. | VG330 Main Function Modules                      | 1-3  |

|------------|--------------------------------------------------|------|

| Table 2-1. | Pins - Alphabetical List                         | 2-3  |

|            | Pin Descriptions                                 |      |

|            | Signals Routable Through GPIO                    |      |

|            | Clock Timing Parameters                          |      |

|            | DRAM Timing for Read/Write Cycles                |      |

|            | DRAM Timing for Refresh Cycles                   |      |

|            | DRAM Video Page Mode Read Timing                 |      |

|            | PSRAM CPU Read/Write Timing                      |      |

|            | PSRAM Video Read Timing                          |      |

|            | PSRAM Refresh Timing                             |      |

|            | ROM Timing                                       |      |

|            | LCD Panel Timing                                 |      |

|            | . ISA Timing                                     |      |

|            | . PC Card Memory Cycle Timing                    |      |

|            | . PC Card IO Cycle Timing                        |      |

|            | Clock-Related Signals and Pins                   |      |

|            | High Frequency Clock Parameters                  |      |

|            | 32 KHz Crystal Parameters                        |      |

|            | Clock Condition Versus Power Management States   |      |

|            | Handling of Memory and I/O Devices in the System |      |

|            | Address Management Components                    |      |

| Table 6-3. | Address Bits Output to DRAM by VG330             | 6-7  |

| Table 6-4. | Display Buffer Mapping                           | 6-8  |

| Table 6-5. | Data Steering                                    | 6-10 |

| Table 6-6. | Data Width Selection for Target Device Types     | 6-10 |

|            | Bus Activity Control Options                     |      |

| Table 7-1. | ISA Signals Provided on VG330 Dedicated Pins     | 7-3  |

| Table 7-2. | ISA Signals Available Through GPIO Pins          | 7-4  |

| Table 7-3. | ISA Signals Not Supported by the VG330           | 7-5  |

| Table 7-4. | VG330 Pins Used in ISA Interfacing               | 7-7  |

| Table 7-5. | Lead Off Delay                                   | 7-10 |

| Table 8-1. | Memory Controller-Related Signals and Pins       | 8-2  |

| Table 8-2. | Memory Controller Pin Functions                  | 8-3  |

| Table 8-3. | Memory and Memory Controller-Related Registers   | 8-10 |

| Table 9-1. | LCD Controller Unit Pins and Related Signals     | 9-3  |

|            | LCD Controller Unit Registers                    |      |

| Table 10-1 | . Supported Types of Keyboard Interfaces         | 10-1 |

|            | . Keyboard Signals and GPIO Pins                 |      |

| Table 10-3 | . SCAN and RETURN Control and Status Bits        | 10-8 |

|            | . Keyboard-Related Registers                     |      |

| Table 11-1 | . Serial Port Power Management States Table      | 11-7 |

|            | . SIO Power Control Register Bits                |      |

|            | . Serial I/O-Related Registers                   |      |

|            | . GPIO Pin Mapping Options                       |      |

|            | . Dedicated IRQs                                 |      |

|            | . GPIO-Related Registers                         |      |

|            | PC Card-Related Signals and Pins                 |      |

|            | PC Card-Related Registers                        |      |

|            | Power Management Mode Usage                      |      |

| Table 14-2 | . PMU-Related Signals and Pins                   | 14-3 |

| Table 14-3. | Activities Monitored by PMU                             | 14-4  |

|-------------|---------------------------------------------------------|-------|

| Table 14-4. | VG330 Dedicated Outputs for Device Power Supply Control | 14-8  |

| Table 14-5. | Design Assumptions for VPSYS and VPRAM                  | 14-9  |

| Table 14-6. | PMU Controller-Related Registers                        | 14-20 |

| Table 15-1. | IRQ Usage                                               | 15-5  |

| Table 16-1. | VG330 Registers in the I/O Address Space                | 16-2  |

| Table 16-2. | Sets of VG330 Indexed Registers                         | 16-14 |

| Table 16-3. | VG330 Indexed Registers - Primary Group                 | 16-14 |

|             | PC Card Controller Register List                        |       |

| Table 17-1. | LCD Register Contents                                   | 17-9  |

| Table 17-2. | LCD Register Contents                                   | 17-10 |

| Table 17-3. | LCD Register Contents                                   | 17-11 |

## Introduction

## 1.1 General Description

The VG330 is the next generation of the popular Vadem Single-Chip Platform for portable computing devices. It is targeted specifically towards systems requiring good processing power but which also provide longer battery life than that allowed by conventional CPUs.

Leveraging on the proven VG230 architecture, the VG330 provides enhanced power management for extended battery operation, along with improved PC CARD capabilities and increased CPU and memory performance. The VG330 also offers increased flexibility with the addition of 24 general purpose input/output (GPIO) pins. The VG330 is packaged in a 160 pin Thin Quad Flat Pack (TQFP).

#### 1.1.1 Processor Capabilities

The VG330 system design integrates system components with the NEC V30MX microprocessor, a high performance 32 MHz CPU core that is Intel 80186 binary code compatible but which provides increased performance over the 80186.

The VG330 operating at 3.3 V and 32 MHz clock rate provides a 2x performance improvement over Vadem's VG230.

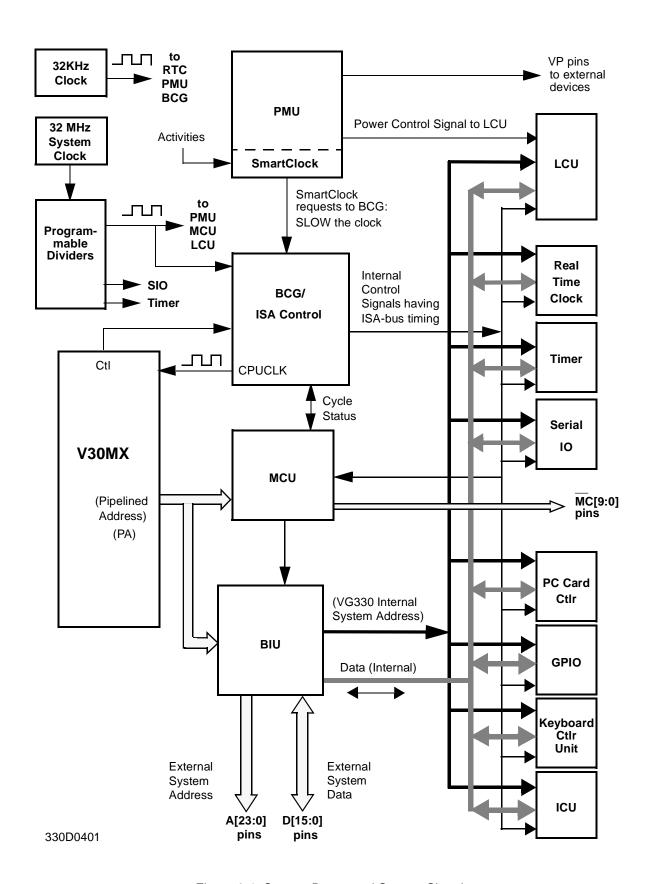

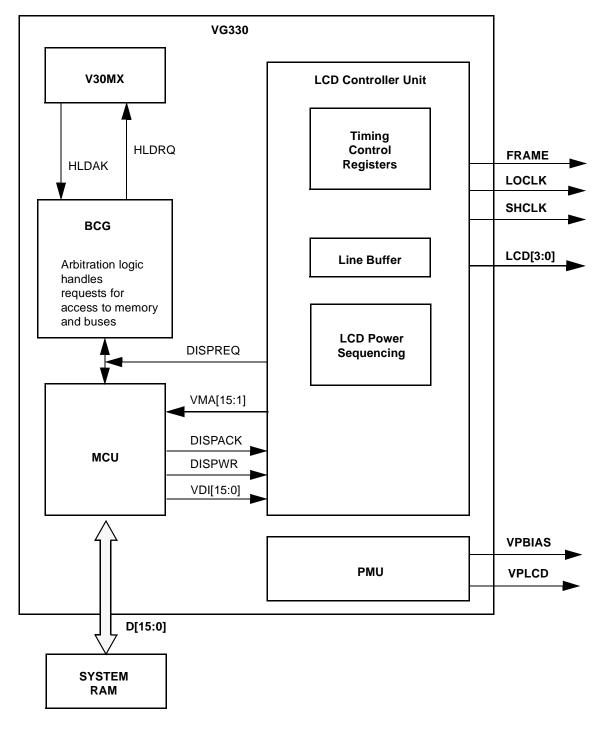

The main functional blocks in the VG330 are shown in Figure 1-1.

330D0101

Figure 1-1 VG330 Block Diagram

#### 1.2 Key Features

The VG330 is intended to support cost sensitive 3.3 V applications requiring high performance at low power consumption.

#### **CPU**

- NEC V30MX core offers a 2x performance improvement over a 5 V VG230 and a 4x improvement over a 3.3 V VG230.

- The V30MX can be operated at the maximum target CPU clock rate for highest performance

- Under power management control,VG330 can run with a slow clock and even supports a stopped clock.

- Programmable 32, 16, 11 or 8 MHz operating frequencies; full-speed clock rate may optionally be reduced under software control to conserve additional power for non compute-intensive applications.

- CPU supports a low-power Halt state

#### **System Features**

- Extensive power management support including DOZE, SLEEP and SMART-CLOCK, Low Battery Resume Inhibit, and Resume Abort.

- 8 and 16 bit Expansion Bus supporting most I/O and Memory ISA cycles, allowing easy connection of ISA devices.

- Real-time clock, dual programmable interrupt controllers and counter/timer.

#### **Memory Support**

- High performance integrated memory controller supporting:

- · Fast page-mode DRAM operation.

- · BIOS shadow option.

- Supports SRAM, PSRAM, DRAM, SRDRAM 16 bit memory configurations. Also supports new high density x8 and x16 DRAM.

- Extensive support for memory saving "execute-in-place" ROM applications.

- · Flash EPROM support.

#### **LCD Support**

Integrated LCD controller supports a wide variety of LCD panel resolutions. Supports 640x200, 640x400, and 640x480 monochrome graphics modes.

#### 1/0

- Integrated 16450 compatible serial port with HP Infra-Red interface option.

- Integrated PC CARD 2.1/ExCA/JEIDA 4.2 controller providing Intel 82365SL B-step register compatibility.

- 24 general purpose input/output (GPIO) pins provide configuration flexibility for maximizing utilization of all chip functions.

#### **Packaging**

160 pin Thin Quad Flat Pack (TQFP) package reduces footprint by nearly 25% compared to standard 160 pin QFP devices.

#### 1.3 Architectural Overview

#### 1.3.1 Single-Bus Architecture

The VG330 utilizes a Single-Bus Architecture. All external memory and I/O devices share a common address bus and data bus. A unique set of control signals are provided for each logical subbus such as main memory, Expansion, and PC CARD.

The VG330 is manufactured using a 0.5 micron 3 Volt process. All output pins are 3.3 V and driven to CMOS levels. Selected input pins are 5 V tolerant allowing 5 V devices to connect to the VG330 address and control buses. Any 5 V com-

ponents connected to the VG330 must support TTL level inputs.

The address bus, A[23:0], and data bus, D[15:0], are dynamically reconfigured on each bus cycle to match the address range and format, data width, and cycle timing of the target I/O or memory device.

#### 1.3.2 Main Modules

The main functional modules in the VG330 are shown in Figure 1-1 and listed in Table 1-1. They are discussed in detail in later chapters.

Table 1-1. VG330 Main Function Modules

| ID           | Name                      | Main Functions                                                                                                       |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------------------------|

| CPU          | Central Processing Unit   | NEC V30MX microprocessor                                                                                             |

| MCU          | Memory Control Unit       | Integrated memory controller providing all memory controller functions for system memory; no glue logic required.    |

| BCG / ISA    | Bus Cycle Generator       | Internal controller for system memory and I/O transactions; provides all required internal system timing             |

| BIU          | Bus Interface Unit        | Controller for activities on external ISA bus; controls internal address and data path handling                      |

| GPIO         | General Purpose I/O       | I/O pin programmable function matrix                                                                                 |

| PMU          | Power Management Unit     | Programmable automatic power control management of functional areas on and off the chip                              |

| KCU          | Keyboard Controller Unit  | XT-compatible standard serial keyboard interface (routed through GPIO pins), and matrix keyboard scanner capability. |

| ICU          | Interrupt Controller Unit | Dual AT-compatible interrupt controller (Intel 8259 compatible) providing 15 interrupt sources.                      |

| Timer        | Timer                     | XT-compatible timer (Intel 8254 compatible)                                                                          |

| PC Card Ctlr | PC Card Controller        | PCMCIA card controller/interface                                                                                     |

| RTC          | Real Time Clock           | Vadem-designed real time clock                                                                                       |

| SIO          | Serial I/O                | Serial I/O UART and Infrared device I/O                                                                              |

| LCU          | LCD Controller Unit       | Controller and interface to LCD panel                                                                                |

#### 1.3.3 Programmer's Model

All PC-XT compatible functional elements in the VG330 are programmable using the standard means for programming a PC-XT.

Vadem enhancements to the architecture are programmed using Vadem-specific indexed registers. These registers are described in the chapters covering the functional blocks, and in Chapter 16.

## 2 Pins and Signals

## 2.1 Introduction

This section describes VG330 pins and signals.

#### 2.1.1 Capabilities

- The VG330 is manufactured using a 0.5 micron 3 Volt process.

- All output pins are 3.3 V and driven to CMOS levels.

- Selected input pins are 5 V-tolerant, permitting direct-connection to 5 V peripherals.

## 2.2 Pinout Diagram

Figure 2-1 VG330 Pinout Diagram

## 2.3 Pin Assignments - Summary as Alphabetical Listing

Table 2-1. Pins - Alphabetical List

| Symbol      | Туре | Pin No.                    | Vcc                 | Characteristics  | lol/loh | State<br>During<br>SUSPEND | State<br>during<br>Reset                  |

|-------------|------|----------------------------|---------------------|------------------|---------|----------------------------|-------------------------------------------|

| A[23:0]     | 0    | 130:126,<br>119:102,<br>99 | 3.3 V               | CMOS three-state | 6 mA    | Low                        | A0- Low<br>A[23:2]-<br>Indetermi-<br>nent |

| BVD2        | I    | 24                         | 5 V tolerant        | CMOS Schmitt     | -       | High-Z                     | High-Z                                    |

| BVD1        | I    | 25                         | 5 V tolerant        | CMOS Schmitt     | -       | High-Z                     | High-Z                                    |

| CD2         | I    | 22                         | 5 V tolerant        | CMOS Schmitt     | -       | High-Z                     | High-Z                                    |

| CD1         | I    | 23                         | 5 V tolerant        | CMOS Schmitt     | -       | High-Z                     | High-Z                                    |

| CDIR        | 0    | 16                         | 3.3 V               | CMOS three-state | 3 mA    | Low                        | Low                                       |

| CE2         | 0    | 14                         | 3.3 V               | CMOS three-state | 6 mA    | High-Z: see note A         | High-Z                                    |

| CE1         | 0    | 15                         | 3.3 V               | CMOS three-state | 6 mA    | High-Z: see note A         | High-Z                                    |

| CLK32X2     | XTL  | 78                         | -                   | Crystal (RTC)    | -       | Running                    | Running                                   |

| CLK32X1     | XTL  | 77                         | -                   | Crystal (RTC)    | -       | Running                    | Running                                   |

| CRDA[25:24] | 0    | 2, 3                       | 3.3 V               | CMOS three-state | 6 mA    | Low: see<br>note A         | Low                                       |

| CRDA[19:12] | 0    | 4:11                       | 3.3 V               | CMOS three-state | 6 mA    | Low: see<br>note A         | Low                                       |

| CRST        | 0    | 17                         | 3.3 V               | CMOS three-state | 6 mA    | High-Z                     | High-Z                                    |

| CTS         | I    | 34                         | 3.3 V               | CMOS             | -       | Active                     | High-Z                                    |

| D[15:0]     | I/O  | 131:146                    | 3.3 V               | CMOS             | 6 mA    | Low                        |                                           |

| DCD         | I    | 36                         | 3.3 V toler-<br>ant | CMOS             | -       | Active                     | Indetermi-<br>nent                        |

| DSR         | I    | 35                         | 3.3 V               | CMOS             | -       | Active                     | High-Z                                    |

| DTR         | 0    | 44                         | 3.3 V               | CMOS three-state | 3 mA    | Active                     | High                                      |

| ENABLE      | 0    | 12                         | 3.3 V               | CMOS three-state | 3 mA    | High: see<br>note A        | High                                      |

| EXT         | I    | 158                        | 3.3 V               | CMOS Schmitt     | -       | Active                     | High-Z                                    |

| FRAME       | 0    | 50                         | 3.3 V               | CMOS             | 6 mA    | Low                        | Low                                       |

Table 2-1. Pins - Alphabetical List

| Symbol     | Туре | Pin No.                                                 | Vcc                                | Characteristics                                   | lol/loh | State<br>During<br>SUSPEND | State<br>during<br>Reset |

|------------|------|---------------------------------------------------------|------------------------------------|---------------------------------------------------|---------|----------------------------|--------------------------|

| GND        | GND  | 21, 41, 42,<br>79, 80,<br>101, 121,<br>122, 159,<br>160 | Ground<br>connec-<br>tions         |                                                   |         |                            |                          |

| GPIOA[7:0] | I/O  | 64:57                                                   | I = 5 V tolerant<br>O = 3.3 V      | CMOS Schmitt<br>CMOS                              | 6 mA    | Low                        | Indetermi-<br>nent       |

| GPIOB[7:0] | I/O  | 72:65                                                   | I = 5 V tol-<br>erant<br>O = 3.3 V | CMOS Schmitt<br>CMOS                              | 6 mA    | Low                        | Indetermi-<br>nent       |

| GPIOC[7:0] | I/O  | 75:73,<br>86:82                                         | I = 5 V tolerant<br>O = 3.3 V      | CMOS Schmitt<br>CMOS                              | 6 mA    | Low                        | Indetermi-<br>nent       |

| IOCHRDY    | I    | 151                                                     | 5 V tolerant                       | CMOS                                              |         | Low                        | Indetermi-<br>nent       |

| IRQA       | I    | 37                                                      | 5 V tolerant                       | CMOS Schmitt                                      |         | Low                        | High-Z                   |

| IRQB       | I    | 38                                                      | 5 V tolerant                       | CMOS Schmitt                                      |         | Low                        | High-Z                   |

| LB1        | I    | 155                                                     | 3.3 V                              | CMOS Schmitt                                      |         | Active                     | High-Z                   |

| LCD[3:0]   | 0    | 56:53                                                   | 3.3 V                              | CMOS                                              | 6 mA    | Low                        | Low                      |

| LOCLK      | 0    | 51                                                      | 3.3 V                              | CMOS                                              | 6 mA    | Low                        | Low                      |

| MC[9:0]    | 0    | 89:98                                                   | 3.3 V                              | CMOS three-state                                  | 6 mA    | Active                     | Indetermi-<br>nent       |

| RDY/BSY    | Ι    | 30                                                      | 5 V tolerant                       | CMOS Schmitt                                      |         | High-Z                     | High-Z                   |

| REG        | 0    | 13                                                      | 3.3 V                              | CMOS three-state                                  | 6 mA    | High-Z                     | High-Z                   |

| RESERVED   | I    | 76                                                      | 3.3 V                              | Pull this pin low<br>through 4.7 KOhm<br>resistor |         | -                          |                          |

| RESERVED   | I    | 39                                                      | 3.3 V                              | Pull this pin low<br>through 4.7 KOhm<br>resistor |         | -                          |                          |

| RESOUT     | 0    | 152                                                     | 3.3 V                              | CMOS                                              | 6 mA    | Low                        | Low                      |

| RI         | I    | 32                                                      | 3.3 V                              | CMOS Schmitt                                      |         | Active                     | High-Z                   |

| ROM8/ 16   | I    | 125                                                     | 3.3 V                              | CMOS                                              |         | Active                     | High-Z                   |

| ROMCE1     | 0    | 87                                                      | 3.3 V                              | CMOS three-state                                  | 3 mA    | Low                        | Indetermi-<br>nent       |

| ROMCE0     | 0    | 88                                                      | 3.3 V                              | CMOS three-state                                  | 3 mA    | Low                        | Indetermi-<br>nent       |

| RSTIN      | 1    | 154                                                     | 3.3 V                              | CMOS Schmitt                                      |         | Active                     | Low                      |

Table 2-1. Pins - Alphabetical List

| Symbol | Туре | Pin No.                       | Vcc          | Characteristics      | lol/loh | State<br>During<br>SUSPEND | State<br>during<br>Reset |

|--------|------|-------------------------------|--------------|----------------------|---------|----------------------------|--------------------------|

| RTS    | 0    | 45                            | 3.3 V        | CMOS three-state     | 3 mA    | Active                     | High                     |

| RXD    | I    | 33                            | 3.3 V        | CMOS                 |         | Active                     | High-Z                   |

| SHCLK  | 0    | 52                            | 3.3 V        | CMOS three-state     | 6 mA    | Low                        | Low                      |

| SIORD  | 0    | 147                           | 3.3 V        | CMOS three-state     | 3 mA    | Low                        | Indetermi-<br>nent       |

| SIOWR  | 0    | 148                           | 3.3 V        | CMOS three-state     | 3 mA    | Low                        | Indetermi-<br>nent       |

| SMRD   | 0    | 149                           | 3.3 V        | CMOS three-state     | 3 mA    | Low                        | indetermi-<br>nent       |

| SMWR   | 0    | 150                           | 3.3 V        | CMOS three-state     | 3 mA    | Low                        | Indetermi-<br>nent       |

| SPKR   | 0    | 47                            | 3.3 V        | CMOS three-state     | 3 mA    | Low                        | Low                      |

| SYSPWG | I    | 153                           | 3.3 V        | CMOS Schmitt         |         | Active                     | Low                      |

| TEST   | I    | 43                            | 3.3 V        | CMOS Schmitt         |         | Low                        | Low                      |

| TXD    | 0    | 46                            | 3.3 V        | CMOS three-state     | 3 mA    | Active                     | Indetermi-<br>nent       |

| VCC    | PWR  | 1, 20, 40,<br>81, 100,<br>120 | 3.3 V        |                      |         |                            |                          |

| VCC3   | 0    | 18                            | 3.3 V        | CMOS                 | 3 mA    | High: see<br>note A        | High                     |

| VCC5   | 0    | 19                            | 3.3 V        | CMOS                 | 3 mA    | High: see<br>note A        | High                     |

| VPBIAS | 0    | 48                            | 3.3 V        | CMOS three-state     | 3 mA    | Active- set to Off         | High-Z                   |

| VPLCD  | 0    | 49                            | 3.3 V        | CMOS three-state     | 3 mA    | Off                        | High-Z                   |

| VPPEN  | 0    | 28                            | 3.3 V        | CMOS                 | 3 mA    | Low                        | Low                      |

| VPRAM  | 0    | 156                           | 3.3 V        | CMOS                 | 3 mA    | High                       | High                     |

| VPSYS  | 0    | 157                           | 3.3 V        | CMOS                 | 3 mA    | ON -High                   | High                     |

| VS2    | I    | 26                            | 3.3 V        | CMOS                 |         | High-Z                     | High-Z                   |

| VS1    | I    | 27                            | 3.3 V        | CMOS                 |         | High-Z                     | High-Z                   |

| WAIT   | I    | 29                            | 5 V tolerant | CMOS                 |         | High-Z                     | High-Z                   |

| WP     | I    | 31                            | 5 V tolerant | CMOS                 |         | High-Z                     | High-Z                   |

| X2     | XTL  | 124                           |              | Crystal (main clock) |         | Low                        | Running                  |

| X1     | XTL  | 123                           |              | Crystal (main clock) |         | High-Z                     | Running                  |

Note A. PCMCIA interface is controlled by bit D7, OE, of the PC Card Controller Power and RESET-

DRV Control Register, Index 02H in the PC Card Register set.

## 2.4 Pin Descriptions

**Table 2-2. Pin Descriptions**

| Symbol      | Туре | Pin No.                | Description                                                                                                                                                                                                                                    |

|-------------|------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[23:0]     | 0    | 130:126,<br>119:102,99 | Address Bus. All external memory and I/O devices attach to this common address bus. The function of this bus is dynamically set according to the device type being addressed in any cycle: DRAM, SRAM, PC Card, ROM, I/O, or Expansion memory. |

| BVD2        | I    | 24                     | Battery voltage status input for PC <u>Card memory cards</u> . Redefined for PC Card I/O cards as <u>SPKR</u> .                                                                                                                                |

| BVD1        | I    | 25                     | Battery voltage status input for PC Card memory cards. Redefined for PC Card I/O cards as STSCHG.                                                                                                                                              |

| CDIR        | 0    | 16                     | Direction control for PC Card Odd and Even Byte data buffers.  0 = transfer from VG330 to PC Card (write to card)  1 = transfer from PC Card to VG330                                                                                          |

| CD2         | I    | 22                     | Card detect status input from PC Card slot.                                                                                                                                                                                                    |

| CD1         | I    | 23                     | Card detect status input from PC Card slot.                                                                                                                                                                                                    |

| CE2         | 0    | 14                     | Odd byte chip select signal to PC Card memory and I/O cards.                                                                                                                                                                                   |

| CE1         | 0    | 15                     | Even byte chip select signal to PC Card memory and I/O cards.                                                                                                                                                                                  |

| CLK32X2     | XTL  | 78                     | 32.768 KHz crystal connection.                                                                                                                                                                                                                 |

| CLK32X1     | XTL  | 77                     | 32.768 KHz crystal connection; external clock input to VG330.                                                                                                                                                                                  |

| CRDA[25:24] | 0    | 2,3                    | PC card address bits. These bits may be directly connected to the PC card socket.                                                                                                                                                              |

| CRDA[19:12] | 0    | 4:11                   | PC card address bits. These bits may be directly connected to the PC card socket.                                                                                                                                                              |

| CRST        | 0    | 17                     | Reset signal for PC Card memory and I/O cards.                                                                                                                                                                                                 |

| CTS         | I    | 34                     | Serial Port clear to send.                                                                                                                                                                                                                     |

| D[15:0]     | I/O  | 131:146                | Bi-directional System Data Bus. All external memory and I/O devices attach to this common data bus. 8-bit devices must reside on the D[7:0] half of the system data bus.                                                                       |

| DCD         | Ī    | 36                     | Serial Port data carrier detect.                                                                                                                                                                                                               |

| DSR         | I    | 35                     | Serial Port data set ready.                                                                                                                                                                                                                    |

| DTR         | 0    | 44                     | Serial Port data transmit ready.                                                                                                                                                                                                               |

| ENABLE      | 0    | 12                     | Enable for PC Card address/control buffers.                                                                                                                                                                                                    |

**Table 2-2. Pin Descriptions**

| Symbol     | Туре | Pin No.                                              | Description                                                                                                                                                                                                                             |

|------------|------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXT        | I    | 158                                                  | External switch input. Active high. Used to command SUSPEND/RESUME from outside the VG330. See also description of PMU NMI Mask Register bit D1, MSK_EXT. (Register Index C4H.)                                                         |

| FRAME      | 0    | 50                                                   | Frame clock to LCD.                                                                                                                                                                                                                     |

| GND        | GND  | 21, 41, 42,<br>79, 80, 101,<br>121, 122,<br>159, 160 | Ground connections.                                                                                                                                                                                                                     |

| GPIOA[7:0] | I/O  | 64:57                                                | General Purpose I/O Pin Group A. See GPIO pin mapping section in Chapter 10 for programming options.                                                                                                                                    |

| GPIOB[7:0] | I/O  | 72:65                                                | General Purpose I/O Pin Group B. See GPIO pin mapping section in Chapter 10 for programming options.                                                                                                                                    |

| GPIOC[7:0] | I/O  | 75:73, 86:82                                         | General Purpose I/O Pin Group C. See GPIO pin mapping section in Chapter 10 for programming options.                                                                                                                                    |

| IOCHRDY    | I    | 151                                                  | I/O Channel Ready input, OR'ed with internal ready sources to insert CPU wait states.                                                                                                                                                   |

| IRQA       | I    | 37                                                   | System interrupt request input to internal 8259. It is user programmable to be any one of IRQ[7:1], using ICU Mode Register.                                                                                                            |

| IRQB       | I    | 38                                                   | System interrupt request input to internal 8259. It is user programmable to be any one of IRQ[7:1], using ICU Mode Register.                                                                                                            |