Digital Signal Processing

# DIGITAL SIGNAL PROCESSING

1993

MARRIS

DB 302A -

HARRIS SEMICONDUCTOR

# HARRIS SEMICONDUCTOR DSP PRODUCTS

This Digital Signal Processing databook represents the full line of Harris Semiconductor DSP products for commercial and military applications and supersedes previously published DSP material under the Harris, GE, RCA or Intersil names. For a complete listing of all Harris Semiconductor products, please refer to the Product Selection Guide (PSG-201S; ordering information below.)

For complete, current and detailed technical specifications on any Harris devices please contact the nearest Harris sales, representative or distributor office; or direct literature requests to:

Harris Semiconductor Literature Department P.O. Box 883, MS CB1-25 Melbourne, FL 32901 FAX 407-724-3937

#### U.S. HEADQUARTERS

Harris Semiconductor 1301 Woody Burke Road Melbourne, Florida 32902 TEL: (407) 724-3000

#### **SOUTH ASIA**

Harris Semiconductor H.K. Ltd 13/F Fourseas Building 208-212 Nathan Road Tsimshatsui, Kowloon Hong Kong TEL: (852) 723-6339

#### **EUROPEAN HEADQUARTERS**

Harris Semiconductor Mercure Centrer 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2-246-21.11

#### **NORTH ASIA**

Harris K.K. Shinjuku NS Bldg. Box 6153 2-4-1 Nishi-Shinjuku Shinjuku-ku, Tokyo 163 Japan TEL: 81-3-3345-8911

See our Specs in CAPS

Copyright © Harris Corporation 1992 (All Rights Reserved) Printed in USA, 9/1992

Harris Semiconductor products are sold by description only. All specifications in this product guide are applicable only to packaged products; specifications for die are available upon request. Harris reserves the right to make changes in circuit design, specifications and other information at any time without prior notice. Accordingly, the reader is cautioned to verify that information in this publication is current before placing orders. Reference to products of other manufacturers are solely for convenience of comparison and do not imply total equivalency of design, performance, or otherwise.

# DIGITAL SIGNAL PROCESSING

#### FOR COMMERCIAL AND MILITARY APPLICATIONS

**General Information**

Multipliers

| 3  | One Dimensional Filters            |

|----|------------------------------------|

| 4  | Two Dimensional Filters            |

| 5  | Signal Synthesizers                |

| 6  | Special Function                   |

| 7  | Development Tools                  |

| 8  | Application Notes                  |

| 9  | Quality and Reliability            |

| 10 | Packaging and Ordering Information |

| 11 | Sales Offices                      |

# DIGITAL SIGNAL PROCESSING PRODUCT TECHNICAL ASSISTANCE

For technical assistance on the Harris products listed in this databook, please contact Field Applications Engineering staff available at one of the following Harris Sales Offices:

| UNITED STATES |                        |

|---------------|------------------------|

| CALIFORNIA    | Woodland Hills         |

| FLORIDA       | Melbourne              |

| GEORGIA       | Duluth                 |

| ILLINOIS      | Schaumburg708-240-3499 |

| NEW JERSEY    | Mt. Laurel             |

| NEW YORK      | Great Neck             |

| INTERNATIONAL |                        |

| FRANCE        | Paris                  |

| GERMANY       | Munich                 |

| HONG KONG     | Kowloon                |

| ITALY         | Milano 39-2-262-0761   |

| JAPAN         | Tokyo                  |

| KOREA         | Seoul                  |

| U.K.          | Camberley              |

#### **GENERAL INFORMATION**

#### **ALPHA NUMERIC PRODUCT INDEX**

|                              |                                                                | PAGE  |

|------------------------------|----------------------------------------------------------------|-------|

| DECI ● MATE™                 | Harris HSP43220 Decimating Digital Filter Development Software | 7-3   |

| HMA510                       | 16 x 16-Bit CMOS Parallel Multiplier Accumulator               | 2-3   |

| HMA510/883                   | 16 x 16-Bit CMOS Parallel Multiplier Accumulator               | 2-10  |

| HMU16/HMU17                  | 16 x 16-Bit CMOS Parallel Multipliers                          | 2-15  |

| HMU16/883                    | 16 x 16-Bit CMOS Parallel Multiplier                           | 2-25  |

| HMU17/883                    | 16 x 16-Bit CMOS Parallel Multiplier                           | 2-31  |

| HSP-EVAL                     | DSP Evaluation Platform NEW PRODUCT                            | 7-7   |

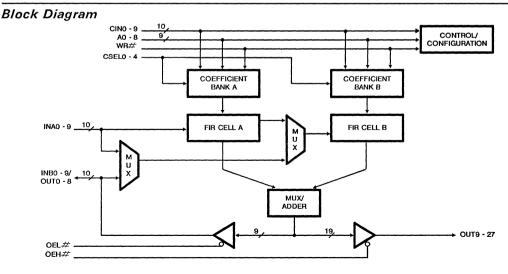

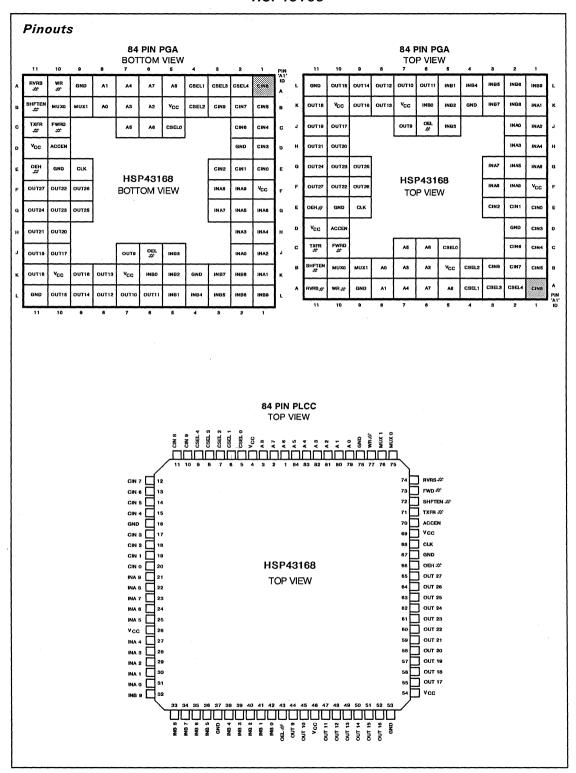

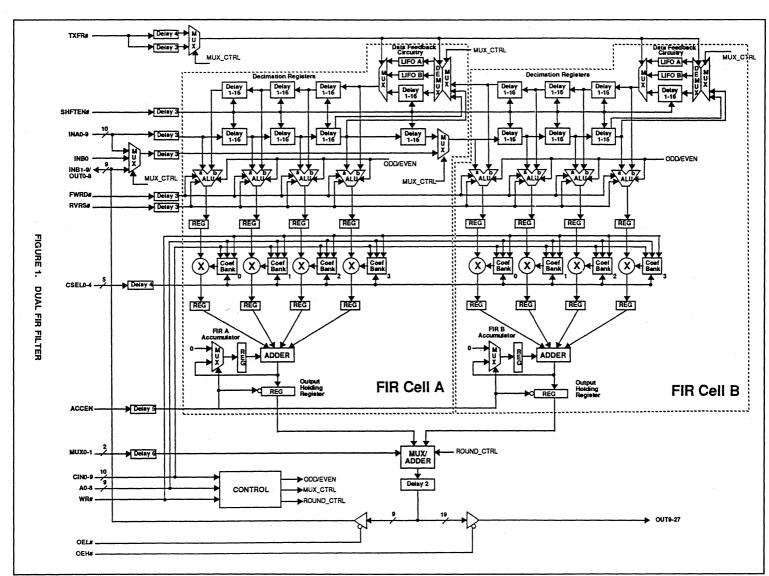

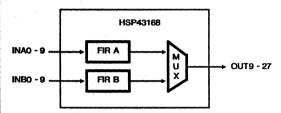

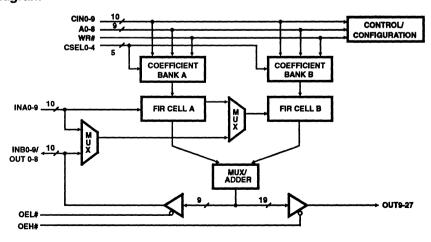

| HSP43168                     | Dual FIR Filter NEW PRODUCT                                    | 3-3   |

| HSP43168/883                 | Dual FIR Filter NEW PRODUCT                                    | 3-19  |

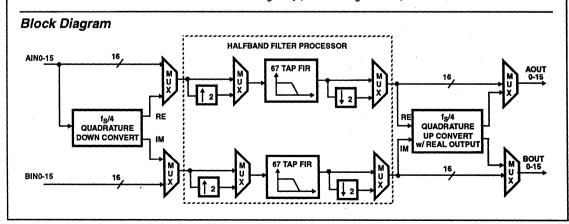

| HSP43216                     | Halfband Filter NEW PRODUCT                                    | 3-116 |

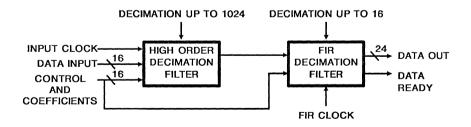

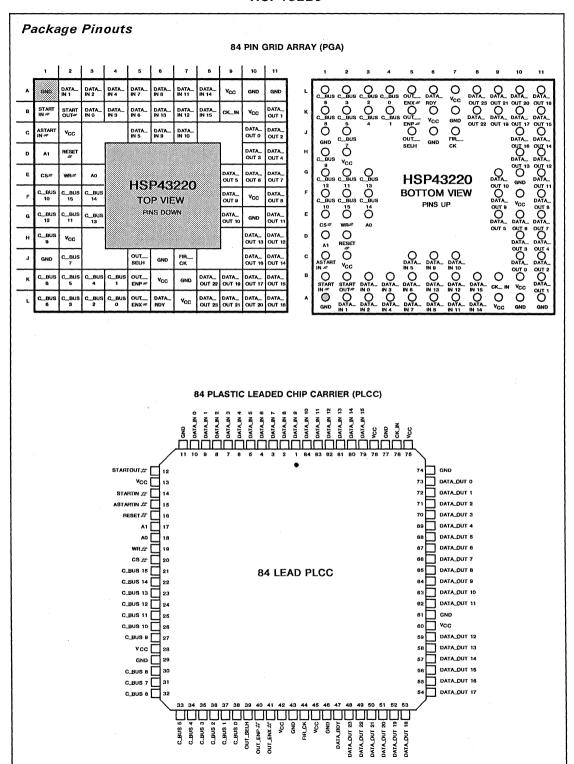

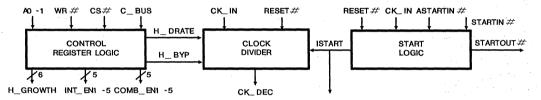

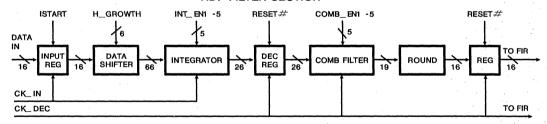

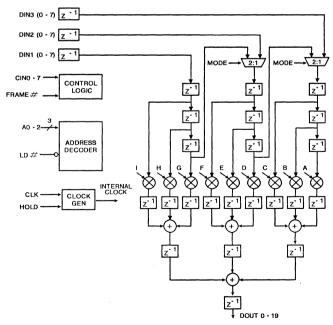

| HSP43220                     | Decimating Digital Filter                                      | 3-27  |

| HSP43220/883                 | Decimating Digital Filter                                      | 3-47  |

| HSP43481                     | Digital Filter                                                 | 3-54  |

| HSP43481/883                 | Digital Filter                                                 | 3-69  |

| HSP43881                     | Digital Filter                                                 | 3-74  |

| HSP43881/883                 | Digital Filter                                                 | 3-89  |

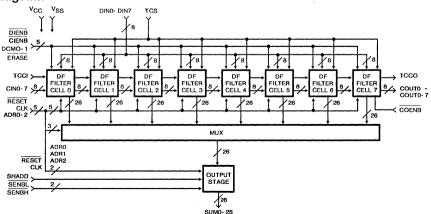

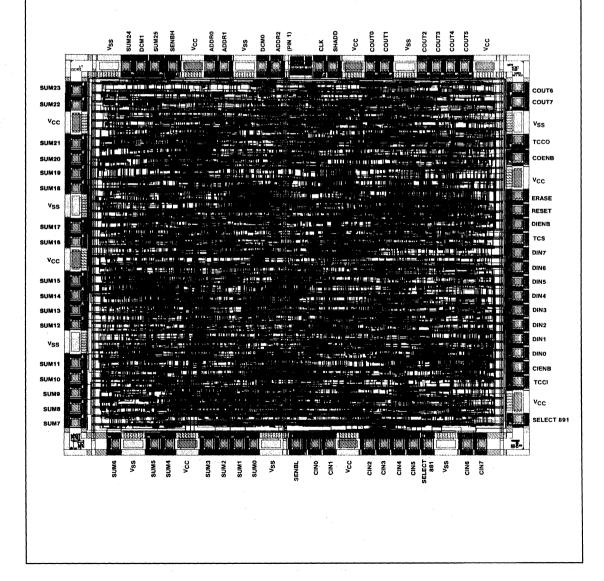

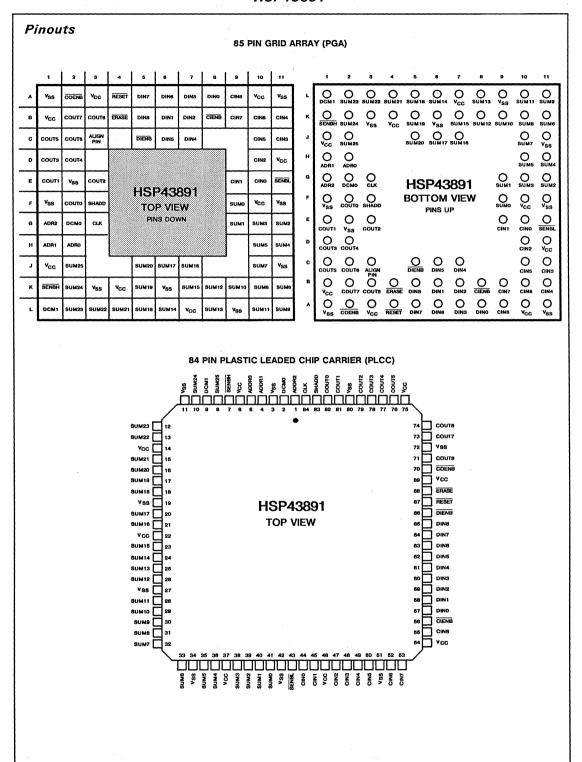

| HSP43891                     | Digital Filter                                                 | 3-95  |

| HSP43891/883                 | Digital Filter                                                 | 3-110 |

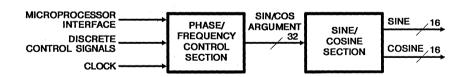

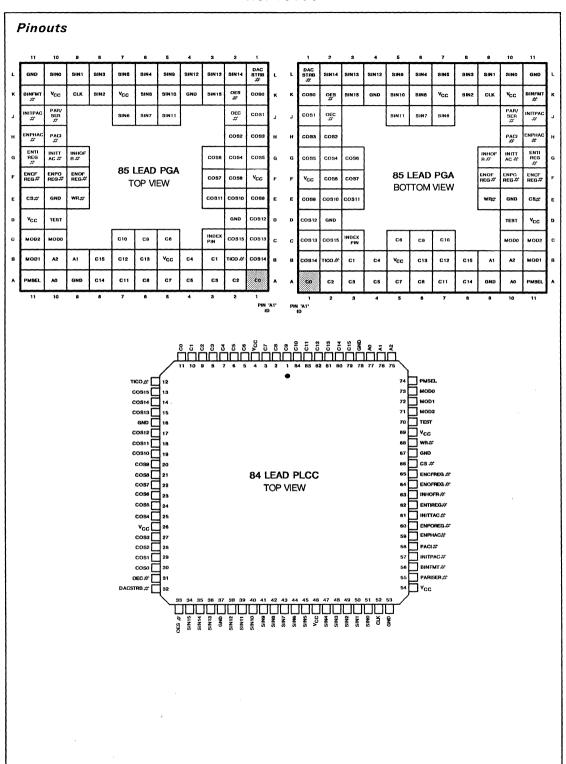

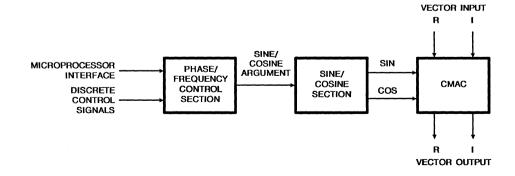

| HSP45102                     | 12 Bit Numerically Controlled Oscillator                       | 5-3   |

| HSP45106                     | 16 Bit Numerically Controlled Oscillator                       | 5-10  |

| HSP45106/883                 | 16 Bit Numerically Controlled Oscillator                       | 5-20  |

| HSP45116                     | Numerically Controlled Oscillator/Modulator                    | 5-26  |

| HSP45116/883                 | Numerically Controlled Oscillator/Modulator                    | 5-41  |

| HSP45116-DB                  | HSP45116 Daughter Board NEW PRODUCT                            | 7-8   |

| HSP45240                     | Address Sequencer                                              | 6-3   |

| HSP45240/883                 | Address Sequencer                                              | 6-15  |

| HSP45256                     | Binary Correlator NEW PRODUCT                                  | 6-21  |

| HSP45256/883                 | Binary Correlator NEW PRODUCT                                  | 6-34  |

| HSP48410                     | Histogrammer/Accumulating Buffer NEW PRODUCT                   | 6-42  |

| HSP48901                     | 3 x 3 Image Filter                                             | 4-3   |

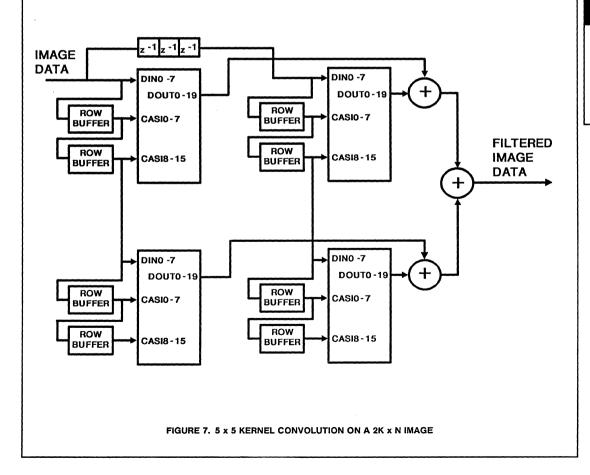

| HSP48908                     | Two Dimensional Convolver                                      | 4-12  |

| HSP48908/833                 | Two Dimensional Convolver                                      | 4-28  |

| HSP50016                     | Digital Down Converter NEW PRODUCT                             | 5-48  |

| HSP9501                      | Programmable Data Buffer                                       | 6-53  |

| HSP9520/9521<br>ISP9520/9521 | Multilevel Pipeline Register                                   | 6-60  |

DECI • MATE™ is a Trademark of Harris Corporation

#### PRODUCT INDEX BY FAMILY

| <b>MULTIPLIERS</b>           |                                                                | PAGE  |

|------------------------------|----------------------------------------------------------------|-------|

| HMA510                       | 16 x 16-Bit CMOS Parallel Multiplier Accumulator               | 2-3   |

| HMA510/883                   | 16 x 16-Bit CMOS Parallel Multiplier Accumulator               | 2-10  |

| HMU16/HMU17                  | 16 x 16-Bit CMOS Parallel Multipliers                          | 2-15  |

| HMU16/883                    | 16 x 16-Bit CMOS Parallel Multiplier                           | 2-25  |

| HMU17/883                    | 16 x 16-Bit CMOS Parallel Multiplier                           | 2-31  |

| <b>ONE DIMENSI</b>           | ONAL FILTERS                                                   |       |

| HSP43168                     | Dual FIR Filter NEW PRODUCT                                    | 3-3   |

| HSP43168/883                 | Dual FIR Filter NEW PRODUCT                                    | 3-19  |

| HSP43216                     | Halfband Filter NEW PRODUCT                                    | 3-116 |

| HSP43220                     | Decimating Digital Filter                                      | 3-27  |

| HSP43220/883                 | Decimating Digital Filter                                      | 3-47  |

| HSP43481                     | Digital Filter                                                 | 3-54  |

| HSP43481/883                 | Digital Filter                                                 | 3-69  |

| HSP43881                     | Digital Filter                                                 | 3-74  |

| HSP43881/883                 | Digital Filter                                                 | 3-89  |

| HSP43891                     | Digital Filter                                                 | 3-95  |

| HSP43891/883                 | Digital Filter                                                 | 3-110 |

| <b>TWO DIMENS</b>            | IONAL FILTERS                                                  |       |

| HSP48901                     | 3 x 3 Image Filter                                             | 4-3   |

| HSP48908                     | Two Dimensional Convolver                                      | 4-12  |

| HSP48908/833                 | Two Dimensional Convolver                                      | 4-28  |

| SIGNAL SYNT                  | HESIZERS                                                       |       |

| HSP45102                     | 12 Bit Numerically Controlled Oscillator                       | 5-3   |

| HSP45106                     | 16 Bit Numerically Controlled Oscillator                       |       |

| HSP45106/883                 | 16 Bit Numerically Controlled Oscillator                       | 5-20  |

| HSP45116                     | Numerically Controlled Oscillator/Modulator                    | 5-26  |

| HSP45116/883                 | Numerically Controlled Oscillator/Modulator                    | 5-41  |

| HSP50016                     | Digital Down Converter NEW PRODUCT                             | 5-48  |

| SPECIAL FUN                  | CTION                                                          |       |

| HSP45240                     | Address Sequencer                                              | 6-3   |

| HSP45240/883                 | Address Sequencer                                              | 6-15  |

| HSP45256                     | Binary Correlator NEW PRODUCT                                  | 6-21  |

| HSP45256/883                 | Binary Correlator NEW PRODUCT                                  | 6-34  |

| HSP48410                     | Histogrammer/Accumulating Buffer NEW PRODUCT                   | 6-42  |

| HSP9501                      | Programmable Data Buffer                                       | 6-53  |

| HSP9520/9521<br>ISP9520/9521 | Multilevel Pipeline Register                                   | 6-60  |

| DEVELOPMEN                   | NT TOOLS                                                       |       |

| DECI • MATE                  | Harris HSP43220 Decimating Digital Filter Development Software | 7-3   |

| HSP-EVAL                     | DSP Evaluation Platform NEW PRODUCT                            | 7-7   |

| HSP45116-DB                  | HSP45116 Daughter Board NEW PRODUCT                            | 7-8   |

/883 Data Sheet Format - In the interests of conserving space, data sheets for /883 qualified products have been printed without the Pinouts, Pin Description, Waveforms, AC Test Load Circuit and Design Information sections. The information in these sections can be obtained from the corresponding portion of the commercial data sheet.

### **MULTIPLIERS**

|             |                                                  | PAGE |

|-------------|--------------------------------------------------|------|

| DATA SHEETS |                                                  |      |

| HMA510      | 16 x 16-Bit CMOS Parallel Multiplier Accumulator | 2-3  |

| HMA510/883  | 16 x 16-Bit CMOS Parallel Multiplier Accumulator | 2-10 |

| HMU16/HMU17 | 16 x 16-Bit CMOS Parallel Multipliers            | 2-15 |

| HMU16/883   | 16 x 16-Bit CMOS Parallel Multiplier             | 2-25 |

| HMU17/883   | 16 x 16-Bit CMOS Parallel Multiplier             | 2-31 |

# **HMA510**

# 16 x 16-Bit CMOS Parallel Multiplier Accumulator

#### August 1992

Features

#### 16 x 16-bit Parallel Multiplication with Accumulation to a 35-Bit Result

- High-Speed (45ns) Multiply Accumulate Time

- Low Power CMOS Operation:

- ► ICCSB = 500µA Maximum

- ► ICCOP = 7.0mA Maximum @ 1.0MHz

- HMA510 is Compatible with the CY7C510 and the IDT7210

- Supports Two's Complement or Unsigned Magnitude Operations

- TTL Compatible Inputs/Outputs

- Three-State Outputs

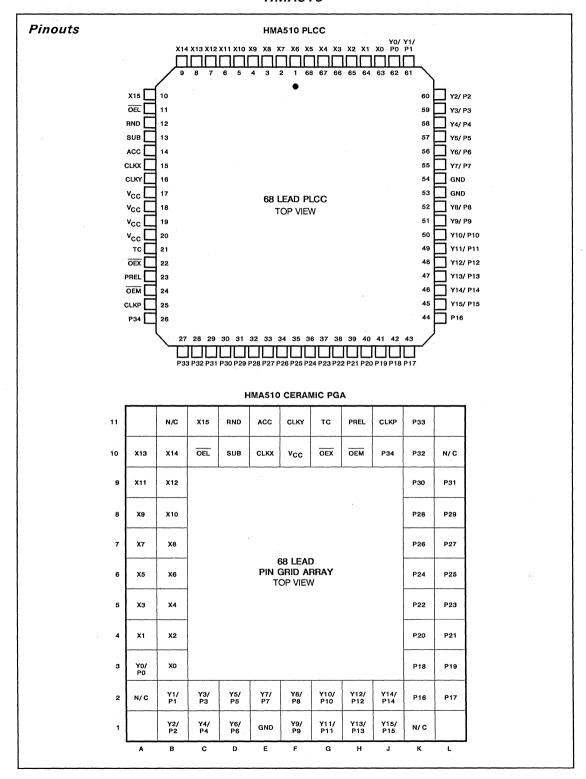

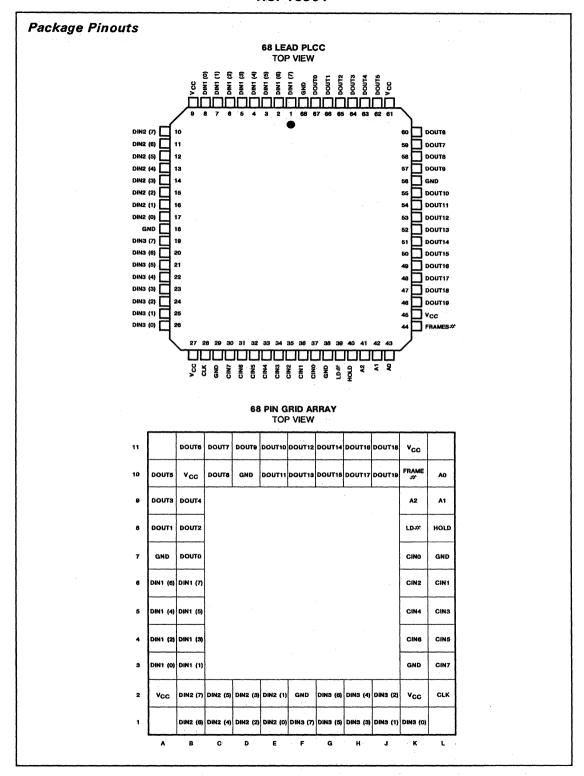

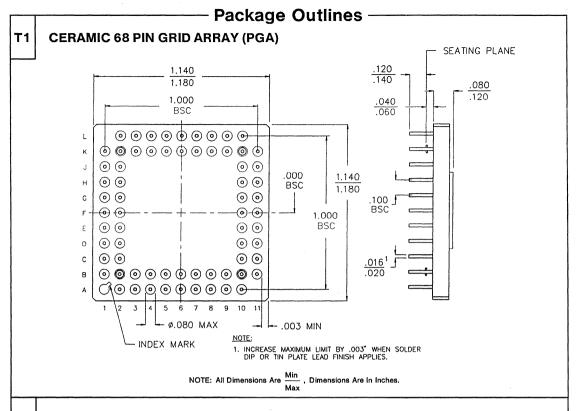

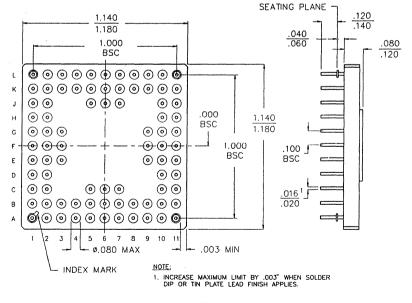

- Available in 68 Pin Plastic Leaded Chip Carrier (PLCC) and 68 Lead Pin Grid Array (PGA)

#### Description

The HMA510 is a high speed, low power CMOS 16 x 16-bit parallel multiplier accumulator capable of operating at 45ns clocked multiply-accumulate cycles. The 16-bit X and Y operands may be specified as either two's complement or unsigned magnitude format. Additional inputs are provided for the accumulator functions which include: loading the accumulator with the current product, adding or subtracting the accumulator contents and the current product, and preloading the accumulator registers from the external inputs.

All inputs and outputs are registered. The registers are all positive edge triggered, and are latched on the rising edge of the associated clock signal. The 35-bit accumulator output register is broken into three parts. The 16-bit least significant product (LSP), the 16-bit most significant product (MSP), and the 3-bit extended product (XTP) registers. The XTP and MSP registers have dedicated output ports, while the LSP register shares the Y-inputs in a multiplexed fashion. The entire 35-bit accumulator output register may be preloaded at any time through the use of the bidirectional output ports and the preloaded control.

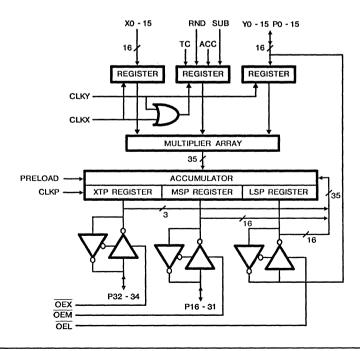

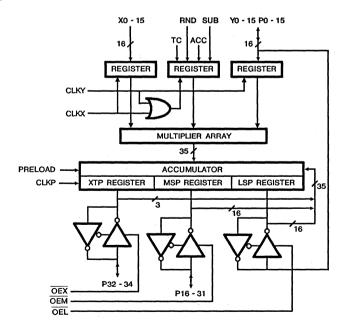

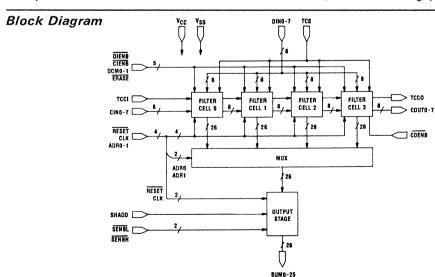

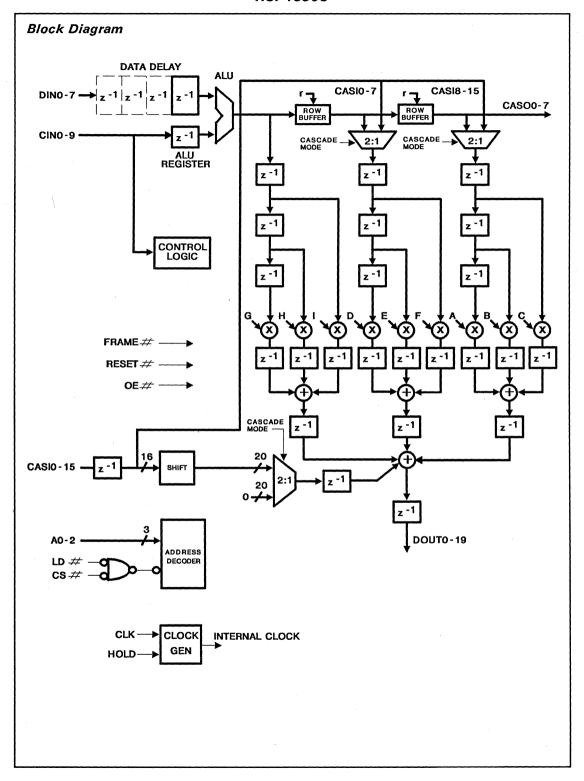

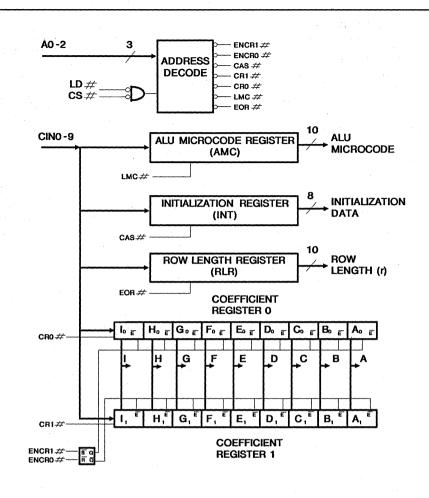

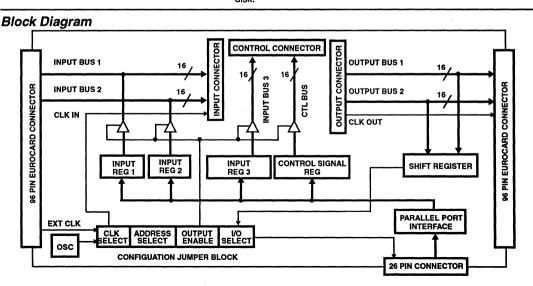

#### Block Diagram

#### Pin Descriptions

| NAME              | PLCC<br>PIN NUMBER | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                    |

|-------------------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc               | 17-20              |      | The +5V power supply pins. $0.1\mu\text{F}$ capacitors between the $V_{\mbox{CC}}$ and GND pins are recommended.                                                                                                                                                                                                               |

| GND               | 53,54              |      | The device ground.                                                                                                                                                                                                                                                                                                             |

| X0-X15            | 1-10,63-68         | ı    | X-Input Data. These 16 data inputs provide the multiplicand which may be in two's complement or unsigned magnitude format.                                                                                                                                                                                                     |

| Y0-Y15/<br>P0-P15 | 45-52, 55-62       | I/O  | Y-Input/LSP Output Data. This 16-bit port is used to provide the multiplier which may be in two's complement or unsigned magnitude format. It may also be used for output of the Least Significant Product (P0-P15) or for preloading the LSP register.                                                                        |

| P16-P3            | 29-44              | 1/0  | MSP Output Data. This 16-Bit port is used to provide the Most Significant Product Output (P16-P31). It may also be used to preload the MSP register.                                                                                                                                                                           |

| P32-P34           | 26-28              | I/O  | XTP Output Data. This 3-Bit port is used to provide the Extended Product Output (P32-P34). It may also be used to preload the XTP register.                                                                                                                                                                                    |

| TC                | 21                 | 1    | Two's Complement Control. Input data is interpreted as two's complement when this control is HIGH. A LOW indicates the data is to be interpreted as unsigned magnitude format. This control is latched on the rising edge of CLKX or CLKY.                                                                                     |

| ACC               | 14                 | 1    | Accumulate Control. When this control is HIGH, the accumulator output register contents are added to or subtracted from the current product, and the result is stored back into the accumulator output register.                                                                                                               |

|                   |                    |      | When LOW, the product is loaded into the accumulator output register overwriting the current contents. This control is also latched on the rising edge of CLKX or CLKY.                                                                                                                                                        |

| SUB               | 13                 | l    | Subtract Control. When both SUB and ACC are HIGH, the accumulator register contents are subtracted from the current product. When ACC is HIGH and SUB is LOW, the accumulator register contents and the current product are summed. The SUB control input is latched on the rising edge of CLKX or CLKY.                       |

| RND               | 12                 | l    | Round Control. When this control is HIGH, a one is added to the most significant bit of the LSP. When LOW, the product is unchanged.                                                                                                                                                                                           |

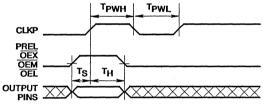

| PREL              | 23                 | 1    | Preload Control. When this control is HIGH, the three bidirectional ports may be used to preload the accumulator registers. The three-state controls (OEX, OEM, OEL) must be HIGH, and the data will be preloaded on the rising edge of CLKP. When this control is LOW, the accumulator registers function in a normal manner. |

| ŌĒĹ               | 11                 | ı    | Y-Input/LSP Output Port Three-state Control. When $\overline{\text{OEL}}$ is HIGH, the output drivers are in the high impedance state. This state is required for Y-data input or preloading the LSP register. When $\overline{\text{OEL}}$ is LOW, the port is enabled for LSP output.                                        |

| ŌĒM               | 24                 | 1    | MSP Output Port Three-state Control. A LOW on this control line enables the port for output. When OEM is HIGH, the output drivers are in the high impedance state. This control must be HIGH for preloading the MSP register.                                                                                                  |

| ŌEX               | 22                 | ı    | XTP Output Port Three-state Control. A LOW on this control line enables the port for output. When OEX is HIGH, the output drivers are in the high impedance state. This control must be HIGH for preloading the XTP register.                                                                                                  |

| CLKX              | 15                 | I    | X-Register Clock. The rising edge of this clock latches the X-data input register along with the TC, ACC, SUB and RND inputs.                                                                                                                                                                                                  |

| CLKY              | 16                 | I    | Y-Register Clock. The rising edge of this clock latches the Y-data input register along with the TC, ACC, SUB and RND inputs.                                                                                                                                                                                                  |

| CLKP              | 25                 | I    | Product Register Clock. The rising edge of CLKP latches the LSP, MSP and XTP registers. If the preload control is active, the data on the I/O ports is loaded into these registers. If preload is not active, the accumulated product is loaded into the the registers.                                                        |

#### Functional Description

The HMA510 is a high speed 16 x 16-bit multiplier accumulator (MAC). It consists of a 16-bit parallel multiplier follower by a 35-bit accumulator. All inputs and outputs are registered and are latched on the rising edge of the associated clock signal. The HMA510 is divided into four sections: the input section, the multiplier array, the accumulator and the output/preload section.

The input section has two 16-bit operand input registers for the X and Y operands which are latched on the rising edge of CLKX and CLKY respectively. A four bit control register (TC, RND, ACC, SUB) is also included and is latched from either of the input clock signals.

The 16 x 16 multiplier array produces the 32-bit product of the input operands. Two's complement or unsigned magnitude operation can be selected by the use of the TC control. The 32-bit result may also be rounded through the use of the RND control. In this case, a '1' is added to the MSB of the LSP (bit P15). The 32-bit product is zero-filled or sign-extened as appropriate and passed as a 35-bit number to the accumulator section.

The accumulator functions are controlled by the ACC, SUB and PREL control inputs. Four functions may be selected: the accumulator may be loaded with the current product; the product may be added to the accumulator contents; the accumulator contents may be subtracted from the current product; or the accumulator may be loaded from the bidirectional ports. The accumulator registers are updated at the rising edge of the CLKP signal.

The output/preload section contains the accumulator/output register and the bidirectional ports. This section is controlled by the signals PREL,  $\overline{OEX}$ ,  $\overline{OEM}$  and  $\overline{OEL}$ . When PREL is high, the output buffers are in a high impedance state. When one of the controls  $\overline{OEX}$ ,  $\overline{OEM}$  or  $\overline{OEL}$  are also high, data present at the outputs will be preloaded into the associated register on the rising edge of CLKP. When PREL is low, the signals  $\overline{OEX}$ ,  $\overline{OEM}$  and  $\overline{OEL}$  are enable controls for their respective three-state output ports.

#### PRELOAD FUNCTION TABLE

|      |     |     |     | OUTP | UT REGIS | TERS |

|------|-----|-----|-----|------|----------|------|

| PREL | OEX | OEM | OEL | XTP  | MSP      | LSP  |

| 0    | 0   | 0   | 0   | Q    | Q        | Q    |

| 0    | 0   | 0   | 1   | Q    | Q        | Z    |

| 0    | 0   | 1   | 0   | Q    | z        | Q    |

| 0    | 0   | 1   | 1   | Q    | z        | Z    |

| 0    | 1   | 0   | 0   | z    | Q        | Q    |

| 0    | 1   | 0   | 1   | z    | Q        | Z    |

| 0    | 1   | 1   | 0   | z    | z        | Q    |

| 0    | 1   | 1   | 1   | z    | z        | Z    |

| 1    | 0   | 0   | 0   | z    | z        | Z    |

| 1    | 0   | 0   | 1   | z    | z        | PL   |

| 1    | 0   | 7   | 0   | z    | PL       | Z    |

| 1    | 0   | 1   | 1   | z    | PL       | PL   |

| 1    | 1   | 0   | 0   | PL   | z        | Z    |

| 1    | 1   | 0   | 1   | PL   | z        | PL   |

| 1    | 1   | 1   | 0   | PL   | PL       | Z    |

| 1.   | 1   | 1   | 1   | PL   | PL       | PL   |

- Z = Output Buffers at High Impedance (Disabled).

- Q = Output Buffers at LOW Impedance. Contents of Output Register Available Through Output Ports.

- PL = Output disabled. Preload data supplied to the output pins will be loaded into the register at the rising edge of CLKP.

#### **ACCUMULATOR FUNCTION TABLE**

| PREL | ACC | SUB | P  | OPERATION |

|------|-----|-----|----|-----------|

| L    | L   | Х   | Q  | Load      |

| L    | Н   | L   | Q  | Add       |

| L    | Н   | Н   | Q  | Subtract  |

| Н    | х   | х   | PL | Preload   |

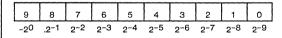

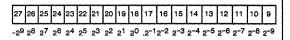

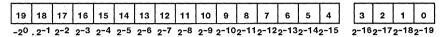

#### INPUT FORMATS Fractional Two's Complement Input

|      |     |     |     |     |     |     | X   |     |     |      |      |      |      |        |      |      |     |     |     |     |     |     | Y   |     |     |      |      |      |      |      |      |

|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|--------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|

| 15   | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5    | 4    | 3    | 2    | 1      | 0    | 15   | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5    | 4    | 3    | 2    | 1    | 0    |

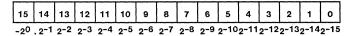

| -20  | 2-1 | 2-2 | 2-3 | 2-4 | 2-5 | 2-6 | 2-7 | 2-8 | 2-9 | 2-10 | 2-11 | 2-12 | 2-13 | 2-14 2 | 2-15 | -20  | 2-1 | 2-2 | 2-3 | 2-4 | 2-5 | 2-6 | 2-7 | 2-8 | 2-9 | 2-10 | 2-11 | 2-12 | 2-13 | 2-14 | 2-15 |

| (Sig | n)  |     |     |     |     |     |     |     |     |      |      |      |      |        |      | (Sig | (n) |     |     |     |     |     |     |     |     |      |      |      |      |      |      |

#### Integer Two's Complement Input

|       |     |     |     |     |     |    | X  |    |    |    |    |    |    |    | _  |      |     | _   |     |     |     |    | Y  |    |    |    |    |    |    |    |    |

|-------|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 15    | 14  | 13  | 12  | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  | 15   | 14  | 13  | 12  | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| -215  | 214 | 213 | 212 | 211 | 210 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | -215 | 214 | 213 | 212 | 211 | 210 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 |

| (Sign | 1)  |     |     |     |     |    |    |    |    |    |    |    |    |    |    | (Sig | n)  |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

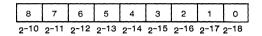

#### **Unsigned Fractional Input**

|     |     |     |     |     |     |     |     |     |      |      |      |      |      |      |      |     |     |     |     |     |     |     | 1   |     |      |      |      |      |      |      |      |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6    | 5    | 4    | 3    | 2    | 1    | 0    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| 2-1 | 2-2 | 2-3 | 2-4 | 2-5 | 2-6 | 2-7 | 2-8 | 2-9 | 2-10 | 2-11 | 2-12 | 2-13 | 2-14 | 2-15 | 2-16 | 2-1 | 2-2 | 2-3 | 2-4 | 2-5 | 2-6 | 2-7 | 2-8 | 2-9 | 2-10 | 2-11 | 2-12 | 2-13 | 2-14 | 2-15 | 2-16 |

#### **Unsigned Integer Input**

|     |     |     |     |     |     |    | X  |    |    |    |    |    |    |    |    |   |     |     |     |     |     |     |    | Y  |    |    |    |    |    |    |    |    |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |   | 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| 215 | 214 | 213 | 212 | 211 | 210 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | - | 215 | 214 | 213 | 212 | 211 | 210 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 |

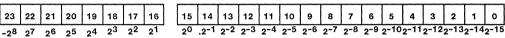

## OUTPUT FORMATS Two's Complement Fractional Output

| XTP       |    |       |      |      |       |       |     | M   | SP  |     |      |      |      |      |      |      |      |      |      |      |      |      | LS   | SP   |      |      |      |      |      |      |      |

|-----------|----|-------|------|------|-------|-------|-----|-----|-----|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 34 33 32  | 31 | 30 2  | 9 28 | 3 27 | 26    | 25    | 24  | 23  | 22  | 21  | 20   | 19   | 18   | 17   | 16   | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| -24 23 22 | 21 | 20 2- | 1 2- | 2 2- | 3 2-4 | 1 2-5 | 2-6 | 2-7 | 2-8 | 2-9 | 2-10 | 2-11 | 2-12 | 2-13 | 2-14 | 2-15 | 2-16 | 2-17 | 2-18 | 2-19 | 2-20 | 2-21 | 2-22 | 2-23 | 2-24 | 2-25 | 2-26 | 2-27 | 2-28 | 2-29 | 2-30 |

| (Sign)    |    |       |      |      |       |       |     |     |     |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

#### Two's Complement Integer Output

| XTP          | MSP                                                             | LSP                                                   |

|--------------|-----------------------------------------------------------------|-------------------------------------------------------|

| 34 33 32     | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16                 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                 |

| -234 233 232 | 231 230 229 228 227 226 225 224 223 222 221 220 219 218 217 216 | 215 214 213 212 211 210 29 28 27 26 25 24 23 22 21 20 |

| (Sign)       |                                                                 |                                                       |

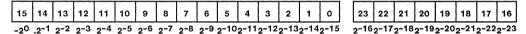

|            | Onsigned Fractional Output    |                            |                                     |                                       |                            |  |  |  |  |  |  |  |  |  |

|------------|-------------------------------|----------------------------|-------------------------------------|---------------------------------------|----------------------------|--|--|--|--|--|--|--|--|--|

| XTP        |                               | MSP                        |                                     | LSP                                   |                            |  |  |  |  |  |  |  |  |  |

| 34 33 32 3 | 31 30 29 28 27 26 25 24       | 4 23 22 21 20 19           | 18 17 16 15 14 13 12                | 2 11 10 9 8 7 6 5                     | 4 3 2 1 0                  |  |  |  |  |  |  |  |  |  |

| 22 21 20 2 | -1 2-2 2-3 2-4 2-5 2-6 2-7 2- | -8 2-9 2-10 2-11 2-12 2-13 | 3 2-14 2-15 2-16 2-17 2-18 2-19 2-1 | 20 2-21 2-22 2-23 2-24 2-25 2-26 2-27 | 7 2-28 2-29 2-30 2-31 2-32 |  |  |  |  |  |  |  |  |  |

|             | Unsigned Integer Output     |                                     |                                                       |  |  |  |  |  |  |  |  |  |

|-------------|-----------------------------|-------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| XTP         |                             | MSP                                 | LSP                                                   |  |  |  |  |  |  |  |  |  |

| 34 33 32    | 31 30 29 28 27 26 25        | 24 23 22 21 20 19 18 17 16          | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                 |  |  |  |  |  |  |  |  |  |

| -24 -22 -22 | -21 -20 -20 -22 -27 -27 -25 | 224 222 222 221 220 210 219 217 216 | 215 214 213 213 211 210 20 28 27 26 25 24 23 23 21 20 |  |  |  |  |  |  |  |  |  |

#### Specifications HMA510

#### Absolute Maximum Ratings

| - 1200 in                                   |

|---------------------------------------------------------------------------------|

| Supply Voltage                                                                  |

| Input, Output or I/O Voltage Applied $\dots$ GND -0.5V to V <sub>CC</sub> +0.5V |

| Storage Temperature Range65°C to +150°C                                         |

| Gate Count 4800 Gates                                                           |

| Junction Temperature 150°C (PLCC), +175°C (PGA)                                 |

| Lead Temperature (Soldering, Ten Seconds)+300°C                                 |

| ESD Classification                                                              |

#### **Operating Conditions**

| Operating Voltage Range     | +4.75V to +5.25V |

|-----------------------------|------------------|

| Operating Temperature Range | 0°C to +70°C     |

#### Reliability Information

θjc ...... 15.1°C/W (PLCC), 10.0°C/W (PGA) Maximum Package Power Dissipation at 70°C . . . . . 1.7W (PLCC) 2.46/W (PGA)

#### **D.C. Electrical Specifications** ( $V_{CC} = 5.0V \pm 5\%$ , $T_A = 0^{\circ}C$ to $+70^{\circ}C$ )

| PARAMETER                      | SYMBOL | MIN | MAX | UNITS | TEST CONDITIONS                                                                          |

|--------------------------------|--------|-----|-----|-------|------------------------------------------------------------------------------------------|

| Logical One Input Voltage      | VIH    | 2.0 | -   | ٧     | V <sub>CC</sub> = 5.25V                                                                  |

| Logical Zero Input Voltage     | VIL    | -   | 0.8 | ٧     | V <sub>CC</sub> = 4.75V                                                                  |

| Output HIGH Voltage            | VOH    | 2.6 | _   | V     | I <sub>OH</sub> = -400μA, V <sub>CC</sub> = 4.75V                                        |

| Output LOW Voltage             | VOL    | -   | 0.4 | V     | I <sub>OL</sub> = +4.0mA, V <sub>CC</sub> = 4.75V                                        |

| Input Leakage Current          | I      | -10 | 10  | μА    | $V_{IN} = V_{CC}$ or GND, $V_{CC} = 5.25V$                                               |

| Output or I/O Leakage Current  | lo     | -10 | 10  | μА    | V <sub>OUT</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.25V                       |

| Standby Power Supply Current   | Iccsb  | _   | 500 | μА    | $V_{IN} = V_{CC}$ or GND, $V_{CC} = 5.25V$ , Outputs Open                                |

| Operating Power Supply Current | Іссор  | -   | 7.0 | mA    | f = 1.0MHz, V <sub>IN</sub> = V <sub>CC</sub> or GND<br>V <sub>CC</sub> = 5.25V (Note 1) |

#### Capacitance (T<sub>A</sub> = +25°C, Note 2)

| PARAMETER          | SYMBOL           | MIN | MAX | UNITS | TEST CONDITIONS                                      |

|--------------------|------------------|-----|-----|-------|------------------------------------------------------|

| Input Capacitance  | CIN              | -   | 10  | pF    | FREQ = 1MHz, V <sub>CC</sub> = Open all Measurements |

| Output Capacitance | C <sub>QUT</sub> | -   | 10  | pF    | are Referenced to Device Ground.                     |

| I/O Capacitance    | C <sub>I/O</sub> | -   | 15  | pF    |                                                      |

#### NOTES:

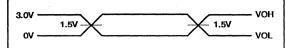

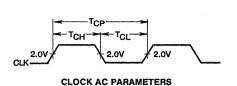

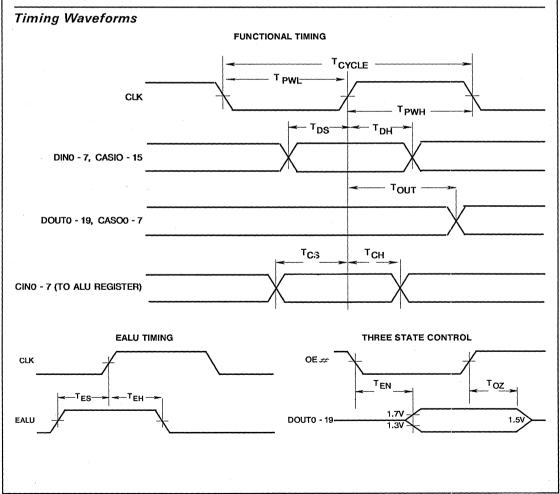

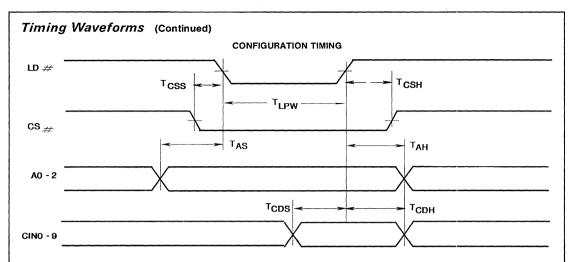

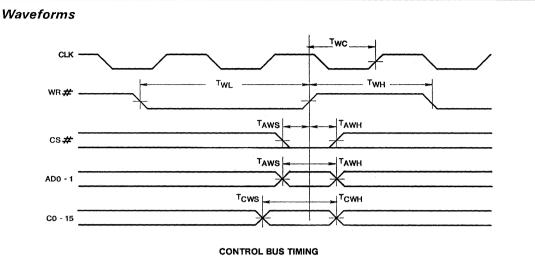

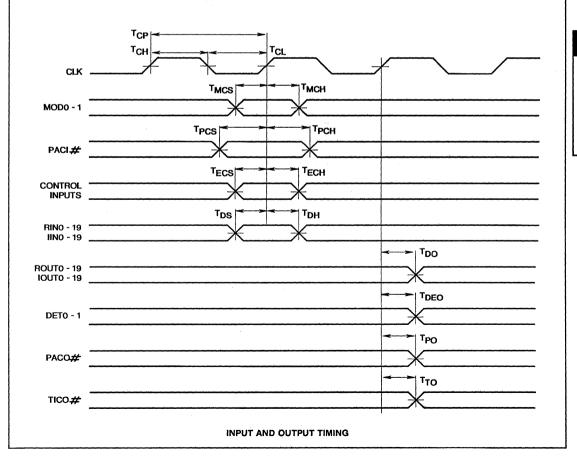

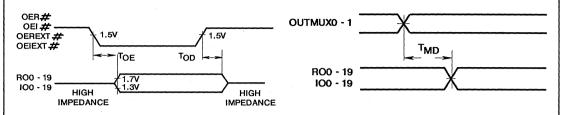

#### A.C. Electrical Specifications ( $V_{CC} = 5.0V \pm 5\%$ , $T_A = 0^{\circ}C$ to $\pm 70^{\circ}C$ )

|                          |                  | HMA5 | 10-45 | HMA510-55 |     |       | ,                 |

|--------------------------|------------------|------|-------|-----------|-----|-------|-------------------|

| PARAMETER                | SYMBOL           | MIN  | MAX   | MIN       | MAX | UNITS | TEST CONDITIONS   |

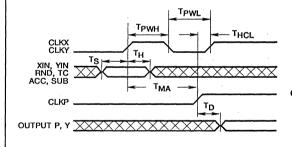

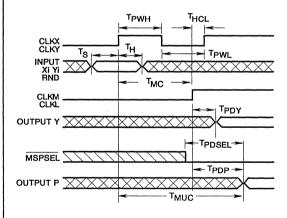

| Multiply Accumulate Time | T <sub>MA</sub>  | -    | 45    | -         | 55  | ns    |                   |

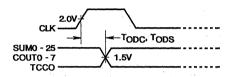

| Output Delay             | TD               | -    | 25    | -         | 30  | ns    |                   |

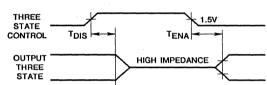

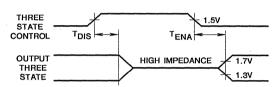

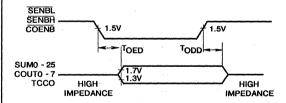

| 3-State Enable Time      | TENA             | -    | 25    | -         | 30  | ns    | Note 1            |

| 3-State Disable Time     | TDIS             | -    | 25    | -         | 30  | ns    | Note 1            |

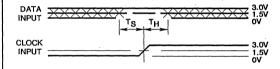

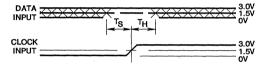

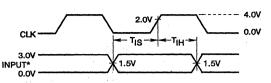

| Input Setup Time         | TS               | 18   | -     | 20        | -   | ns    | :                 |

| Input Hold Time          | TH               | 2    | -     | 2         | -   | ns    |                   |

| Clock High Pulse Width   | TPWH             | 15   | -     | 20        | -   | ns    |                   |

| Clock Low Pulse Width    | T <sub>PWL</sub> | 15   | -     | 20        | -   | ns    |                   |

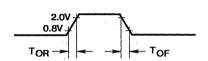

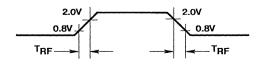

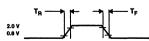

| Output Rise Time         | TR               | -    | 8     | -         | 8   | ns    | From 0.8V to 2.0V |

| Output Fall Time         | TF               | -    | 8     | -         | 8   | ns    | From 2.0V to 0.8V |

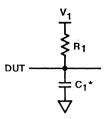

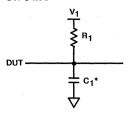

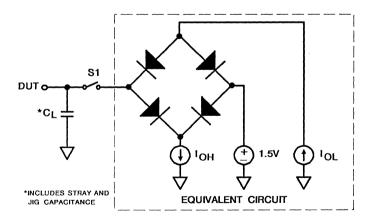

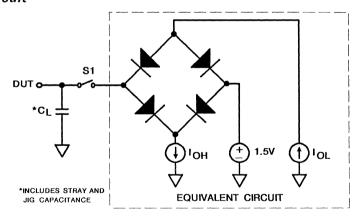

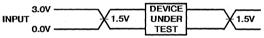

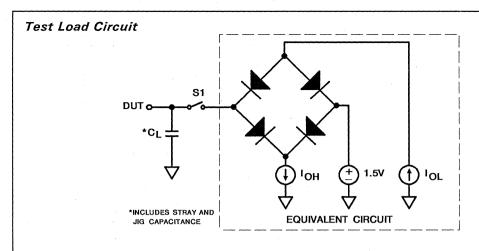

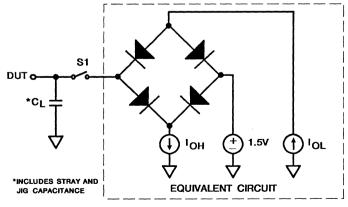

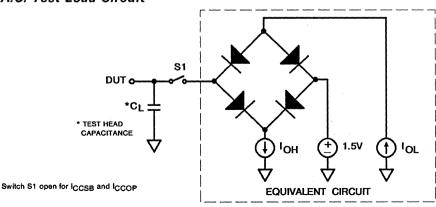

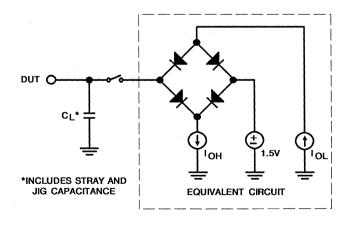

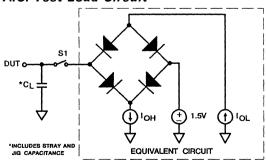

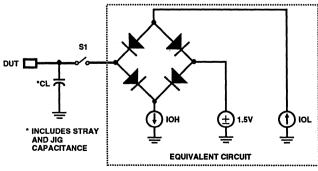

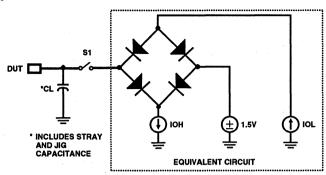

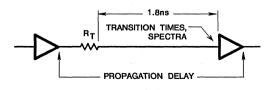

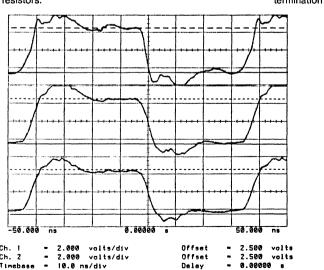

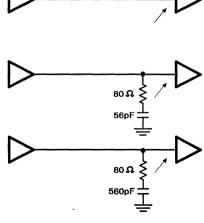

<sup>1.</sup> Operating Supply Current is proportional to frequency, typical rating is 2. Not tested, but characterized at initial design and at major process/design

<sup>1.</sup> Transition is measured at ±200mV from steady state voltage with loading 2. For A.C. Test load, refer to A.C. Test Circuit with V<sub>1</sub> = 2.4V, R<sub>1</sub> = 500Ω specified in A.C. Test Circuit; V  $_1$  = 1.5V, R  $_1$  = 500  $\Omega$  and C  $_L$  = 40pF.

and  $C_L = 40pF$ .

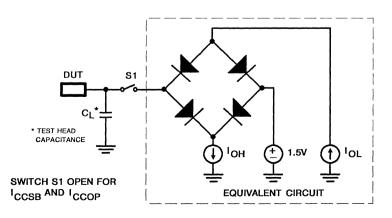

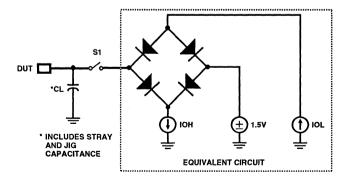

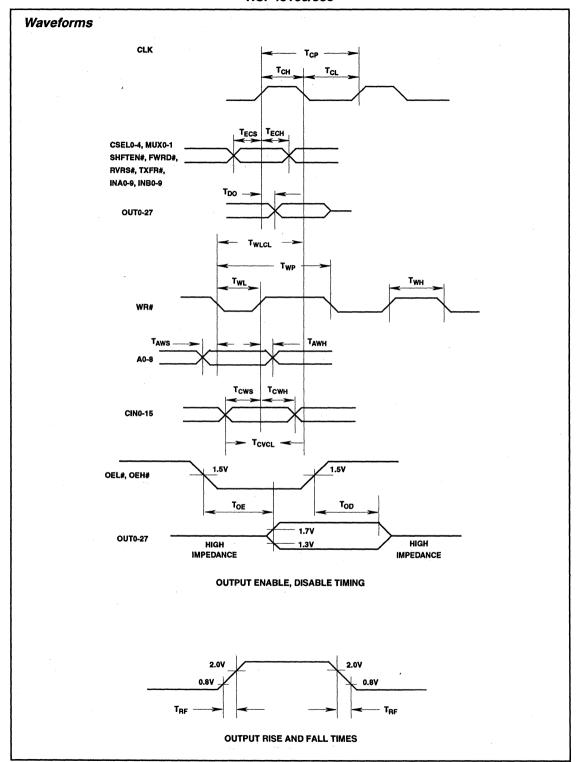

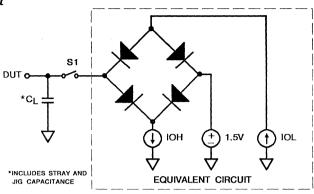

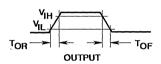

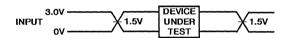

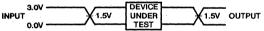

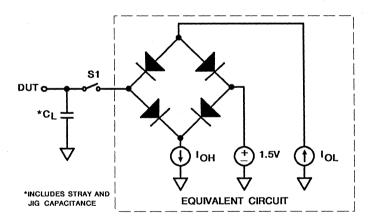

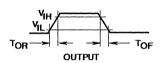

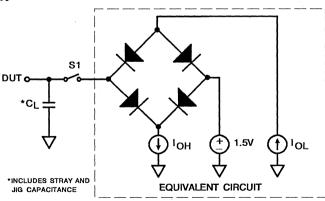

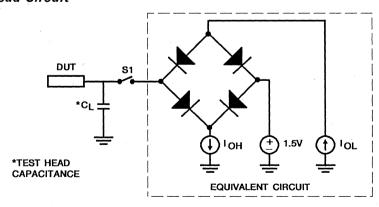

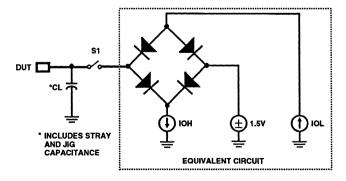

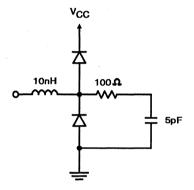

#### A.C. Test Circuit

\*Includes Stray and Jig Capacitance

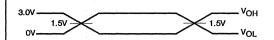

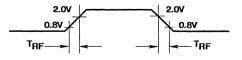

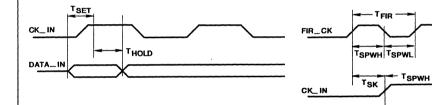

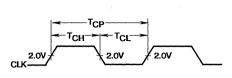

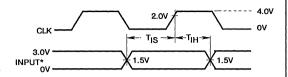

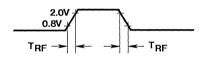

#### A.C. Testing Input, Output Waveforms

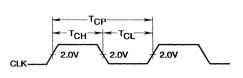

A.C. Testing: All Parameters tested as per test circuit.

Input rise and fall times are driven at 1ns/V.

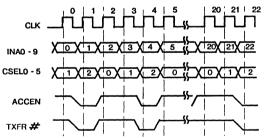

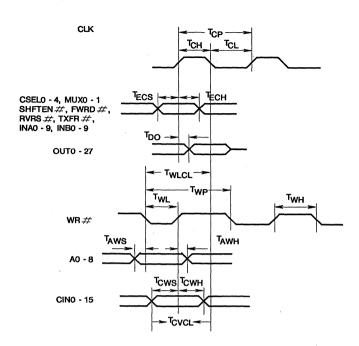

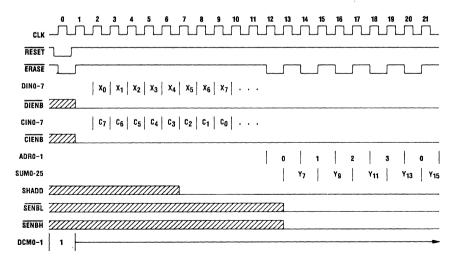

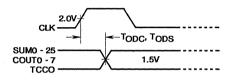

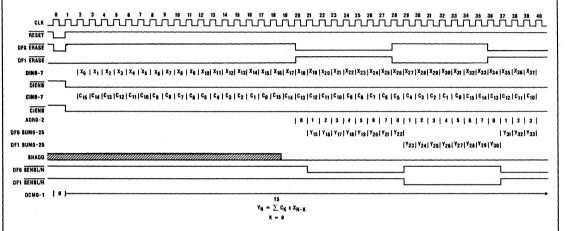

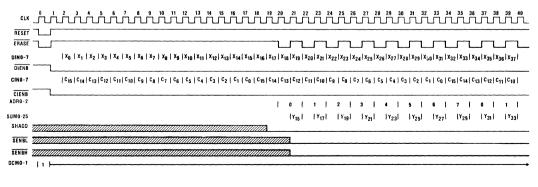

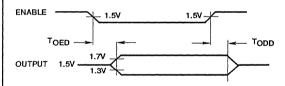

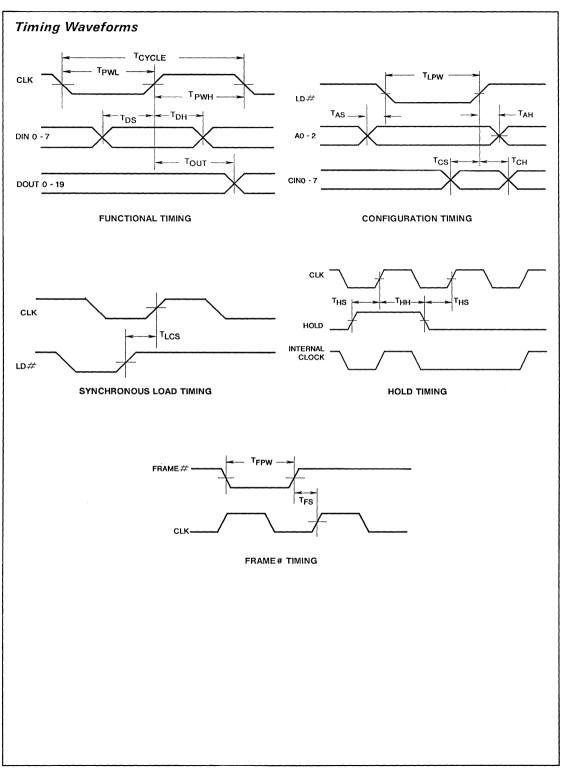

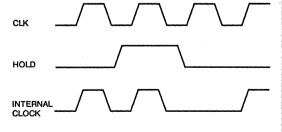

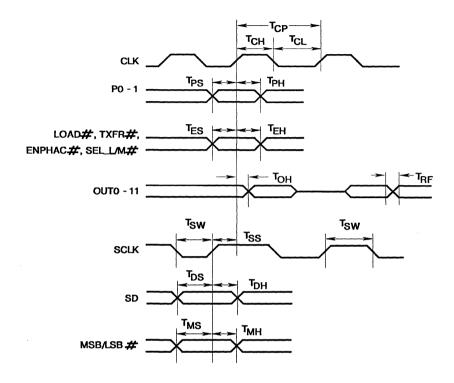

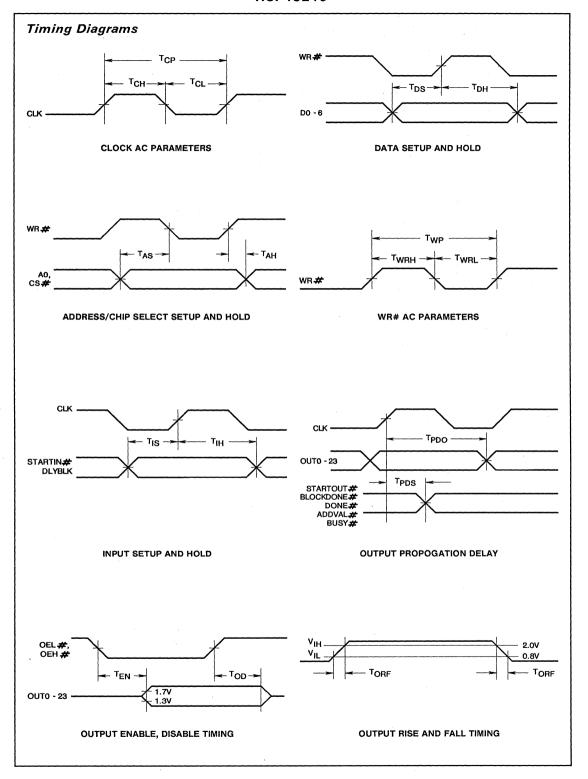

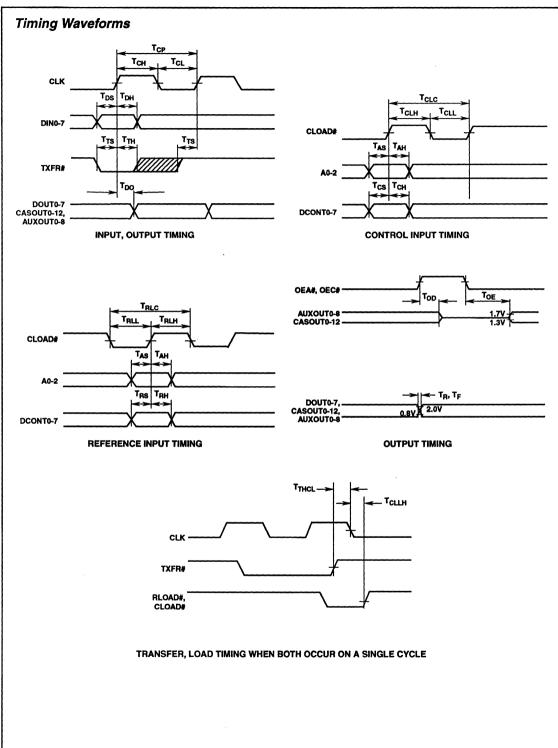

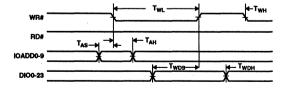

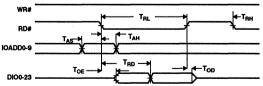

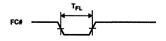

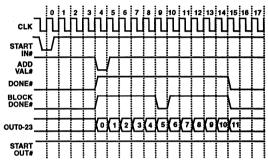

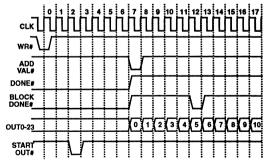

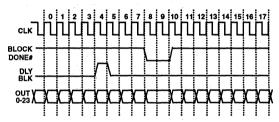

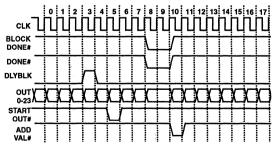

#### Timing Diagram

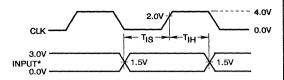

#### SET-UP AND HOLD TIME

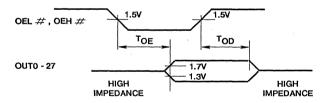

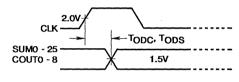

#### THREE STATE CONTROL

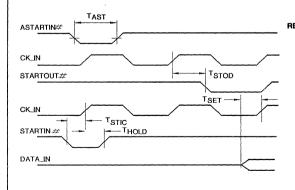

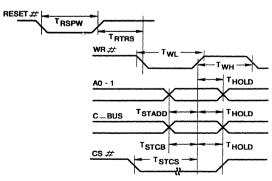

#### HMA510 TIMING DIAGRAM

#### PRELOAD TIMING DIAGRAM

# HMA510/883

August 1992

16 x 16-Bit CMOS Parallel Multiplier Accumulator

#### Features

- This Circuit is Processed in Accordance to Mil-Std-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- 16 x 16-bit Parallel Multiplication with Accummulation to a 35-Bit Result

- High-Speed (55ns) Multiply Accumulate Time

- Low Power CMOS Operation:

- ► ICCSB = 500µA Maximum

- ► ICCOP = 7.0mA Maximum @ 1.0MHz

- HMA510/883 is Compatible with the CY7C510 and the IDT7210

- Supports Two's Complement or Unsigned Magnitude Operations

- TTL Compatible Inputs/Outputs

- Three-State Outputs

- Available in 68 Lead Pin Grid Array (PGA) Package

#### Description

The HMA510/883 is a high speed, low power CMOS  $16 \times 16$ -bit parallel multiplier accumulator capable of operating at 55ns clocked multiply-accumulate cycles. The 16-bit X and Y operands may be specified as either two's complement or unsigned magnitude format. Additional inputs are provided for the accumulator functions which include: loading the accumulator with the current product, adding or subtracting the accumulator contents and the current product, and preloading the accumulator registers from the external inputs.

All inputs and outputs are registered. The registers are all positive edge triggered, and are latched on the rising edge of the associated clock signal. The 35-bit accumulator output register is broken into three parts. The 16-bit least significant product (LSP), the 16-bit most significant product (MSP), and the 3-bit extended product (XTP) registers. The XTP and MSP registers have dedicated output ports, while the LSP register shares the Y-inputs in a multiplexed fashion. The entire 35-bit accumulator output register may be preloaded at any time through the use of the bidirectional output ports and the preloaded control.

#### **Block Diagram**

#### Specifications HMA510/883

# Absolute Maximum Ratings Reliability Information Supply Voltage +8.0V Input or Output Voltage Applied GND-0.5V to V<sub>CC</sub>+0.5V Storage Temperature Range -65°C to +150°C Junction Temperature +175°C Lead Temperature (Soldering 10 sec) 300°C ESD Classification Class 1

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Operating Conditions**

Operating Voltage Range .....+4.5V to +5.5V Operating Temperature Range .....-55°C to +125°C

#### TABLE 1. HMA510/883 D.C. ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Guaranteed and 100% Tested

|                                   |                |                                                                                            | GROUP A   |                                 | LIM |     |       |

|-----------------------------------|----------------|--------------------------------------------------------------------------------------------|-----------|---------------------------------|-----|-----|-------|

| PARAMETER                         | SYMBOL         | CONDITIONS                                                                                 | SUBGROUPS | TEMPERATURE                     | MIN | MAX | UNITS |

| Logical One Input<br>Voltage      | VIH            | V <sub>CC</sub> = 5.5V                                                                     | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C | 2.2 | -   | V     |

| Logical Zero Input<br>Voltage     | VIL            | V <sub>CC</sub> = 4.5V                                                                     | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C | -   | 0.8 | V     |

| Output HIGH Voltage               | VOH            | I <sub>OH</sub> = -400μA<br>V <sub>CC</sub> = 4.5V (Note 1)                                | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C | 2.6 | -   | V     |

| Output LOW Voltage                | VOL            | I <sub>OL</sub> = +4.0mA<br>V <sub>CC</sub> = 4.5V (Note 1)                                | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C | -   | 0.4 | V     |

| Input Leakage Current             | l <sub>į</sub> | $V_{IN} = V_{CC}$ or GND<br>$V_{CC} = 5.5V$                                                | 1, 2, 3   | -55°C ≤T <sub>A</sub> ≤ +125°C  | -10 | +10 | μА    |

| Output or I/O Leakage<br>Current  | ю              | V <sub>OUT</sub> = V <sub>CC</sub> or GND<br>V <sub>CC</sub> = 5.5V                        | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C | -10 | +10 | μА    |

| Standby Power Supply<br>Current   | ICCSB          | $V_{IN} = V_{CC}$ or GND,<br>$V_{CC} = 5.5V$ , Outputs<br>Open                             | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C | -   | 500 | μА    |

| Operating Power<br>Supply Current | ICCOP          | f = 1.0MHz,<br>V <sub>IN</sub> = V <sub>CC</sub> or GND<br>V <sub>CC</sub> = 5.5V (Note 2) | 1, 2, 3   | -55°C ≤ T <sub>A</sub> ≤ +125°C | -   | 7.0 | mA    |

| Functional Test                   | FT             | (Note 3)                                                                                   | 7,8       | -55°C ≤ T <sub>A</sub> ≤ +125°C | _   | -   |       |

#### NOTES:

- 1. Interchanging of force and sense conditions is permitted.

- Operating Supply Current is proportional to frequency, typical rating is 5mA/MHz.

- 3. Tested as follows: f = 1MHz, V<sub>IH</sub> (clock inputs) = 3.2V, V<sub>IH</sub> (all other inputs) = 2.6V, V<sub>IL</sub> = 0.4V, V<sub>OH</sub>  $\geq$  1.5V, and V<sub>OL</sub>  $\leq$  1.5V.

#### Specifications HMA510/883

TABLE 2. HMA510/883 A.C. ELECTRICAL PERFORMANCE CHARACTERISTICS

Device Guaranteed and 100% Tested

|                             |                  | (NOTE 1)   | GROUP A   |                                                     | -5  | 55  | 6   | 55  | -7  | 75  |       |

|-----------------------------|------------------|------------|-----------|-----------------------------------------------------|-----|-----|-----|-----|-----|-----|-------|

| PARAMETER                   | SYMBOL           | CONDITIONS | SUBGROUPS | TEMPERATURE                                         | MIN | MAX | MIN | MAX | MIN | MAX | UNITS |

| Multiply<br>Accumulate Time | ТМА              |            | 9, 10, 11 | -55°C ≤ T <sub>A</sub> ≤ +125°C                     | -   | 55  | -   | 65  | -   | 75  | ns    |

| Input Setup<br>Time         | TS               |            | 9, 10, 11 | -55°C ≤T <sub>A</sub> ≤ +125°C                      | 20  | -   | 25  | -   | 25  | -   | ns    |

| Clock HIGH<br>Pulse Width   | T <sub>PWH</sub> |            | 9, 10, 11 | -55°C ≤ T <sub>A</sub> ≤ +125°C                     | 20  | -   | 25  | -   | 25  | -   | ns    |

| Clock LOW<br>Pulse Width    | T <sub>PWL</sub> |            | 9, 10, 11 | -55°C ≤ T <sub>A</sub> ≤ +125°C                     | 20  | -   | 25  | -   | 25  | -   | ns    |

| Output Delay                | ТD               |            | 9, 10, 11 | -55°C <u>&lt;</u> T <sub>A</sub> <u>&lt;</u> +125°C | -   | 30  | -   | 35  | -   | 35  | ns    |

| 3-State<br>Enable Time      | TENA             | (Note 2)   | 9, 10, 11 | -55°C <u>&lt;</u> T <sub>A</sub> <u>&lt;</u> +125°C | -   | 30  | -   | 30  | -   | 35  | ns    |

#### NOTES:

TABLE 3. HMA510/883 ELECTRICAL PERFORMANCE CHARACTERISTICS

|                         |                  |                                                   |      |                                                     | -55 |     | -65 |     | -7  |     |       |

|-------------------------|------------------|---------------------------------------------------|------|-----------------------------------------------------|-----|-----|-----|-----|-----|-----|-------|

| PARAMETER               | SYMBOL           | CONDITIONS                                        | NOTE | TEMPERATURE                                         | MIN | MAX | MIN | MAX | MIN | MAX | UNITS |

| Input Capacitance       | C <sub>IN</sub>  | V <sub>CC</sub> = Open,                           | 1    | T <sub>A</sub> = +25°C                              | -   | 10  | -   | 10  | -   | 10  | pF    |

| Output Capacitance      | COUT             | f = 1MHz All<br>measurements are<br>referenced to | 1    | T <sub>A</sub> = +25°C                              | -   | 10  | -   | 10  | -   | 10  | ρF    |

| I/O Capacitance         | CI/O             | device GND.                                       | 1    | T <sub>A</sub> = +25°C                              | -   | 15  | -   | 15  | -   | 15  | pF    |

| Input Hold Time         | T <sub>H</sub>   |                                                   | 1    | -55°C <u>&lt;</u> T <sub>A</sub> <u>&lt;</u> +125°C | 3   | -   | 3   | -   | 3   | -   | ns    |

| 3–State Disable<br>Time | T <sub>DIS</sub> |                                                   | 1    | -55°C <u>&lt;</u> T <sub>A</sub> <u>&lt;</u> +125°C | -   | 30  | -   | 30  | -   | 30  | ns    |

| Output Rise Time        | TR               | From 0.8V to 2.0V                                 | 1    | -55°C ≤ T <sub>A</sub> ≤ +125°C                     | -   | 10  | -   | 10  | -   | 10  | ns    |

| Output Fall Time        | Τ <sub>F</sub>   | From 2.0V to 0.8V                                 | 1    | -55°C <u>&lt;</u> T <sub>A</sub> <u>&lt;</u> +125°C | -   | 10  | -   | 10  | -   | 10  | ns    |

#### NOTE:

**TABLE 4. APPLICABLE SUBGROUPS**

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |

|--------------------|--------------|-------------------------------|

| Initial Test       | 100%/5004    | -                             |

| Interim Test       | 100%/5004    | <del>-</del> .                |

| PDA                | 100%         | 1                             |

| Final Test         | 100%         | 2, 3, 8A, 8B, 10, 11          |

| Group A            | -            | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |

| Groups C & D       | Samples/5005 | 1,7,9                         |

CAUTION: These devices are sensitive to electrostatic discharge. Proper IC handling procedures should be followed.

test load circuit, with  $V_1 = 2.4V$ ,  $R_1 = 500\Omega$  and  $C_L = 40pF$ .

<sup>1.</sup> ACTesting as follows: V<sub>CC</sub> = 4.5V and 5.5V. Input levels 0V and 3.0V (oV and 3.2V for clock inputs). Timing reference levels = 1.5V, Output load per lest load circuit, with V<sub>1</sub> = 1.5V, R<sub>1</sub> = 500Ω and C<sub>L</sub> = 40pF.

<sup>1.</sup> The parameters listed in Table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design and after major process and/or design changes.

#### Burn-In Circuit

| 11 |           | N/C       | X15       | RND       | ACC       | CLKY                          | тс          | PREL        | CLKP        | P33 |     |

|----|-----------|-----------|-----------|-----------|-----------|-------------------------------|-------------|-------------|-------------|-----|-----|

| 10 | X13       | X14       | OEL       | SUB       | CLKX      | v <sub>cc</sub>               | OEX         | ОЕМ         | P34         | P32 | N/C |

| 9  | X11       | X12       |           |           |           |                               |             |             |             | P30 | P31 |

| 8  | Х9        | XIO       |           |           |           |                               |             |             |             | P28 | P29 |

| 7  | Х7        | X8        |           |           |           |                               |             |             |             | P26 | P27 |

| 6  | Х5        | хв        |           |           | PIN (     | 68 LEAI<br>GRID AI<br>OP VIEV | RRAY        |             |             | P24 | P25 |

| 5  | хз        | X4        |           |           |           |                               |             |             |             | P22 | P23 |

| 4  | Х1        | X2        |           |           |           |                               |             |             |             | P20 | P21 |

| 3  | Y0/<br>P0 | хо        |           |           |           |                               |             |             |             | P18 | P19 |

| 2  | N/C       | Y1/<br>P1 | Y3/<br>P3 | Y5/<br>P5 | Y7/<br>P7 | Y8/<br>P8                     | Y10/<br>P10 | Y12/<br>P12 | Y14/<br>P14 | P16 | P17 |

| 1  |           | Y2/<br>P2 | Y4/<br>P4 | Y6/<br>P6 | GND       | Y9/<br>P9                     | Y11/<br>P11 | Y13/<br>P13 | Y15/<br>P15 | N/C |     |

|    |           | 8         | С         | D         | E         | F                             | G           | н           | J           | к   | L   |

| PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL | PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL  | PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL  | PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL |

|------------|-------------|-------------------|------------|-------------|--------------------|------------|-------------|--------------------|------------|-------------|-------------------|

| В6         | X6          | F1                | F1         | Y9/P9       | F2                 | K7         | P26         | V <sub>CC</sub> /2 | E11        | ACC         | F1                |

| A6         | X5          | F2                | G2         | Y10/P10     | F3                 | L7         | P27         | V <sub>CC</sub> /2 | D10        | SUB         | F2                |

| B5         | X4          | F3                | G1         | Y11/P11     | F5                 | К8         | P28         | V <sub>CC</sub> /2 | D11        | RND         | F3                |

| A5         | хз          | F4                | H2         | Y12/P12     | F4                 | L8         | P29         | V <sub>CC</sub> /2 | C10        | OEL         | Vcc               |

| B4         | X2          | F5                | H1         | Y13/P13     | F4                 | К9         | P30         | V <sub>CC</sub> /2 | C11        | X15         | F8                |

| A4         | X1          | F6                | J2         | Y14/P14     | F8                 | L9         | P31         | V <sub>CC</sub> /2 | B10        | X14         | F9                |

| вз         | хо          | F7                | J1         | Y15/P15     | F9                 | K10        | P32         | V <sub>CC</sub> /2 | A10        | X13         | F10               |

| АЗ         | Y0/P0       | F8                | K2         | P16         | V <sub>CC</sub> /2 | K11        | P33         | V <sub>CC</sub> /2 | В9         | X12         | F11               |

| B2         | Y1/P1       | F9                | L2         | P17         | V <sub>CC</sub> /2 | J10        | P34         | V <sub>CC</sub> /2 | A9         | X11         | F12               |

| B1         | Y2/P2       | F10               | КЗ         | P18         | V <sub>CC</sub> /2 | J11        | CLKP        | F0                 | B8         | X10         | F13               |

| C2         | Y3/P3       | F11               | L3         | P19         | V <sub>CC</sub> /2 | H10        | OEM         | GND                | A8         | Х9          | F14               |

| C1         | Y4/P4       | F12               | K4         | P20         | V <sub>CC</sub> /2 | H11        | PREL        | F6                 | B7         | X8          | F15               |

| D2         | Y5/P5       | F13               | L4         | P21         | V <sub>CC</sub> /2 | G10        | OEX         | GND                | A7         | Х7          | F7                |

| D1         | Y6/P6       | F14               | K5         | P22         | V <sub>CC</sub> /2 | G11        | TC          | F5                 | A2         | N.C.        | N.C.              |

| E2         | Y7/P7       | F15               | L5         | P23         | V <sub>CC</sub> /2 | F10        | vcc         | v <sub>cc</sub>    | K1         | N.C.        | N.C.              |

| E1         | GND         | GND               | К6         | P24         | V <sub>CC</sub> /2 | F11        | CLKY        | F0                 | L10        | N.C.        | N.C.              |

| F2         | Y8/P8       | F1                | L6         | P25         | V <sub>CC</sub> /2 | E10        | CLKX        | F0                 | B11        | N.C.        | N.C.              |

#### NOTES:

- 1.  $V_{CC}$  = 5.5V +0.5V/-0.0V with 0.1  $\mu F$  decoupling capacitor to GND

- 2. F0 = 100kHz, F1 = F0/2, F2 = F1/2, . . . . . . , 10%

- 3.  $V_{IH} = V_{CC} 1V \pm 0.5V$  (Min),  $V_{IL} = 0.8V$  (Max)

4.  $47 k\Omega$  load resistors used on all pins except  $V_{\hbox{CC}}$  and GND (Pin-Grid identifiers F10, G10, G11 and H11)

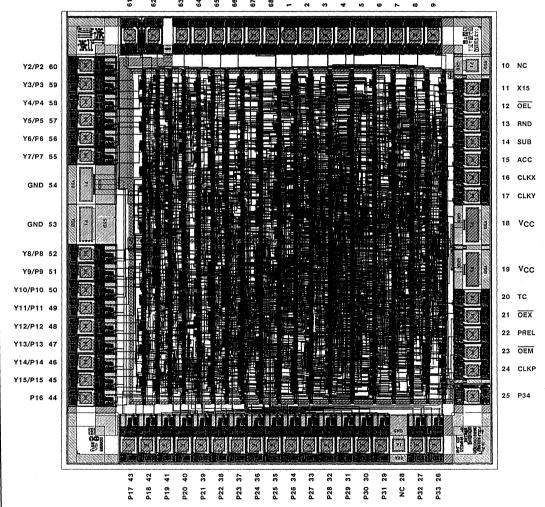

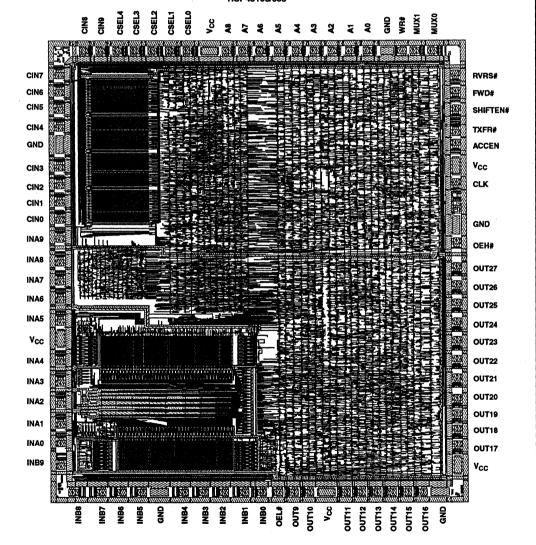

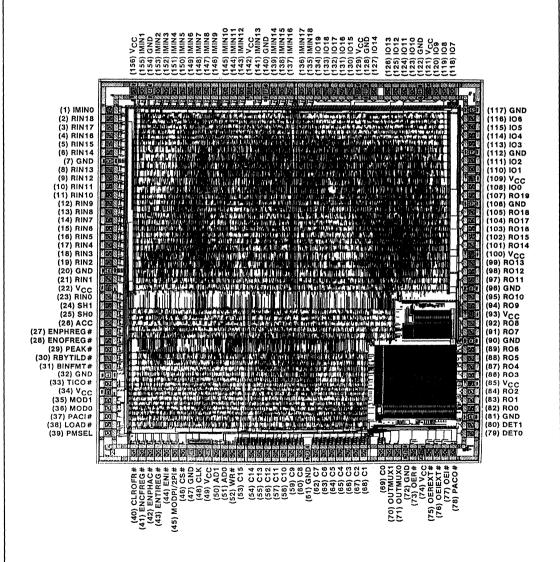

#### Die Characteristics

DIE DIMENSIONS:

$184 \times 176 \times 19 \pm 1 \text{ mils}$

METALLIZATION:

Type: Si-Al or Si-Al-Cu Thickness: 8kÅ

GLASSIVATION:

Type: Nitrox Thickness: 10kÅ

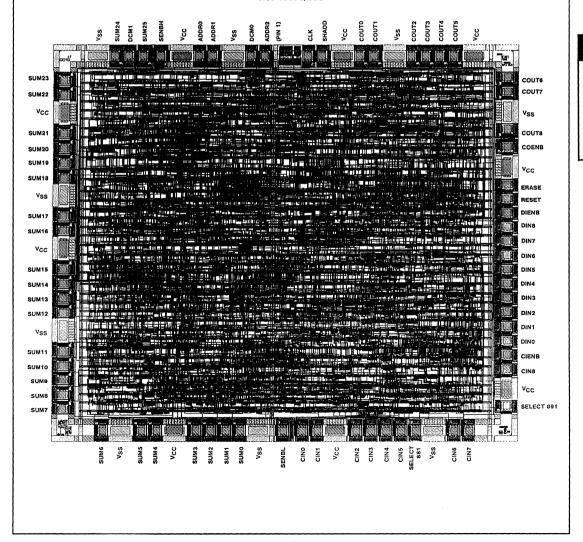

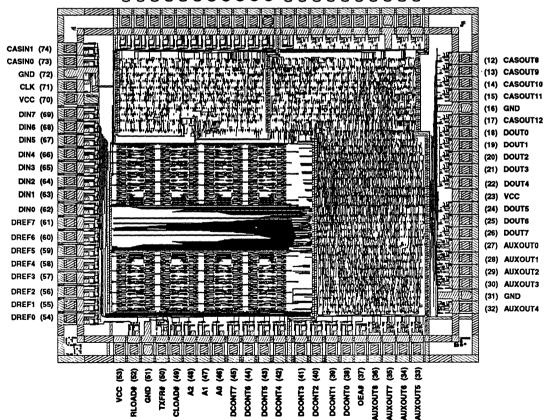

#### Metallization Mask Layout

DIE ATTACH:

Material: Si-Au Eutectic Alloy or Silver-Glass

WORST CASE CURRENT DENSITY: 0.9 x 10<sup>5</sup>A/cm<sup>2</sup>

HMA510/883

61 Y1/P1 62 Y0/P0 64 X1 65 X2 66 X3 67 X4 67 X4 77 X12 87 X13 87 X13 87 X13

# THARRIS HMU16/HMU17

August 1992

# 16 x 16-Bit CMOS Parallel Multipliers

#### Features

- 16 x 16-Bit Parallel Multiplier with Full 32-Bit Product

- High-Speed (35ns) Clocked Multiply Time

- Low Power Operation:

- ► ICCSB = 500µA Maximum

- ► ICCOP = 7.0mA Maximum @ 1MHz

- Supports Two's Complement, Unsigned Magnitude and Mixed Mode Multiplication

- HMU16 is Compatible with the AM29516, LMU16, IDT7216 and the CY7C516

- HMU17 is Compatible with the AM29517, LMU17, IDT7217 and the CY7C517

- TTL Compatible Inputs/Outputs

- . Three-State Outputs

- Available in a Ceramic 68 Pin Grid Array (PGA) and 68 Pin Plastic Leaded Chip Carrier (PLCC)

#### **Applications**

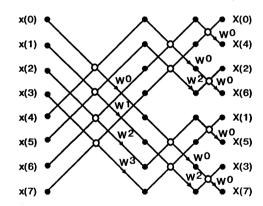

- Fast Fourier Transform Analysis

- Digital Filtering

- Graphic Display Systems

- Image Processing

- · Radar and Sonar

- . Speech Synthesis and Recognition

#### Description

The HMU16/HMU17 are high speed, low power CMOS 16 x 16-bit multipliers ideal for fast, real time digital signal processing applications.

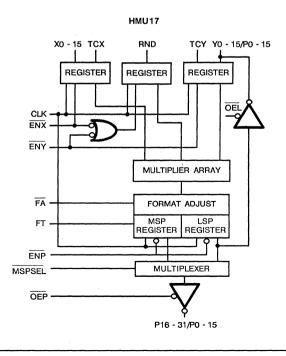

The X and Y operands along with their mode controls (TCX and TCY) have 17-bit input registers. The mode controls independently specify the operands as either two's complement or unsigned magnitude format, thereby allowing mixed mode multiplication operations.

Two 16-bit output registers are provided to hold the most and least significant halves of the result (MSP and LSP). For asynchronous output these registers may be made transparent through the use of the feedthrough control (FT).

Additional inputs are provided for format adjustment and rounding. The format adjust control (FA) allows the user to select either a left shifted 31-bit product or a full 32-bit product, whereas the round control (RND) provides the capability of rounding the most significant portion of the result

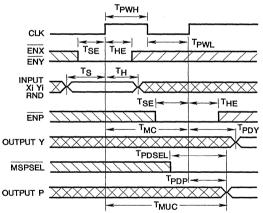

The HMU16 has independent clocks (CLKX, CLKY, CLKL, CLKM) associated with each of these registers to maximize throughput and simplify bus interfacing. The HMU17 has only a single clock input (CLK), but makes use of three register enables (ENX, ENY and ENP). The ENX and ENY inputs control the X and Y input registers, while ENP configuration facilitates the use of the HMU17 for microprogrammed systems.

The two halves of the product may be routed to a single 16-bit three-state output port via a multiplexer, and in addition, the LSP is connected to the Y-input port through a separate three-state buffer.

All outputs of the HMU16/HMU17 multipliers also offer threestate control for multiplexing results onto multi-use busses.

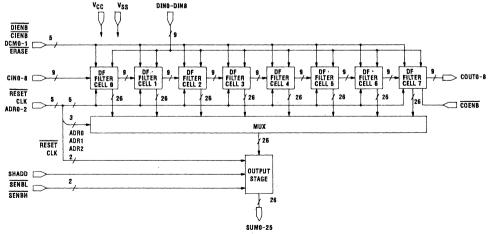

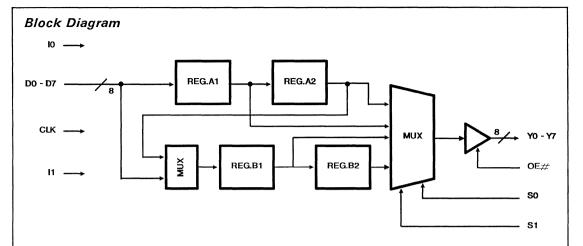

#### **HMU16/HMU17**

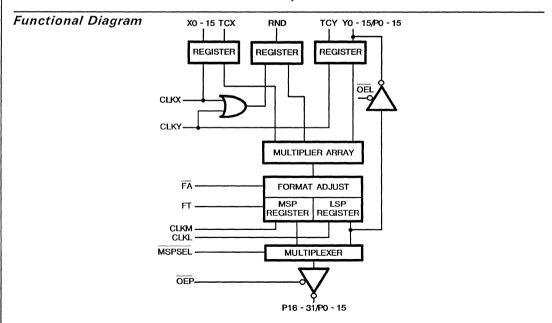

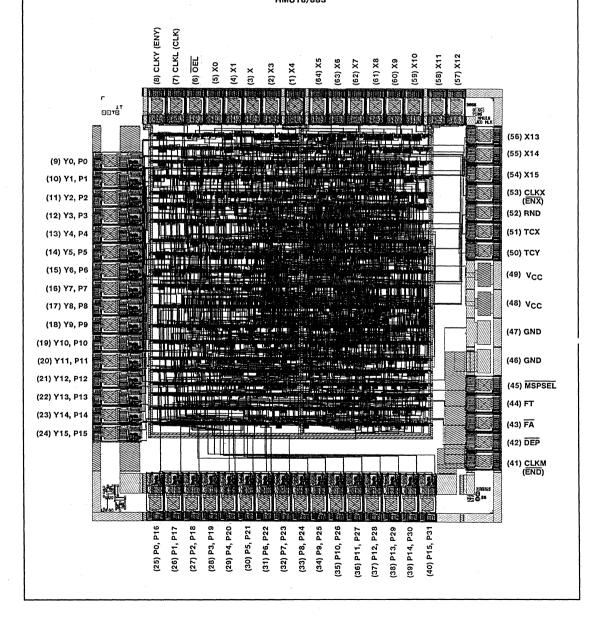

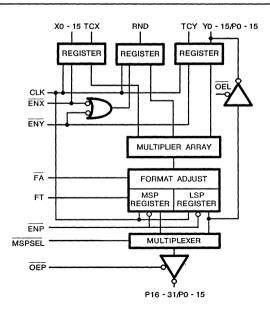

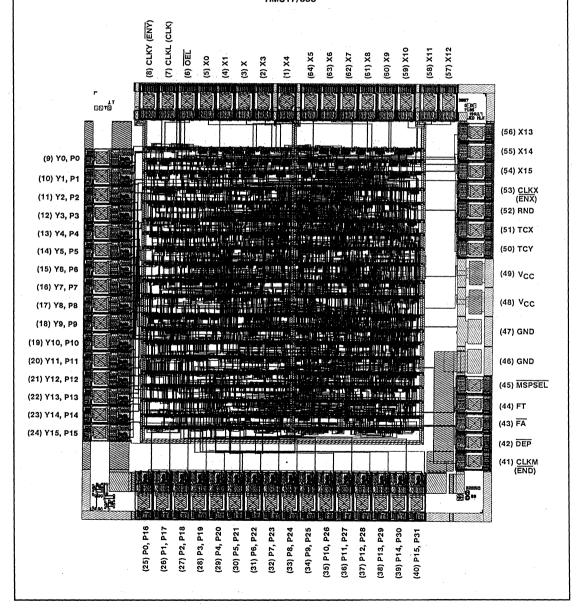

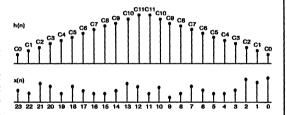

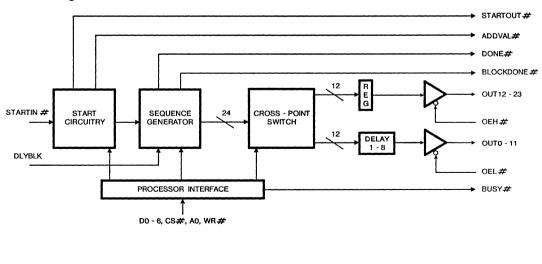

#### Functional Block Diagram HMU16 X0 - 15 TCX RND TCY Y0 - 15/P0 - 15 REGISTER REGISTER REGISTER OEL CLKX -CLKY-MULTIPLIER ARRAY FA-FORMAT ADJUST MSP LSP REGISTER REGISTER CLKM -CLKL MSPSEL MULTIPLEXER OEP -P16 - 31/P0 - 15

#### HMU16/HMU17

#### Pin Description

| SYMBOL             | PLCC<br>PIN NUMBER | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                               |

|--------------------|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vcc                | 1,68               |                  | $V_{CC}$ . The +5V power supply pins. A 0.1 $\mu F$ capacitor between the $V_{CC}$ and GND pin is recommended.                                                                                                                                                                                            |

| GND .              | 2,3                |                  | GND. The device ground.                                                                                                                                                                                                                                                                                   |

| X0-X15             | 47-59, 61-63       |                  | X-Input Data. These 16 data inputs provide the multiplicand which may be in two's complement or unsigned magnitude format.                                                                                                                                                                                |

| Y0-Y15/<br>P0-P15  | 27-42              | 1/0              | Y-Input/LSP Output Data. This 16-Bit port is used to provide the multiplier which may be in two's complement or unsigned magnitude format. It may also be used for output of the Least Significant Product (LSP).                                                                                         |

| P16-P31/<br>P0-P15 | 10-25              | 0                | Output Data. This 16-Bit port may provide either the MSP (P16-31) or the LSP (P0-15).                                                                                                                                                                                                                     |

| TCY, TCX           | 66, 67             | 1                | Two's Complement Control. Input data is interpreted as two's complement when this control is HIGH. A LOW indicates the data is to be interpreted as unsigned magnitude format.                                                                                                                            |

| FT                 | 5                  | 1                | Feedthrough Control. When this control is HIGH, both the MSP and LSP registers ar transparent. When LOW, the registers are latched by their associated clock signals.                                                                                                                                     |

| FA                 | 6                  | 1                | Format Adjust Control. A full 32-bit product is selected when this control line is HIGH. A LOW on this control line selects a left shifted 31-bit product with the sign bit replicated in the LSP. This control is normally HIGH except for certain two's complement integer and fractional applications. |

| RND                | 65                 |                  | Round Control. When this control is HIGH, a one is added to the Most Significant Bit (MSB) of the LSP. This position is dependent on the FA control; $FA = HIGH$ indicates RND adds to the 2–15 bit (P15), and $FA = LOW$ indicates RND adds to the $2^{-16}$ bit (P14).                                  |

| MSPSEL             | 4                  | ı                | Output Multiplexer Control. When this control is LOW, the MSP is available for output at the dedicated output port, and the LSP is available at the Y-input/LSP output port. When MSPSEL is HIGH, the LSP is available at both ports and the MSP is not available for output.                             |

| ŌĒĹ                | 46                 | ı                | Y-In/P0-15 Output Port Three-state Control. When OEL is HIGH, the output drivers are in the high impedance state. This state is required for Y-data input. When OEL is LOW, the port is enabled for LSP output.                                                                                           |

| ÖEP                | 7                  | 1                | P16-31/P0-15 Output Port Three-state Control. A LOW on this control line enables the output port. When OEP is HIGH, the output drivers are in the high impedance state.                                                                                                                                   |

| The following      | Pin Descriptions a | apply to the HMI | J16 only.                                                                                                                                                                                                                                                                                                 |

| CLKX               | 64                 | 1                | X-Register Clock. The rising edge of this clock loads the X-data input register along with the TCX and RND registers.                                                                                                                                                                                     |

| CLKY               | 44                 | !                | Y-Register Clock. The rising edge of this clock loads the Y-data input register along with the TCY and RND registers.                                                                                                                                                                                     |

| CLKM               | 8                  | I                | MSP Register Clock. The rising edge of CLKM loads the most significant product (MSP) register.                                                                                                                                                                                                            |

| CLKL               | 45                 | l                | LSP Register Clock. The rising edge of CLKL loads the least significant product (LSP) register.                                                                                                                                                                                                           |

| The following      | Pin Descriptions   | apply to the HMI | J17 only.                                                                                                                                                                                                                                                                                                 |

| CLK                | 45                 | 1                | Clock. The rising edge of this clock will load all enabled registers.                                                                                                                                                                                                                                     |

| ENX                | 64                 | I                | X-Register Enable. When $\overline{\text{ENX}}$ is LOW, the X-register is enabled; X-input data and TCX will be latched at the rising edge of CLK. When $\overline{\text{ENX}}$ is high, the X-register is in a hold mode.                                                                                |

| ENY                | 44                 | I                | Y-Register Enable. ENY enables the Y-register. (See ENX).                                                                                                                                                                                                                                                 |

| ENP                | 8                  | ì                | Product Register Enable. ENP enables the product register. Both the MSP and LSP sections are enabled by ENP. (See ENX).                                                                                                                                                                                   |

#### Functional Description

The HMU16/HMU17 are high speed 16 X 16-bit multipliers designed to perform very fast multiplication of two 16-bit binary numbers. The two 16-bit operands (X and Y) may be independently specified as either two's complement or unsigned magnitude format by the two's complement controls (TCX and TCY). When either of these control lines is LOW, the respective operand is treated as an unsigned 16-bit value; and when it is HIGH, the operand is treated as a signed value represented in two's complement format. The operands along with their respective controls are latched at the rising edge of the associated clock signal. The HMU16 accomplishes this through the use of independent clock inputs for each of the input registers (CLKX and CLKY), while the HMU17 utilizes a single clock signal (CLK) along with the X and Y register enable inputs (ENX and ENY).

Input controls are also provided for rounding and format adjustment of the 32-bit product. The Round input (RND) is provided to accomodate rounding of the most significant portion of the product by adding one to the Most Significant Bit (MSB) of the LSP register. The position of the MSB is dependent on the state of the Format Adjust Control (See Pin Descriptions and Multiplier Input/Output Format Tables). The Round input is latched into the RND register whenever either of the input registers is clocked. The Format Adjust control ( $\overline{\text{FA}}$ ) allows the product output to be formatted. When the  $\overline{\text{FA}}$  control is HIGH, a full 32-bit product is output; and when  $\overline{\text{FA}}$  is LOW, a left-shifted 31-bit product is output with the sign bit replicated in bit position 15 of the LSP. The  $\overline{\text{FA}}$  control must be HIGH for unsigned magnitude, and mixed mode multiplication

operations. It may be LOW for certain two's complement integer and fractional operations only (See Multiplier Input/Output Formats Table).

The HMU16/HMU17 multipliers are equipped with two 16-bit output registers (MSP and LSP) which are provided to hold the most and least significant portions of the resultant product respectively. The HMU16 uses independent clocks (CLKM and CLKL) for latching the two output registers, while the HMU17 uses a single clock input (CLK) along with the Product Latch Enable (ENP). The MSP and LSP registers may also be made transparent for asynchronous output through the use of the Feedthrough control (FT).

There are two output configurations which may be selected when using the HMU16/HMU17 multipliers. The first configuration allows the simultaneous access of the most and least significant halves of the product. When the MSPSEL input is LOW, the Most Significant Product will be available at the dedicated output port (P16-31/P0-15). The Least Significant Product is simultaneously available at the bi-directional port shared with the Y-inputs (Y0-15/P0-15) through the use of the LSP output enable (OEL). The other output configuration involves multiplexing the MSP and LSP registers onto the dedicated output port through the use of the MSPSEL control. When the MSPSEL control is LOW, the Most Significant Product will be available at the dedicated output port; and when MSPSEL is HIGH, the Least Significant Product will be available at this port. This configuration allows access of the entire 32-bit product by a 16-bit wide system bus.

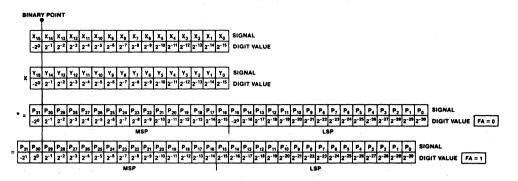

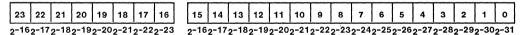

#### Multiplier Input/Output Formats Table

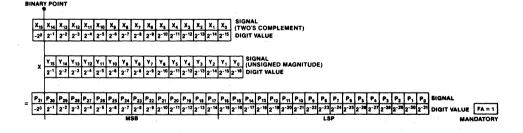

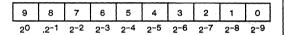

#### FRACTIONAL TWO'S COMPLEMENT NOTATION

<sup>\*</sup> In this format an overflow occurs in the attempted multiplication of the two's complement number 1,000  $\dots$  0 with 1,000  $\dots$  0 yielding an erroneous product of -1 in the fraction case and  $-2^{30}$  in the integer case.

#### FRACTIONAL UNSIGNED MAGNITUDE NOTATION

#### FRACTIONAL MIXED MODE NOTATION

#### Multiplier Input/Output Formats Table (Continued)

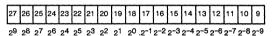

#### INTEGER TWO'S COMPLEMENT NOTATION

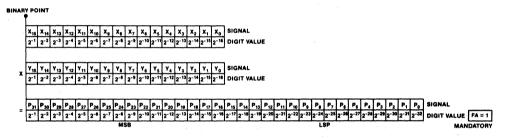

|     |                |     |      |    |                 |                 |                 |      |     |                 |     |                 |                 |     |                 |                 |     |                 |      |                 |                 |      |      |    |                |    |                |                |                |                |                | BI             | NAR            | Y POINT            |

|-----|----------------|-----|------|----|-----------------|-----------------|-----------------|------|-----|-----------------|-----|-----------------|-----------------|-----|-----------------|-----------------|-----|-----------------|------|-----------------|-----------------|------|------|----|----------------|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--------------------|

|     |                |     |      |    |                 |                 |                 |      |     |                 |     |                 |                 |     |                 |                 |     |                 |      |                 |                 |      |      |    |                |    |                |                |                |                |                |                |                |                    |

|     |                |     |      |    |                 |                 |                 |      |     |                 |     |                 |                 |     |                 |                 |     | X 15            | X 14 | X 13            | X 12            | X,1  | X 10 | X, | X.             | X, | X <sub>8</sub> | X <sub>5</sub> | X4             | x,             | X2             | X,             | X <sub>0</sub> | SIGNAL             |

|     |                |     |      |    |                 |                 |                 |      |     |                 |     |                 |                 |     |                 |                 |     | -215            | 214  | 213             | 212             | 211  | 210  | 29 | 28             | 27 | 26             | 25             | 24             | 23             | 22             | 21             | 20             | DIGIT VALUE        |

|     |                |     |      |    |                 |                 |                 |      |     |                 |     |                 |                 |     |                 |                 |     |                 |      |                 |                 |      |      |    |                |    |                |                |                |                |                |                |                |                    |

|     |                |     |      |    |                 |                 |                 |      |     |                 |     |                 |                 |     |                 |                 |     | r               | T.,  | T               | T               | T.,  | T    | T  |                | Г  | r              | T              | T              | T              | T              |                | T              |                    |

|     |                |     |      |    |                 |                 |                 |      |     |                 |     |                 |                 |     |                 |                 | X   | Y 15            | Y 14 | Y 13            | Y 12            | Y 11 | Y 10 | ٧, | Y.8            | ٧, | Y 6            | Y 5            | 14             | ¥3             | Y2             | ٧,             | Y0             | SIGNAL             |

|     |                |     |      |    |                 |                 |                 |      |     |                 |     |                 |                 |     |                 |                 |     | -215            | 214  | 213             | 212             | 211  | 210  | 29 | 28             | 27 | 26             | 25             | 24             | 23             | 22             | 21             | 20             | DIGIT VALUE        |

|     |                |     |      |    |                 |                 |                 |      |     |                 |     |                 |                 |     |                 |                 |     |                 |      |                 |                 |      |      |    |                |    |                |                |                |                |                |                |                |                    |

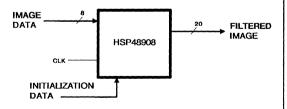

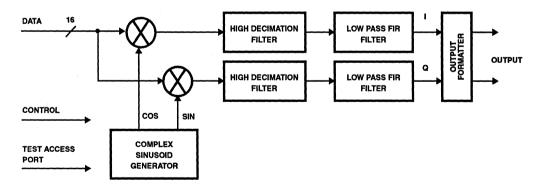

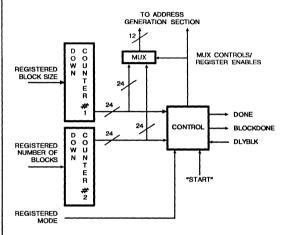

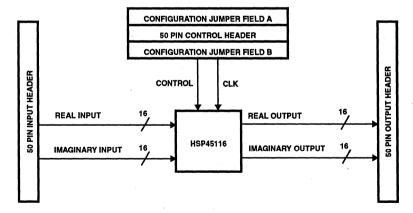

| • = | P <sub>3</sub> | , F | 30 P | 29 | P 28            | P <sub>27</sub> | P <sub>28</sub> | P 25 | P24 | P23             | P22 | P21             | P <sub>20</sub> | P19 | P <sub>18</sub> | P17             | P16 | P <sub>15</sub> | P14  | P <sub>13</sub> | P <sub>12</sub> | P11  | P 10 | Pg | P <sub>8</sub> | Ρ, | Pe             | P <sub>5</sub> | P4             | P <sub>3</sub> | P <sub>2</sub> | Р,             | Po             | SIGNAL             |