# VIA C3 Processor Alternate Instruction Set Programming Reference

Version 0.25 (Review version, Incomplete)

VIA Confidential

# This is **Version 0.25** of the VIA C3 Processor Alternate Instruction Set Programming Reference.

#### © 2002 VIA Technologies, Inc All Rights Reserved.

VIA reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to any implied warranty of merchantability or fitness for a particular purpose. No license, express or implied, to any intellectual property rights is granted by this document.

VIA makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. VIA disclaims responsibility for any consequences resulting from the use of the information included herein.

# **Table of Contents**

| 1 | 1-1          |                                         |      |

|---|--------------|-----------------------------------------|------|

|   | 1.1          | BASIC CONCEPTS                          | 1-1  |

|   | 1.2          | OVERVIEW OF THIS PROGRAMMING REFERENCE  | 1-1  |

|   | 1.3          | GENERAL PURPOSE REGISTERS               | 1-2  |

|   | 1.4          | FLOATING POINT REGISTERS                | 1-4  |

|   | 1.5          | MMX <sup>TM</sup> REGISTERS             | 1-4  |

|   | 1.6          | INTERNAL PROCESSOR REGISTERS            |      |

| _ |              |                                         |      |

| 2 | 2-1          |                                         |      |

|   | 2.1          | GENERAL FORMAT & PRIMARY OPCODES        |      |

|   | 2.1.         |                                         |      |

|   | 2.2          | INSTRUCTION FORMATS USED                |      |

|   | 2.2.<br>2.2. | ,                                       |      |

|   | 2.2.         |                                         |      |

|   | 2.2.         |                                         |      |

|   | 2.2.         |                                         | 2-15 |

| 3 | 1            |                                         |      |

| J | •            |                                         |      |

|   | 3.1          | ALU INSTRUCTIONS                        |      |

|   | 3.1.<br>3.1. |                                         |      |

|   | 3.2          | EFLAGS UPDATE FORMS                     |      |

|   | 3.3          | LOAD/STORE INSTRUCTIONS                 |      |

|   | 3.4          | CONTROL REGISTERS AND MICRO-OPERATIONS  |      |

|   | 3.4          | CONTROL REGISTERS AND MICRO-OF EXATIONS |      |

| 4 | 4-1          |                                         |      |

|   | 4.1          | X87 FLOATING PONT REGISTERS             | 4-1  |

|   | 4.2          | X87 FLOATING-PONT MICRO-OPERATIONS      | 4-2  |

|   | 4.2.         | 1 FADD, FSUB, FSUBR, FMUL, FDIV, FDIVR  | 4-2  |

|   | 4.2.         | 2 FSQRT, FABS, FCHS                     | 4-4  |

| 5 | 5-1          |                                         |      |

|   | 5.1          | MMX REGISTERS                           | 5.2  |

|   | 5.2          | MMX MICRO-OPERATIONS                    |      |

|   | 5.2.         |                                         |      |

|   | 5.2.         |                                         |      |

|   | 5.2.         | 3 MMXUNPACK                             | 5-5  |

|   | 5.2.         |                                         |      |

|   | 5.2.<br>5.2. |                                         |      |

|   | 5.2.<br>5.2. |                                         |      |

|   | _            | 8 SHIFT                                 |      |

**CHAPTER**

1

# INTRODUCTION

This document describes an alternate set of instructions that may be used on the VIA C3 processor. The alternate instructions are the internal instructions of the VIA C3 processor and provide substantial additional function over the x86 instruction set. The VIA C3 Alternate Instruction Set Application Note describes how system software can enable these alternate instructions. This document is a programming reference describing the encoding and operation of alternate instructions.

# 1.1 BASIC CONCEPTS

The VIA C3 processor family is intended as a plug-replaceable, software-compatible alternative to the Intel Pentium III processor. Accordingly, the VIA C3 processor normally executes compatible instructions. The internal design of the VIA C3 processor, however, is quite different from the Pentium III internal design. In particular, the VIA C3 processor comprises two major components: a front-end that fetches x86 instruction bytes and translates them from x86 into internal instructions, and an internal microprocessor that executes these internal instructions.

# 1.2 OVERVIEW OF THIS PROGRAMMING REFERENCE

This Programming Reference is divided into sections describing internal instructions according to the registers used:

■ **Chapter 1 – Introduction.** Describes the different execution units and programmer's model of the registers.

- Chapter 2 Instruction format. Describes the instruction format and bit field definitions.

- Chapter 3 General instructions. These instructions operate on the general x86 registers EAX, EBX, ECX, EDX, EBP, ESP, ESI, EDI as well as additional temporary general registers.

- **Chapter 4 Floating-point instructions.** These instructions operate on the floating-point registers as well as additional temporary floating-point registers.

- Chapter 5 MMX<sup>TM</sup> instructions. These instructions operate on the x86 MMX<sup>TM</sup> registers as well as additional temporary MMX<sup>TM</sup> registers.

# 1.3 GENERAL PURPOSE REGISTERS

These are 32 general purpose registers (GPRs) with similar usage to the x86 GPRs. GPR 0 always returns zero and can never be written. GPR 31 has a different special meaning in alternate instruction mode. It is the forward path data from the EA unit when referenced on load/store instructions (not LEA) as the base.

The GPRs have the required x86 functionality in that there are instruction controls that can select byte-oriented subsets (such as the low byte) of the 32-bit result data to be written into the result register.

The x86 instruction translator and associated microcode use the GPRs to store some x86 architecture registers such as the x86 GPRs and the x86 selector registers. These registers are directly referenced by code generated by the translator; thus, the mapping of EAX etc. into the native GPRs is fixed and considered part of the ISA. Other use of the GPRs is known only to the x86 microcode and thus is not defined as part of the ISA. A table below shows the usage of all GPRs and whether their use is known to the hardware (T means that the translator references the register, and H means that there are special hardware semantics for this register).

# **GPR Registers**

| Reg | Asm Label  | Description                 | Hdw<br>Vis |

|-----|------------|-----------------------------|------------|

| R0  | 0          | Constant 0                  | Н,Т        |

| R1  | tmp1,X_EA  | Xlator-ucode communication  | Т          |

| R2  | tmp2,X_ED  | Xlator-ucode communication  | Т          |

| R3  | tmp3,X_ED2 | Xlator-ucode communication  | Т          |

| R4  | tmp4       | Normal microcode temp       |            |

| R5  | tmp5       | Normal microcode temp       |            |

| R6  | tmp6       | Normal microcode temp       |            |

| R7  | tmp7       | Normal microcode temp       |            |

| R8  | ES         | (1)                         | Т,Н        |

| R9  | CS         | (1)                         | Т,Н        |

| R10 | SS         | (1)                         | Т,Н        |

| R11 | DS         | (1)                         | Т,Н        |

| R12 | FS         | (1)                         | Т,Н        |

| R13 | GS         | (1)                         | Т,Н        |

| R14 | LDTR       | (1)TR (upper), LDTR (lower) | Н          |

| R15 | tmp15      | (1)Special emulator temp    | Н          |

| R16 | EAX        |                             | Т          |

| R17 | ECX        |                             | T          |

| R18 | EDX        |                             | Т          |

| R19 | EBX        |                             | T          |

| R20 | ESP        |                             | T          |

| R21 | EBP        |                             | Т          |

| R22 | ESI        |                             | Т          |

| R23 | EDI        |                             | Т          |

| R24 | tmp24      | Exception handler temp      |            |

| R25 | tmp25      | Exception handler temp      |            |

| R26 | tmp26      | Exception handler temp      |            |

| R27 | tmp27      | Exception handler temp      |            |

| R28 | tmp28      | Exception handler temp      |            |

| R29 | tmp29      | Exception handler temp      |            |

| R30 | tmp30      | Exception handler temp      |            |

| R31 | tmp31   | Exception handler temp                       |     |

|-----|---------|----------------------------------------------|-----|

|     | LEA_FWD | EA forward path for load/store instructions/ | Т,Н |

|     |         | Normal data for non load/store               |     |

|     |         | instructions                                 |     |

(1) XPUSH of 32-bits pushes 0x0000 | [15:0]

# 1.4 FLOATING POINT REGISTERS

The floating point data registers are similar to those in x86 architecture except that:

- there are extra scratch registers available, and

- all of the registers may be directly accessed in addition to the x86 stack semantics.

| Reg   | Asm Label | Description                   | Туре |

|-------|-----------|-------------------------------|------|

| FP0   | FP0       | x86 FP Stack Register 0       | RW   |

| FP1   | FP1       | x86 FP Stack Register 1       | RW   |

| FP2   | FP2       | x86 FP Stack Register 2       | RW   |

| FP3   | FP3       | x86 FP Stack Register 3       | RW   |

| FP4   | FP4       | x86 FP Stack Register 4       | RW   |

| FP5   | FP5       | x86 FP Stack Register 5       | RW   |

| FP6   | FP6       | x86 FP Stack Register 6       | RW   |

| FP7   | FP7       | x86 FP Stack Register 7       | RW   |

| FP8   | FP8       |                               | RW   |

| FP9   | FP9       |                               | RW   |

| FP10  | FP10      |                               | RW   |

| FP11  | FP11      |                               | RW   |

| FP12  | FP12      |                               | RW   |

| FP13  | FP13      |                               | RW   |

| FP14  | FP14      |                               | RW   |

| FP15  | FP15      |                               | RW   |

| FP16: | FP16:FP31 | FP Scratch registers 16 to 31 | RW   |

| FP31  |           |                               |      |

# 1.5 MMX™ REGISTERS

Xxxx

# 1.6 INTERNAL PROCESSOR REGISTERS

XXXX.

CR0 ...

**CHAPTER**

2

# **INSTRUCTION FORMAT**

This chapter describes the format and bit fields of the alternate instructions.

# 2.1 GENERAL FORMAT & PRIMARY OPCODES

Alternate instruction formats are all instructions 32 bits long with a 6-bit primary opcode field:

| 31:26          | 25:0             |

|----------------|------------------|

| Primary Opcode | Opcode Dependent |

| 6              | 26               |

Some of the primary opcodes have extended opcodes in other bits of the instruction.

# 2.1.1 PRIMARY OPCODES

| The pri | The primary opcodes are: |       |        |        |         |      |        |       |

|---------|--------------------------|-------|--------|--------|---------|------|--------|-------|

| 28:26→  | 0                        | 1     | 2      | 3      | 4       | 5    | 6      | 7     |

| 31:29↓  |                          |       |        |        |         |      |        |       |

| 0       |                          |       |        |        |         |      | XJ     |       |

| 1       | ORIU                     | ADDI  | ANDIU  | ANDIL  | ANDI    | ORI  | XORI   | XORIU |

| 2       |                          | FPU   | XLFP   | XSFP   | MMX     |      | XLMMX  | XSMMX |

| 3       |                          |       |        |        |         |      |        |       |

| 4       | XALU                     | XALUI | XALUR  | XALUIR |         |      |        |       |

| 5       | XMISC                    |       |        | XLEAI  | XLEAD   |      |        |       |

| 6       | XL                       | XL2   | XL3    | XLBI   | XLDESC  | XIOR | XPOPBR | XPOP  |

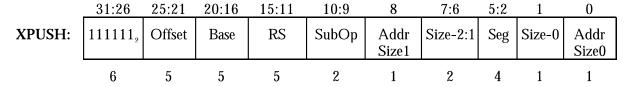

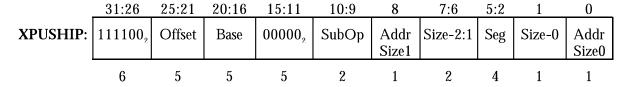

| 7       | XS                       | XS2   | XPUSHI | XSI    | XPUSHIP | XIOW | XSU    | XPUSH |

The shaded opcodes have extended opcodes as defined in subsequent sections. Cross-hatched unlabeled opcodes represent primary opcodes that are not included in the alternate instruction set.

# 2.2 INSTRUCTION FORMATS USED

# 2.2.1 IMMEDIATE (OR I-TYPE) INSTRUCTION FORMATS

Some alternate instructions use the immediate instruction format:

| 31:26  | 25:21 | 20:16 | 15:0       |

|--------|-------|-------|------------|

| Opcode | RS    | RT    | IMMMEDIATE |

| 6      | 5     | 5     | 16         |

The opcode is one of the primary opcodes. The source and target operands for these I-type instructions are:

# GPR[RT] ← GPR[RS] opcode IMMEDIATE

Note that the destination is RT in this case rather than RD as for R-type instructions (which are described in a later section).

The I-type instructions are:

| $28:26 \rightarrow 31:29 \downarrow$ | 0    | 1    | 2     | 3     | 4    | 5   | 6    | 7     |

|--------------------------------------|------|------|-------|-------|------|-----|------|-------|

| 1                                    | ORIU | ADDI | ANDIU | ANDIL | ANDI | ORI | XORI | XORIU |

# 2.2.1.1 XALU-Type Instruction Formats

The XALU-type instruction format is used for x86-style ALU instructions defined using the XALU[I][R] primary opcodes. It has special control fields to allow most x86 ALU semantics to be specified in a single 32-bit instruction.

| 31:26    | 25:21 | 20:16 | 15:11 | 10:0     |

|----------|-------|-------|-------|----------|

| XALU[R]  | RS    | RT    | RD    | Function |

| XALUI[R] | RS    | Const | RD    | Function |

| 6        | 5     | 5     | 5     | 11       |

The source and target operands for XALU[R] instructions is basically the same as for R-type instructions. XALUI[R] instructions are similar except that they allow an encoded immediate value, to be used instead of RT. is a multi-part field that defines the function to be performed.

GPR[RD] ← GPR[RS] function GPR[RT] GPR[RD] ← GPR[RS] function Const value

The R versions of the XALU[I][R] instructions cause the x86 result flags to be set as defined for the particular instruction type.

**Implementation Note:** As described in the instruction definition section, not every version of every extended opcode is needed for all of the XALU[I][R] instructions.

#### 2.2.1.2 Const Field (for XALUI forms)

The 5-bit field allows a small constant to be used as an immediate value. The following table lists the values for .

| Const  | Mnemonic | Description                                      |

|--------|----------|--------------------------------------------------|

| 00000, | 0        | Constant zero                                    |

| 00001, | 1        | Constant one                                     |

| 00010, | 2        | Constant two                                     |

| 00011, | 4        | Constant four                                    |

| 00100, | 8        | Constant eight                                   |

| 00101, | 16       | Constant 16                                      |

| 00110, | 24       | Constant 24                                      |

| 00111, | 32       | Constant 32                                      |

| 01000, | LoWdMask | 0x0000FFFF (used for AltInst sel register moves) |

| 01001, | -1       | Constant minus one                               |

| 01010, | -2       | Constant minus two                               |

| 01011, | -4       | Constant minus four                              |

| 01100, | -8       | Constant minus eight                             |

| 01101, |          |                                                  |

| 01110, |          |                                                  |

| 01111, | 5        | Constant 5                                       |

| 10000, | OS         | Operand size: +2 or +4 depending on TSR.OS                  |

|--------|------------|-------------------------------------------------------------|

| 10001, | 3          | Constant 3                                                  |

| 10010, | 6          | Constant 6                                                  |

| 10011, | 7          | Constant 7                                                  |

| 10100, | 9          | Constant 9                                                  |

| 10101, | LoByteMask | Constant 0x00FF                                             |

| 10110, | OSSH       | OS-related shift magic count: 16 for OS==0, 0 for OS==1     |

| 10111, |            |                                                             |

| 11000, | MOS        | Minus operand size: -2 or -4 depending on TSR.OS            |

| 11001, | MGS        |                                                             |

| 11010, |            |                                                             |

| 11011, |            |                                                             |

| 11100, | DFind1     | Minus or Plus 1 respectively depending on EFLAGS.DF         |

| 111012 | DFindOS    | Minus or Plus Operand Size (2 or 4) (defined in TSR.OS) re- |

| ~      |            | spectively depending on EFLAGS.DF                           |

| 11110, | IMMED      | Use value in the IMMED Register                             |

| 11111, | DISP       | Use value in the DISP Register                              |

## 2.2.1.3 Function Codes for XALU-Type

| 10:8 | 7:5    | 4:0   |

|------|--------|-------|

| Ind  | DPcntl | SubOp |

| 3    | 3      | 5     |

#### SubOp Field

This field describes the ALU function. It is similar in concept to the 6-bit extended opcode for special instructions. The extended opcodes for the primary opcodes are:

| $2:0\rightarrow$ | 0   | 1    | 2   | 3   | 4    | 5     | 6     | 7     |

|------------------|-----|------|-----|-----|------|-------|-------|-------|

| 4:3↓             |     |      |     |     |      |       |       |       |

| 0                | SHL |      | SHR | SAR | ROL  | ROR   | RCL   | RCR   |

| 1                | INC | CMPS | DEC |     | IMUL | MUL   | IDIV  |       |

| 2                | ADD | ADC  | SUB | SBB | AND  | OR    | XOR   | NOR   |

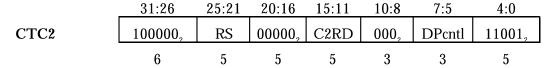

| 3                |     | CTC2 |     |     |      | SETCC | MFLOU | MFLOI |

The fourth-row opcodes have special semantics over the normal logical operations: the C2 suffix indicates that the destination is a CP2 control register (vs. a GPR. Only some CP2 registers may be used as the destination.

#### **DPcntl**

The DPcntl field controls (1) the source byte selection, (2) the size of the writes into the register file, and (3) the size of the result over which condition codes are calculated.

In the table below, BE indicates which bytes of the register file are written back ( ); and CC is the portion of the result that the condition codes other than AF and PF are calculated over

(these are always based on carry from bit 3 and the low order 8 bits of the result). Condition codes are always calculated over the low-order bits of the result.

| DPcntl | Mnemonic   | BE        | cc      |

|--------|------------|-----------|---------|

| 0002   | 32         | 000011112 | 32 bits |

| 0012   | 16         | 000000112 | 16 bits |

| 0102   | LL         | 000000012 | 8 bits  |

| 0112   | HL         | 000000102 | 8 bits  |

| 1002   | LH         | 000000012 | 8 bits  |

| 1012   | НН         | 000000102 | 8 bits  |

| 1102   | (reserved) |           |         |

| 1112   | (reserved) |           |         |

#### 32

Provides 32 bit operations. All 32 bits are written back to the register file. Condition codes are calculated with an operand size of 32 bits.

#### 16

Provides for 16-bit operations. The low 16 bits are written back to the register file. Condition codes are calculated on the low-order 16 bits of the result.

#### LL

Provides for 8-bit low-low byte operations. The low 8 bits of each operand are used as the sources and the low 8 bits of the result are written back to the register file. Condition codes are calculated on the low-order 8 bits of the result.

#### HL

Provides for 8-bit high-low byte operations. Bits 15:8 of the left operand are shifted right and operated on with the low byte of the right operand. Condition codes are calculated on the low-order 8 bits of the result. The low 8 bits are shifted left and written into bits 15:8 of the target register.

#### HH

Provides for 8-bit high-high byte operations. Bits 15:8 of both operands are shifted right and operated on. Condition codes are calculated on the low-order 8 bits of the result. The low 8 bits are shifted left and written into bits 15:8 of the target register.

#### LH

Provides for 8-bit low-high byte operations. Bits 15:8 of the right operand are shifted right and operated on with the low byte of the left operand. Condition codes are calculated on the low-order 8 bits of the result. The low 8 bits are into the low byte of the target register.

#### (reserved)

Using reserved DPcntl codes will result in unpredictable results.

#### Ind

The field is not useful for alternate instruction mode and must always be all zeros. Non-zero values will result in unpredictable results.

# 2.2.2 XMISC-Type Instruction Formats

The XMISC-type instruction format is used for miscellaneous x86-related instructions defined using the XMISC primary opcode. It is like the XALU format except that the field is special for each particular instruction.

|   | 31:26 | 25:21 | 20:16 | 15:11 | 10:6    | 5:0                       |

|---|-------|-------|-------|-------|---------|---------------------------|

|   | XMISC | RS    | RT    | RD    | SubFunc | Defined By<br>Instruction |

| ٠ | 6     | 5     | 5     | 5     | 5       | 6                         |

#### **Subfunction Field**

This field describes the specific instruction. It is similar in concept to the 6-bit extended opcode for R-form instructions. The extended opcodes for the new primary opcode are

| $8:6 \rightarrow 0$ | 1      | 2     | 3     | 4       | 5    | 6     | 7     |

|---------------------|--------|-------|-------|---------|------|-------|-------|

| 10:9↓               |        |       |       |         |      |       |       |

| 0 $XRET X$          | KCNULL | XRFP  | XHALT | SBF/SBN | MFHI |       | CFPFL |

| 1 XTI               | XTII   |       |       | MTC0    | MFC0 | MTCNT | MFCNT |

| 2 XMDB Z            | XMDBI  | DMTC1 | DMFC1 | MTC1    | MFC1 | CTC1  | CFC1  |

| 3 D                 | OMTMD  | DMTC2 |       | MTC2    | MFC2 |       | CFC2  |

2-6 Instruction Format Chapter 2

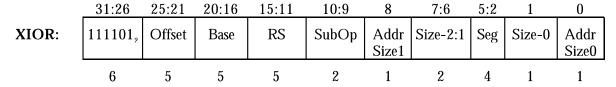

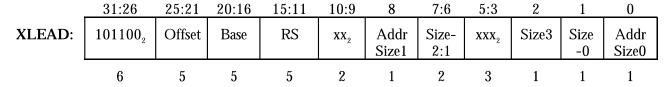

# 2.2.3 XLS-Type Instruction Formats

The new XLS-Type instruction format is used for x86-style load and store (Xlx, XSx) instructions. This form is highly encoded to allow most x86 load/store semantics to be specified in a single 32-bit instruction.

| 31:26  | 25:21 | 20:16 | 15:11  | 10:0     |

|--------|-------|-------|--------|----------|

| Opcode | RS    | Base  | Offset | Function |

| 6      | 5     | 5     | 5      | 11       |

The source and target operands for XL-type instructions are similar to those for load and store instructions (except that the Base register is in a different register field). The x86-style EA is calculated as a base register plus an offset. The x86 selector register and other x86 addressing semantics are specified in the field.

Load: RS ← memory(selector, GPR[Base] + Offset)

Store: RS → memory(selector, GPR[Base] + Offset)

This general instruction format is also used for XLEA instructions which do not actually perform load or stores but rather calculate an offset address. However, the XLEA instructions have some unique fields and should really be considered as special format instructions.

#### Offset

The 5-bit field allows a small constant to be used as an immediate value. The following table lists the values for .

| Offset | Mnemonic | Description          |  |

|--------|----------|----------------------|--|

| 00000, | 0        | Constant zero        |  |

| 00001, | 1        | Constant one         |  |

| 00010, | 2        | Constant two         |  |

| 00011, | 4        | Constant four        |  |

| 00100, | 8        | Constant eight       |  |

| 00101, | 16       | Constant 16          |  |

| 00110, | 24       | Constant 24          |  |

| 00111, | 32       | Constant 32          |  |

| 01000, | 10       | Constant ten         |  |

| 01001, | -1       | Constant minus one   |  |

| 01010, | -2       | Constant minus two   |  |

| 01011, | -4       | Constant minus four  |  |

| 01100, | -8       | Constant minus eight |  |

| 01101, |          |                      |  |

| 01110, |          |                      |  |

| 01111, | 5        | Constant 5           |  |

| 10000,      | OS      | Operand size: +2 or +4 depending on TSR.OS                  |

|-------------|---------|-------------------------------------------------------------|

| 10001,      | PDOS    |                                                             |

| 10010,      |         |                                                             |

| 10011,      |         |                                                             |

| 10100,      |         |                                                             |

| 10101,      |         |                                                             |

| 10110,      |         |                                                             |

| 10111,      |         |                                                             |

| 11000,      | MOS     | Minus operand size: -2 or -4 depending on TSR.OS            |

| 11001,      | MGS     |                                                             |

| 11010,      | MDOS    |                                                             |

| 11011,      |         |                                                             |

| 11100,      | DFind1  | Minus or Plus 1 respectively depending on EFLAGS.DF         |

| $11101_{2}$ | DFindOS | Minus or Plus Operand Size (2 or 4) (defined in TSR.OS) re- |

|             |         | spectively depending on EFLAGS.DF                           |

| 11110,      |         |                                                             |

| 11111,      | DISP    | Use value in the DISP Register                              |

#### **Function Codes**

The XLx and XSx instructions are used to implement x86 load and store instructions. The function field encodes most of the x86 peculiar load/store semantics:

| 10:9  | 8          | 7:6      | 5:2 | 1      | 0          |

|-------|------------|----------|-----|--------|------------|

| SubOp | AddrSize-1 | Size-2:1 | Sel | Size-0 | AddrSize-0 |

| 2     | 1          | 2        | 4   | 1      | 1          |

Note that GPR indirection (via the IIR) is not available in the normal load/store format. If register indirection is needed, a XLEAx instruction (which allows indirection) must be used to calculate the address followed by the load/store instruction using the output register of the XLEA as the Base register.

#### AddrSize

Indicates the address size for the effective address calculation of this XL , or XS instruction.

| AddrSize | Mnemonic | Address Size Used |                   |

|----------|----------|-------------------|-------------------|

| 002      | AS       | TSR.AS            |                   |

| 012      | SAS      | TSR.SAS           |                   |

| 012      | OS       | TSR.OS            | If XLEAD or XLEAI |

| 102      | 16       | 16                |                   |

| 112      | 32       | 32                |                   |

Sel

Specifies the selector descriptor used for virtual address calculation and limit checking. The bit encoding is:

| SEL Value | Mnemonic | Descriptor Used               |

|-----------|----------|-------------------------------|

| 0000,     | ES       | ES                            |

| 0001,     | CS       | CS                            |

| 0010,     | SS       | SS                            |

| 0011,     | DS       | DS                            |

| 0100,     | FS       | FS                            |

| 0101,     | GS       | GS                            |

| 0110,     | GDT      | GDT                           |

| 0111,     | LDT      | LDT                           |

| 1000,     | IDT      | IDT                           |

| 1001,     | TSS      | TSS                           |

| 1010,     | FLAT     | Flat 32-bit address space     |

| 1011,     | Т0       | Temp0                         |

| 1100,     |          |                               |

| 1101,     |          |                               |

| 1110,     |          |                               |

| 1111,     | indSEL   | Use value in field of the TSR |

**Architecture Note:** The register encoding values for GDT and LDT are important: they differ only in the low-order bit which corresponds to the TI bit in a selector that selects GDT or LDT. This bit has a mux on it that selects the saved TI bit or the bit in the field based. This mux is set-up be the XTI instruction, but affects the following instruction —assumed to be a XLDES. See these instructions for more description of this magic.

**Usage Note:** The FLAT descriptor is set-up (by microcode) as a special "flat" segment used for implementing I/O accesses. This is a 32-bit, flat RW segment.

Size

The size field indicates which portion of the destination register to update for loads, and the size of the source operand for stores. It has different encodings for the various types of x86 load/store opcodes. The high order two bits come from the Size-2:1 field, and the low order bit is bit 1 of the instruction. The XLEAD and XLEAI instructions have an additional (highest order) bit which comes from bit 2 of the instruction.

All Load/Store Instructions (Include LEAx) Except XLDESC,XLFP/XSFP

| Size | Mnemonic | Data Size                                                                                                                  |                                                                         |

|------|----------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 0002 | 16       | 16 bits-low                                                                                                                |                                                                         |

| 0102 | 32       | 32 bits                                                                                                                    |                                                                         |

| 1002 | AS       | address size-16 or 32                                                                                                      | If 16 bits, it is low 16 bits.                                          |

| 1102 | OS       | operand size - 16 or 32                                                                                                    | If 16 bits, it is low 16 bits.                                          |

| 0012 | 8L       | 8 bits-low                                                                                                                 |                                                                         |

| 0112 | 8H       | 8 bits-high                                                                                                                |                                                                         |

| 0112 | 16H      | XPUSH: operand size<br>16 (31:16) or 32<br>(31:16) zero extended                                                           |                                                                         |

| 1012 | 64       | 64 bits In this case, the destination register (RS) must have an even address; the data will be loaded into RS and RS   1. | Note that there a store of 64 bits is an invalid (missing) instruction. |

| 1112 | IND      | defined by TSR.DPcntl                                                                                                      |                                                                         |

| 1112 | GS       | 16 or 32 depending on<br>XBR bit 27                                                                                        | Gate Size (only on XPUSH)                                               |

XLEAD and XLEAI same as previous plus:

| Size  | Mnemonic | Data Size                   |

|-------|----------|-----------------------------|

| Size  |          |                             |

| 10002 | SAS      | stack address size-16 or 32 |

| 10012 |          | undefined                   |

| 10102 |          | undefined                   |

| 10112 |          | undefined                   |

| 11002 |          | undefined                   |

| 11012 |          | undefined                   |

| 11102 |          | undefined                   |

| 11112 |          | undefined                   |

## SubOp

This field controls the use of the effective-address, linear-address, physical-address, and protection-calculation hardware for performing operations other than simple loads and stores. It is used mostly to precipitate exceptions before modifying the architectural state (thus facilitating instruction restartability). It is also used to control bus operations.

Various types of load/store instructions have different encodings for this field:

SubOp Type 1 – For All Load/Store Instructions Except Below Types

| Sub0p | Mnemonic | Load Desc        | Store Desc       |

|-------|----------|------------------|------------------|

| 002   | [norm]   | Normal Load      | Normal Store     |

| 012   | rwv      | Verify Writeable | Verify Writeable |

| 102   | sup      | Assume CPL = 0   | Assume CPL = 0   |

| 112   | lock     | Locked Load      | UnLock Store     |

SubOp Type 2 – XSU & XPOP Instructions

| Sub0p | Mnemonic    | Load Desc                                | Store Desc                               |  |

|-------|-------------|------------------------------------------|------------------------------------------|--|

| 002   | [norm]      | Normal Load                              | Normal Store                             |  |

| 012   | str_int     | Decr/test COUNT<br>Allow Interrupt       | String Semantics<br>Allow Interrupt      |  |

| 102   | str_testcnt | Test COUNT<br>Don't allow inter-<br>rupt | Test COUNT<br>Don't allow inter-<br>rupt |  |

| 112   |             |                                          |                                          |  |

SubOp Type 3 – For XLDESC (details on xldesc in page Error! Bookmark not defined.)

| Sub0p | Mnemonic | Load Desc            |     |

|-------|----------|----------------------|-----|

| 002   | dschk    | Data Segment checks  |     |

| 012   | sschk    | Stack Segment checks | N/A |

| 102   |          |                      |     |

| 112   | NoChk    |                      | N/A |

SubOp Type 3 – For XLDESC\_CS (details on xldesc\_cs in page Error! Bookmark not defined.)

| Sub0p | Mnemonic | Load Desc                    |     |

|-------|----------|------------------------------|-----|

| 002   | jmp_call | JMP and CALL checks          |     |

| 012   | retf     | Return far checks            | N/A |

| 102   | spec     | Checks for special microcode |     |

| 112   | NoChk    |                              | N/A |

SubOp Type 4 – XL2 & XS2 Instructions

| Sub0p | Mnemonic     | Load Desc                      | Store Desc                        |

|-------|--------------|--------------------------------|-----------------------------------|

| 002   | [norm]       | Normal Load                    |                                   |

| 012   | tickle       | Tickle Load                    | Tickle Store                      |

| 102   | tickle_ lock | Tickle Locked Load             |                                   |

| 112   | suplk        | Assume CPL = 0,<br>Locked Load | Assume CPL = 0, Un-<br>Lock Store |

SubOp Type 5 – For XIO

| SubOp | Mnemonic | Load Desc     | Store Desc                                                       |

|-------|----------|---------------|------------------------------------------------------------------|

| 002   | [norm]   | I/O Read      | I/O Write                                                        |

| 012   | special  | Interrupt Ack | Special Bus Cycle<br>(type defined by low<br>three address bits) |

| 102   |          |               |                                                                  |

| 112   |          |               |                                                                  |

SubOp Type FP – XLFP & XSFP Instructions

| SubOp Mnemonic |          | Load Desc        | Store Desc        |  |

|----------------|----------|------------------|-------------------|--|

| 002            | [norm]   | Normal Load      |                   |  |

| 012            | tickle   | Tickle Load      | Tickle Store      |  |

| 102            | NORM_REC | Load w/ RFP      | Store w/ RFP      |  |

| 112            | TICK_REC | Tick Load w/ RFP | Tick Store w/ RFP |  |

#### norm

Performs a normal load or store operation as specified in the rest of the instruction. This is the default in assembler instructions and does not have to be specified.

#### rwv (used only with loads)

Performs the load operation as specified in the instruction, except that it performs all protection and access right checks as though this were a store operation. This is meant to be used to force read-modify-write operations that are going to fault on the write to fault on the read instead. This is used to force exceptions to occur before the flags are modified, and to prevent partial modification of the target memory location on unaligned references.

#### tickle

Performs the effective-address, virtual-address, and physical-address calculations as specified in the instruction including all protection and access-right checks. However, the actual transfer of data is inhibited. This is meant to be used to verify that all parts of a data structure will not generate faults before a portion of it is modified.

#### lock (used only with loads)

Performs the load operation as specified in the instruction with x86 Lock semantics. The fully compatible definition invalidates the cache line containing the data and asserts the LOCK#

signal on the external bus. Locked loads are also tested for write privileges as described above in LSrmv.

The bus control unit manages the synchronization of asserting and deasserting LOCK#. It basically counts consecutive locked loads operations (reaching the bus unit) and deasserts LOCK# after the last of an equivalent number of stores. However, the locked store portions of the locked RMW sequence must be specified with a Lock SubOp.

Note that the TSR.LK bit (the x86 instruction had a valid LOCK prefix) forces a LOCK sequence only if the SubOp is RVW. If the SubOp is nom, for example, the LOCK prefix is ignored.

str\_int

Adds the following semantics to the load/store instruction:

- If the COUNT register is 0 (considering any effect of the previous instruction), do not perform the load or store operation and signal "stop string generation" to the translator.

- Else, perform the operation and decrement COUNT by one (forwarding results to next instruction test of COUNT).

In addition, an external interrupt, data breakpoint trap exception, or TF exception is allowed to occur following successful completion of the associated load/store instruction.

str testcnt

Adds the following semantics to the load/store instruction:

If the COUNT register is 0 (considering any effect of the previous instruction), do not perform the load or store operation and signal "stop string generation" to the translator.

special

Allows generation of interrupt acknowledge on loads, and special cycles on stores the low-order bits of the address defines the special bus operation (the byte enable lines on the bus define the cycle type).

sup

Performs the otherwise specified operation but performs all access right and paging tests as though CPL == 0. This is used for descriptor table accesses.

suplk

Performs the load with the semantics of and combined.

#### **Unaligned Operations**

There are two different meanings of

1. The data operand spans across two 8-byte-aligned memory units. This case is handled automatically by the hardware by decomposing the load/store operation into the correct two load/store operations for each portion. This will called

Note that this is technically different than the P54 which uses a four-byte boundary for generating multiple bus cycles (if the data size is four bytes or less) rather than eight.

2. The data is aligned such that it meets the x86 architecture definition of unaligned. In this case, if CPL == 3 && (EFLAGS.AC & CR0.AM) then an alignment exception occurs. This will called

The architecture alignment boundary for data is the same as for the P54 (some of this must be enforced by microcode).

#### **MMX Load and Store Instructions**

The MMX load and store instructions are formatted identically to the LS form load store instructions, with the exception that the load target and the store source registers are MMX operand registers. The size 64 store is a true size\_64 store in that page protection checking, etc. is performed for the entire 64 bit operand. Note that this is not the case in the standard form store-64 instructions.

# ADD LOAD\_ALU INFO HERE!!

#### **FPU Load and Store Instructions**

The FPU load and store instructions are formatted identically to the LS form load store instructions, with the exception that the load target and the store source registers are FPU operand registers and the size field (bits 7,6,1 in the instruction) are encoded to represent the format of the FPU load/store (see table below). The size 64 store is a true size\_64 store in that page protection checking, etc. is performed for the entire 64 bit operand. Note that this is not the case in the standard form store-64 instructions.

| 2221    | YI ED | and YCED | cizo | encodinas |

|---------|-------|----------|------|-----------|

| Z-Z-5-1 | XLFP  | and ASEP | Size | encoainas |

| Size | Mnemonic     | Data Size |

|------|--------------|-----------|

| 0002 | Int 16 (H)   | 16        |

| 0012 | Int 64 (L)   | 64        |

| 0102 | Int 32 (W)   | 32        |

| 0112 |              |           |

| 1002 | Exp 16 (Exp) | 16        |

| 1012 | FP Ext (E)   | 64        |

| 1102 | FP Sng (S)   | 32        |

| 1112 | FP Dbl (D)   | 64        |

# 2.2.4 CP1 (FLOATING POINT) INSTRUCTION FORMATS

See the floating-point instruction description section.

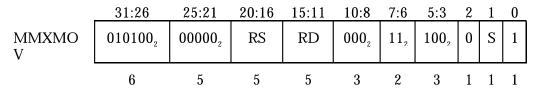

# 2.2.5 CP4 (MMX) INSTRUCTIONS

Coprocessor 4 primary opcodes are used for implementation of the MMX instruction set. Please refer to the MMX section for more detail.

**CHAPTER**

3

# **GENERAL INSTRUCTIONS**

This chapter describes the instructions that operate on the general purpose registers (GPRs) as well as the additional temporary registers.

# 3.1 ALU INSTRUCTIONS

# 3.1.1 IMMEDIATE INSTRUCTIONS

**Usage Note:** The following table summarizes what gets modified how by the 16-bit immediate logical instructions:

| logical mistracti | OIIS.             |                  |  |

|-------------------|-------------------|------------------|--|

| Instruction       | Upper RT          | Lower RT         |  |

| ANDI              | 0                 | RS(15:0) & Immed |  |

| ANDIL             | RS(31:16)         | RS(15:0) & Immed |  |

| ANDIU             | RS(31:16) & Immed | RS(15:0)         |  |

| ORI               | RS(31:16)         | RS(15:0)   Immed |  |

| ORIU              | RS(31:16)   Immed | RS(15:0)         |  |

| XORI              | RS(31:16)         | RS(15:0) ^ Immed |  |

| XORIU             | RS(31:16) ^ Immed | RS(15:0)         |  |

Chapter 3 General Instructions 3-1

## 3.1.1.1 ADDI - Add Immediate

# **Encoding**

## **Format**

ADDI RT,RS,0x1234

# **Description**

The contents of GPR  $\,$  is added to the  $\,$  field extended with 0x0000. The result is written back to GPR  $\,$  .

#### **Operation**

GPR[RT] = GPR[RS] + IMMEDIATE;

# **Flags Setting**

None

## **Exceptions**

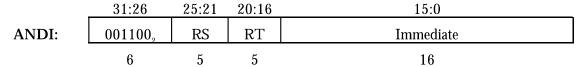

## 3.1.1.2 ANDI - AND Immediate

# **Encoding**

#### **Format**

| 7 7 7 7 | D.T. D.G. 0. 1004 |

|---------|-------------------|

| ANDI    | RT,RS,0x1234      |

| 1111121 | 1(1)1(0) (1)11201 |

# **Description**

the  $$\operatorname{field}$$  and ANDs it to 32-bit GPR  $% \operatorname{SPR}$  with the result replacing 32-bit GPR  $% \operatorname{SPR}$  .

## **Operation**

GPR[RT] = GPR[RS] & IMMEDIATE;

# Flags Setting

None

# **Exceptions**

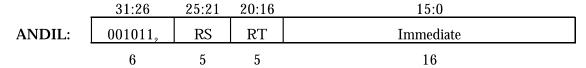

# 3.1.1.3 ANDIL - AND Immediate Lower

# **Encoding**

#### **Format**

ANDIL RT,RS,0x1234

# **Description**

The contents of GPR are ANDed with the field extended with 0xFFFF. The result is written back to GPR .

#### **Operation**

GPR[RT] = GPR[RS] & (0xffff0000 | IMMEDIATE);

# Flags Setting

None

## **Exceptions**

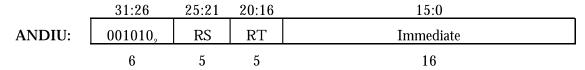

# 3.1.1.4 ANDIU - AND Immediate Upper

## **Encoding**

#### **Format**

| ANDIU | RT, | RS, | 0x6789 |

|-------|-----|-----|--------|

# **Description**

The contents of GPR are ANDed with the immediate field shifted left 16 and extended on the right with 0xFFFF. The result is written back to GPR .

#### **Operation**

$$GPR[RT] = GPR[RS] & ((IMMEDIATE << 16) | 0x0000FFFF);$$

## **Flags Setting**

None

## **Exceptions**

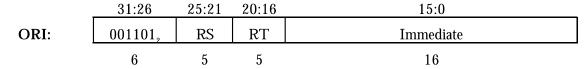

# 3.1.1.5 ORI - OR Immediate

# **Encoding**

#### **Format**

| ORI RI | RS, | 0x1234 |

|--------|-----|--------|

|--------|-----|--------|

## **Description**

the  $$\operatorname{field}$$  and ORs it to 32-bit GPR  $$\operatorname{Mathemath{BPR}}$$  with the result replacing 32-bit GPR  $$\operatorname{Mathemath{BPR}}$$  .

# **Operation**

GPR[RT] = GPR[RS] | IMMEDIATE;

# Flags Setting

None

# **Exceptions**

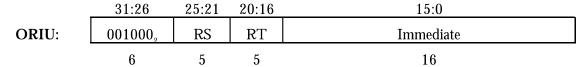

# 3.1.1.6 ORIU – OR Immediate Upper

# **Encoding**

#### **Format**

|--|

# **Description**

The contents of GPR are ORed with the immediate field shifted left 16. The result is written back to GPR .

# **Operation**

| <pre>GPR[RT] = GPR[RS]   (IMMEDIATE &lt;&lt; 16);</pre> |

|---------------------------------------------------------|

|---------------------------------------------------------|

# Flags Setting

None

# **Exceptions**

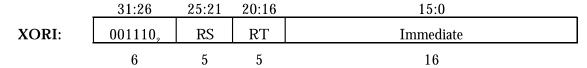

# 3.1.1.7 XORI - XOR Immediate

# **Encoding**

#### **Format**

| XORI   | RT, RS, 0x1234  |

|--------|-----------------|

| 110111 | 111/110/0111101 |

## **Description**

the  $$\operatorname{field}$$  and XORs it to 32-bit GPR  $$\operatorname{Mod}$  with the result replacing 32-bit GPR  $$\operatorname{Mod}$$  .

# **Operation**

GPR[RT] = GPR[RS] ^ IMMEDIATE;

# Flags Setting

None

# **Exceptions**

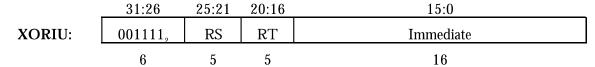

# 3.1.1.8 XORIU - XOR Immediate Upper

# **Encoding**

#### **Format**

| XOI | RIU | RT, RS, 0x1234 |  |

|-----|-----|----------------|--|

|     |     | ,              |  |

# **Description**

The contents of GPR are XORed with the immediate field shifted left 16. The result is written back to GPR .

#### **Operation**

```

GPR[RT] = GPR[RS] ^ (IMMEDIATE << 16);

```

# Flags Setting

None

## **Exceptions**

# 3.1.2 X86-SEMANTIC INSTRUCTIONS

6

# 3.1.2.1 XADC[I][R] - X86 Add with Carry

5

# **Encoding**

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0                       |

|-------------------|--------------------------------------------|-------|-------|-------|------|--------|---------------------------|

| XADC:<br>XADCR:   | 100000 <sub>2</sub><br>100010 <sub>2</sub> | RS    | RT    | RD    | 0002 | DPcntl | ADC<br>10001 <sub>2</sub> |

|                   | 6                                          | 5     | 5     | 5     | 3    | 3      | 5                         |

|                   |                                            |       |       |       |      |        |                           |

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:06                      |

| XADCI:<br>XADCIR: | 100001 <sub>2</sub><br>100011 <sub>2</sub> | RS    | Const | RD    | 0002 | DPcntl | ADC<br>10001,             |

5

#### **Format**

5

3

3

5

# **Description**

The contents of GPR are added to either the contents of GPR or the immediate value specified in depending on the primary opcode. The EFLAGS.CF is also added to the result.

# **Operation**

| GPR[RD] | = | GPR[RS] | + | GPR[RT] | + | CF |

|---------|---|---------|---|---------|---|----|

| GPR[RD] | = | GPR[RS] | + | Const   | + | CF |

# Flags Setting

**CCarith**

# **Exceptions**

## 3.1.2.2 XADD[I][R] - X86 Add

# **Encoding**

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8      | 7:5    | 4:0                       |

|-------------------|--------------------------------------------|-------|-------|-------|-----------|--------|---------------------------|

| XADD:<br>XADDR:   | 100000 <sub>2</sub><br>100010 <sub>2</sub> | RS    | RT    | RD    | 0002      | DPcntl | ADD<br>10000,             |

|                   | 6                                          | 5     | 5     | 5     | 3         | 3      | 5                         |

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8      | 7:5    | 4:06                      |

| XADDI:<br>XADDIR: | 100001 <sub>2</sub><br>100011 <sub>2</sub> | RS    | Const | RD    | $000_{2}$ | DPcntl | ADD<br>10000 <sub>2</sub> |

|                   | 0                                          | ~     | ~     | ~     | 0         | 0      | ~                         |

#### **Format**

| XADD  | RD,RS,RT |

|-------|----------|

| XADDI | RD,RS,2  |

# **Description**

The contents of GPR RS are added to either the contents of GPR or the immediate value specified in depending on the primary opcode.

#### **Operation**

| GPR[RD] | = GPR[RS] + GPR[RT] |

|---------|---------------------|

| GPR[RD] | = GPR[RS] + Const   |

# **Flags Setting**

**CCarith**

### **Exceptions**

## 3.1.2.3 XAND[I][R] - X86 And

6

### **Encoding**

|                   | 31:26                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0           |

|-------------------|----------------------------|-------|-------|-------|------|--------|---------------|

| XAND:<br>XANDR:   | $100000_{2} \\ 100010_{2}$ | RS    | RT    | RD    | 0002 | DPcntl | AND<br>10100, |

|                   | 6                          | 5     | 5     | 5     | 3    | 3      | 5             |

|                   |                            |       |       |       |      |        |               |

| ·                 | 31:26                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:06          |

| XANDI:<br>XANDIR: | $100001_{2} \\ 100011_{2}$ | RS    | Const | RD    | 0002 | DPcntl | AND<br>10100, |

5 5 5

#### **Format**

3

5

# **Description**

The contents of GPR RS are logically ANDed to either the contents of GPR RT or the value immediate specified in depending on the primary opcode.

# Operation

# **Flags Setting**

CClog

# **Exceptions**

#### 3.1.2.4 XCMPS - X86 A-Stage Compare String

#### **Encoding**

|        | 31:26   | 25:21 | 20:16 | 15:11              | 10:8             | 7:5    | 4:0             |

|--------|---------|-------|-------|--------------------|------------------|--------|-----------------|

| XCMPS: | 1000002 | RS    | RT    | XXXXX <sub>2</sub> | $\mathbf{XXX}_2$ | DPcntl | XCMPS<br>01001, |

|        | 6       | 5     | 5     | 5                  | 3                | 3      | 5               |

#### **Format**

|           |         | <br> |  |  |

|-----------|---------|------|--|--|

| ***       | D 0 D E |      |  |  |

| V ( '   \ | DC DT   |      |  |  |

| XCMPS     | LO'LI   |      |  |  |

|           |         |      |  |  |

#### **Description**

If the COUNT register modulo TSR.AS is not zero then it is decremented by one. The contents of GPR are compared in the to the contents of GPR according to the size specified field as described in the following table. If any of the conditions to terminate or by the interrupt an x86 string compare are true then the instruction is nullified and the translator is signalled to stop generating the sequence for a repeat string and control is transferred to microcode. The conditions under which a string compare terminate are either the COUNT register modulo TSR.AS is zero or the comparison results in equality and TSR.REPN is set or the comparison results in inequality and TSR.REPN is clear. The conditions under which a string compare is interrupted is an external interrupt or debug trap. If the string compare is interrupted or a debug trap is triggered before the terminating condition is met then hardware will set XCR[STRINT\_BIT] at the .T that completes the current x86 instruction; IP is not advanced in this case. See the operation description below.

| DPcntl | Mnemonic | Compare    |

|--------|----------|------------|

| 0002   | 32       | 31:0       |

| 0012   | 16       | 15:0       |

| 0102   | LL       | 7:0        |

| 1102   | os       | 31 or 15:0 |

**Usage Note:** XCMPS is needed to allow the translator to generate the instruction sequence for x86 string compares and scan strings.

A sample usage is

MTCNT ECX // mod AS automatically

XPOP.8L.AS tmp2,DSdesc,ESI,1,str\_testcnt XPOP.8L.AS tmp3,ESdesc,DSI,1,str\_testcnt

XCMPS.8L tmp2,tmp3

which loads the COUNT register with CX or ECX based on the address size, then checks for COUNT equal to zero and if not zero then loads a byte from DS:[E]SI and from ES:[E]DI and

compares the two bytes. The loads and the compare are repeatedly generated by the translator until COUNT goes to zero or the terminating condition of equality is reached or there is an interrupt or debug trap. Note that XCMPS does not modify EFLAGS, microcode must determine if the original count in [E]CX was non-zero and set EFLAGS in that case.

### **Operation**

```

if (COUNT.AS != 0) {

COUNT = COUNT - 1;

}

REP_DONE = (COUNT.AS == 0 or not((GPR[ ] == GPR[ ]) ^ TSR.REPN));

if (REP_DONE or interrupt or IT or TF or DBRKPT) {

send signal to xlator to stop;

nullify inst;

nullify pipeline;

transfer control to corresponding microcode entry point;

}

```

//--The following action taken at .T that completes current x86 instruction

```

if (REP_DONE == 0) {

IP          advance;

XCR[STRINT_BIT] = 1;

}

```

#### Flags Setting

None

# **Exceptions**

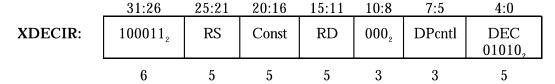

#### 3.1.2.5 XDECIR - X86 Decrement

#### **Encoding**

#### **Format**

XDECIR RD, RS, 1

#### **Description**

The contents of the immediate specified in are subtracted from the contents of GPR RS.

**Usage Note:** XDECIR is needed to perform a single-cycle X86 DEC function. It is the same as a XSUBIR instruction (subtract immediate) except that it sets EFLAGS differently than XSUBIR.

### **Operation**

GPR[RD] = GPR[RS] - Const

### Flags Setting

**CCinc**

#### **Exceptions**

# 3.1.2.6 XIDIV - X86 Signed Divide Step

### **Encoding**

|        | 31:26   | 25:21              | 20:16              | 15:11  | 10:9                     | 8       | 7:5  | 4:0            |

|--------|---------|--------------------|--------------------|--------|--------------------------|---------|------|----------------|

| XIDIV: | 1000002 | XXXXX <sub>2</sub> | XXXXX <sub>2</sub> | 000002 | $\mathbf{x}\mathbf{x}_2$ | $0_{2}$ | Cntl | IDIV<br>01110, |

|        | 6       | 5                  | 5                  | 5      | 2                        | 1       | 3    | 5              |

#### **Format**

XIDIV.STEP

#### **Description**

Performs an signed divide of the dividend in (loaded by DMTMD.DVD) by the divisor in (loaded by DMTMD.DVS).. The size of the dividend, divisor, and quotient are specified by the field and summarized in the following table. The dividend and divisor must be loaded using the DMTMD.DIV.size instruction before issuing XDIV. For 64b-by32b divide the dividend is loaded separately using DMTMD.DIVidend.32 instruction. XIDIV does not allow register indirection or (immediate) values. XIDIV computes as many quotient bits as are specified in the table below. The quotient is written to the LO register, the remainder is written to the HI register. A MFLOU.size instruction is used to get the quotient. A MFHI instruction is used to get the remainder. This DIVIDE instruction is a divide styep instruction that produces one bit of result per cycle. Unlike previous implementations, C3 microcode will control all steps of the multiply process.

| Cntl | Mnemonic | Details             |  |  |  |  |

|------|----------|---------------------|--|--|--|--|

| 0002 | Step     | General Divide Step |  |  |  |  |

| 0012 | OVF      | Detect Divide Ovf   |  |  |  |  |

| 0102 | REM      | Remainder Adjust    |  |  |  |  |

| 0112 | QUO      | Quotient Adjust     |  |  |  |  |

| 1002 |          |                     |  |  |  |  |

| 1012 |          |                     |  |  |  |  |

| 1102 |          |                     |  |  |  |  |

| 1112 |          |                     |  |  |  |  |

#### Flags Setting

None

#### **Exceptions**

# 3.1.2.7 XIMUL[I] - X86 Signed Multiply Step

### **Encoding**

| ,       | 31:26   | 25:21 | 20:16 | 15:11  | 10:9            | 8       | 7:5  | 4:0            |

|---------|---------|-------|-------|--------|-----------------|---------|------|----------------|

| XIMUL:  | 1000002 | RS    | RT    | 000002 | $\mathbf{XX}_2$ | $0_{2}$ | Cntl | IMUL<br>01100, |

|         | 6       | 5     | 5     | 5      | 2               | 1       | 3    | 5              |

| ,       | 31:26   | 25:21 | 20:16 | 15:11  | 10:9            | 8       | 7:5  | 4:0            |

| XIMULI: | 1000012 | RS    | Const | 000002 | $\mathbf{XX}_2$ | $0_{2}$ | Cntl | IMUL<br>01100, |

|         | 6       | 5     | 5     | 5      | 2               | 1       | 3    | 5              |

#### **Format**

| XIMUL  | RS,RT |  |  |

|--------|-------|--|--|

| XIMULI | RS,2  |  |  |

# **Description**

Performs a signed multiply of the operands in the MUL operand registers. The product is written to the LO register. The size of the factors and product are specified by the field and summarized in the following table. XIMUL does not allow register indirection. If is used it must be coded as IMMED.

| Cntl | Mnemonic | Info                              |

|------|----------|-----------------------------------|

| [2]  | First    | First Multiply Clock (choose ops) |

| [1]  | LastClk  | Load result into LO               |

| [0]  |          |                                   |

# **Operation**

#### Flags Setting

None

### **Exceptions**

## 3.1.2.8 XMUL - X86 Unsigned Multiply Step

### **Encoding**

XMUL:

| 31:26   | 25:21 | 20:16 | 15:11  | 10:9            | 8                          | 7:5  | 4:0           |

|---------|-------|-------|--------|-----------------|----------------------------|------|---------------|

| 1000002 | RS    | RT    | 000002 | $\mathbf{XX}_2$ | $0_{\scriptscriptstyle 2}$ | Cntl | MUL<br>01101, |

| 6       | 5     | 5     | 5      | 2               | 1                          | 3    | 5             |

#### **Format**

|           |         |  | <br> |

|-----------|---------|--|------|

| XMUL      | RS RT   |  |      |

| 771.10 11 | 1(0,1(1 |  |      |

### **Description**

Performs an unsigned multiply of and . of the factors and product are specified by the XIMUL does not allow register indirection. If

and . The product is written to the LO register. The size d by the field and summarized in the following table. ection. If is used it must be coded as IMMED.

| Cntl | Mnemonic | Info                              |

|------|----------|-----------------------------------|

| [2]  | First    | First Multiply Clock (choose ops) |

| [1]  | LastClk  | Load result into LO               |

| [0]  |          |                                   |

# Operation

### **Flags Setting**

None.

#### **Exceptions**

#### 3.1.2.9 XINCIR - X86 Increment

### **Encoding**

31:26 25:21 20:16 15:11 10:8 7:5 4:0 XINCIR: 100011, RS RD **DPcntl INC** Const 000, 01000, 5 5 3 5 6 5 3

#### **Format**

| VTMCTD | DN DC 1 |  |  |

|--------|---------|--|--|

| XINCIR | VD'VD'T |  |  |

### Description

The contents of the immediate specified in are added to the contents of GPR RS.

**Usage Note:** XINCIR is needed to perform a single-cycle X86 INC function. It is the same as a XADDIR instruction (add immediate) except that it sets EFLAGS differently than XADDIR.

#### **Operation**

GPR[RD] = GPR[RS] + Const

### **Flags Setting**

**CCinc**

## **Exceptions**

# 3.1.2.10X8NOR[I][R] - X86 NOR

### **Encoding**

|                     | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0           |

|---------------------|--------------------------------------------|-------|-------|-------|------|--------|---------------|

| X8NOR:<br>X8NORR:   | 100000 <sub>2</sub><br>100010 <sub>2</sub> | RS    | RT    | RD    | 0002 | DPcntl | NOR<br>10111, |

|                     | 6                                          | 5     | 5     | 5     | 3    | 3      | 5             |

|                     | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:06          |

| X8NORI:<br>X8NORIR: | 100001 <sub>2</sub><br>100011 <sub>2</sub> | RS    | Const | RD    | 0002 | DPcntl | NOR<br>10111, |

|                     | 6                                          | 5     | 5     | 5     | 3    | 2      | 5             |

#### **Format**

| X8NOR  | RD,RS,RT |                         |

|--------|----------|-------------------------|

| X8NORI | RD,RS,0  | // Same as RD = NOT(RS) |

# **Description**

The contents of GPR are logically NORed with the immediate value specified in depending.

**Usage Note:** By specifying a constant of zero, this instruction directly performs an X86 NOT instruction function. This is the intended function of this instruction.

## **Operation**

```

GPR[RD] = ~ (GPR[RS] | GPR[RT])

GPR[RD] = ~ (GPR[RS] | Const)

```

## Flags Setting

None

#### **Exceptions**

## 3.1.2.11X8OR[I][R] - X86 OR

# **Encoding**

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8      | 7:5    | 4:0          |

|-------------------|--------------------------------------------|-------|-------|-------|-----------|--------|--------------|

| X8OR:<br>X8ORR:   | 100000 <sub>2</sub><br>100010 <sub>2</sub> | RS    | RT    | RD    | 0002      | DPcntl | OR<br>10101, |

|                   | 6                                          | 5     | 5     | 5     | 3         | 3      | 5            |

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8      | 7:5    | 4:06         |

| X8ORI:<br>X8ORIR: | 100001 <sub>2</sub><br>100011,             | RS    | Const | RD    | $000_{2}$ | DPcntl | OR<br>10101, |

|                   | 6                                          | 5     | 5     | 5     | 3         | 3      | 5            |

#### **Format**

| X8OR  | RD,RS,RT |                   |

|-------|----------|-------------------|

| X8ORI | RD,RS,0  | // Moves RS to RD |

# **Description**

The contents of GPR RS are logically ORed to either the contents of GPR RT or the value immediate specified in depending on the primary opcode.

### **Operation**

| GPR[RD] | = | GPR[RS] | GPR[RT] |  |

|---------|---|---------|---------|--|

| GPR[RD] | = | GPR[RS] | Const   |  |

# **Flags Setting**

**CClog**

### **Exceptions**

## 3.1.2.12 XRCL - X86 Rotate Left Thru Carry

### **Encoding**

|                   | 31:26                                      | 25:21 | 20:16  | 15:11 | 10:8 | 7:5    | 4:06          |

|-------------------|--------------------------------------------|-------|--------|-------|------|--------|---------------|

| XRCLI:<br>XRCLIR: | 100001 <sub>2</sub><br>100011 <sub>2</sub> | RS    | 000012 | RD    | 0002 | DPcntl | RCL<br>00110, |

|                   | 6                                          | 5     | 5      | 5     | 3    | 3      | 5             |

#### **Format**

| VDCLT |       |  |  |  |

|-------|-------|--|--|--|

| XRCLI | RD,RS |  |  |  |

#### **Description**

This instruction implements a rotate left through carry of a GPR. The low-order portion of GPR (as defined by the operand size in with the carry flag concatenated on the left end is rotated left

**Usage Note:** This instruction directly performs an X86 RCL instruction of X86 instructions are trapped to the microcode and performed one bit at a time.

**Architecture Note:** This instruction only rotates through carry one bit because (1) it is much harder to do multi-bit rotates through carry, and (2) the multi-bit forms are rarely used in X86.

#### **Operation**

```

Temp_bit = EFLAGS.CF

EFLAGS.CF = MSB(GPR[RS]) // MSB = most significant bit

GPR[RD] = (GPR[RS] << 1) | Temp bit</pre>

```

#### Flags Setting

**CCrl**

#### **Exceptions**

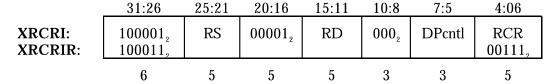

### 3.1.2.13XRCR - X86 Rotate Right Thru Carry

### **Encoding**

#### **Format**

| RD, RS |

|--------|

|--------|

#### **Description**

This instruction implements a rotate right through carry of a GPR.. The low-order portion of GPR (as defined by the operand size in with the carry flag concatenated on the right end is rotated right

**Usage Note:** This instruction directly performs an X86 RCR instruction of . The multi-bit X86 instructions are trapped to the emulator and performed one bit at a time.

**Architecture Note:** This instruction only rotates through carry one bit because (1) it is much harder to do multi-bit rotates through carry, and (2) the mult-bit forms are rarely used in X86.

#### **Performance**

If there is no data dependency stall, this instruction executes in one clock.

#### Operation

```

Temp = EFLAGS.CF << N // N = 32, 16, or 8 depending on DPcntl EFLAGS.CF = GPR[RS] & 1 GPR[RD] = Temp | (GPR[RS] >> 1)

```

#### Flags Setting

**CCrr**

#### **Exceptions**

## 3.1.2.14XROL[I][R] - X86 Rotate Left

## **Encoding**

|                    | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0           |

|--------------------|--------------------------------------------|-------|-------|-------|------|--------|---------------|

| XROL:<br>XROLR:    | 100000 <sub>2</sub><br>100010 <sub>2</sub> | RS    | RT    | RD    | 0002 | DPcntl | ROL<br>00100, |

|                    | 6                                          | 5     | 5     | 5     | 3    | 3      | 5             |

|                    | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:06          |

| XROLI:<br>XROLIR:: | 100001 <sub>2</sub><br>100011 <sub>2</sub> | RS    | Const | RD    | 0002 | DPcntl | ROL<br>00100, |

|                    | 6                                          | 5     | 5     | 5     | 3    | 3      | 5             |

#### **Format**

| OL RD,RS,RT |

|-------------|

| OLI RD,RS,2 |

# **Description**

This instruction implements a rotate left of a GPR. The low-order portion of GPR by the operand size in is rotated left the value in GPR or modulo 32.

#### Operation

$\overline{\text{Temp}} = xxxxxx$

### **Flags Setting**

CCrl

### **Exceptions**

# 3.1.2.15XROR[I][R] - X86 Rotate Right

## **Encoding**

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0           |

|-------------------|--------------------------------------------|-------|-------|-------|------|--------|---------------|

| XROR:<br>XRORR:   | 100000 <sub>2</sub><br>100010 <sub>2</sub> | RS    | RT    | RD    | 0002 | DPcntl | ROR<br>00101, |

|                   | 6                                          | 5     | 5     | 5     | 3    | 3      | 5             |

| į                 | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:06          |

| XRORI:<br>XRORIR: | $100001_{2} \\ 100011_{2}$                 | RS    | Const | RD    | 0002 | DPcntl | ROR<br>00101, |

| ·                 | 6                                          | 5     | 5     | 5     | 3    | 3      | 5             |

#### **Format**

| XROR  | RD,RS,RT |

|-------|----------|

| XRORI | RD,RS,2  |

# **Description**

This instruction implements a rotate right of a GPR. The low-order portion of GPR as defined by the operand size in is rotated right the value in GPR or modulo 32.

#### Operation

Temp = xxxxxx

### Flags Setting

**CCrr**

# **Exceptions**

# 3.1.2.16XSBB[I][R] - X86 Subtract with Borrow

# **Encoding**

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0           |

|-------------------|--------------------------------------------|-------|-------|-------|------|--------|---------------|

| XSBB:<br>XSBBR:   | 100000 <sub>2</sub><br>100010 <sub>2</sub> | RS    | RT    | RD    | 0002 | DPcntl | SBB<br>10011, |

|                   | 6                                          | 5     | 5     | 5     | 3    | 3      | 5             |

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0           |

| XSBBI:<br>XSBBIR: | $100001_{2} \\ 100011_{2}$                 | RS    | Const | RD    | 0002 | DPcntl | SBB<br>10011, |

|                   | 6                                          | 5     | 5     | 5     | 3    | 3      | 5             |

#### **Format**

# **Description**

The contents of GPR or the immediate specified in , depending on the primary opcode, are subtracted from the contents of GPR .

# Operation

| GPR[RD] | = | GPR[RS] | _ | GPR[RT] | _ | EFLAGS.CF |

|---------|---|---------|---|---------|---|-----------|

| GPR[RD] | = | GPR[RS] | _ | Const   | _ | EFLAGS.CF |

# Flags Setting

**CCarith**

### **Exceptions**

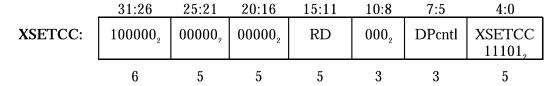

#### 3.1.2.17XSETCC - X86 SETcc

### **Encoding**

#### **Format**

|         |     | <br> |  |  |

|---------|-----|------|--|--|

| XSETCC  | RD  |      |  |  |

| 7701100 | 110 |      |  |  |

### Description

The contents of GPR (expected to be coded as 0) are logically ORed to the contents of GPR (also expected to be coded as 0), the low order bit of the result is then logically ORed with the condition specified by the tttn field of the IIR.

**Architecture Note**: This instruction is intended for the translator to implement the x86 SETcc instruction, its use in microcode is limited by the fact that the condition to test is specified in the tttn field of IIR.

**Architecture Differences:** this instruction is new to C2.

#### **Operation**

#### Flags Setting

None.

#### **Exceptions**

# 3.1.2.18XSHL[I][R] - X86 Shift Left Logical

### **Encoding**

|                    | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0                       |

|--------------------|--------------------------------------------|-------|-------|-------|------|--------|---------------------------|

| XSHL:<br>XSHLR:    | $100000_{2} \\ 100010_{2}$                 | RS    | RT    | RD    | 0002 | DPcntl | SLL<br>00000,             |

|                    | 6                                          | 5     | 5     | 5     | 3    | 3      | 5                         |

|                    | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0                       |

| XSHLI:<br>XSHLIR:: | 100001 <sub>2</sub><br>100011 <sub>2</sub> | RS    | Const | RD    | 0002 | DPcntl | SLL<br>00000 <sub>2</sub> |

|                    | 6                                          | 5     | 5     | 5     | 3    | 3      | 5                         |

#### **Format**

| XSHL  | RD,RS,RT |

|-------|----------|

| XSHLI | RD,RS,2  |

# **Description**

This instruction implement a shift left of a GPR. The low-order portion of GPR  $\,$  as defined by the operand size in  $\,$  is shifted left the value in GPR  $\,$  or  $\,$  modulo 32.

#### **Operation**

GPR[RD] = xxxxx

### **Flags Setting**

**CCshl**

# **Exceptions**

# 3.1.2.19XSAR[I][R] - X86 Shift Right Arithmetic

### **Encoding**

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0           |

|-------------------|--------------------------------------------|-------|-------|-------|------|--------|---------------|

| XSAR:<br>XSARR:   | 100000 <sub>2</sub><br>100010 <sub>2</sub> | RS    | RT    | RD    | 0002 | DPcntl | SRA<br>00011, |

|                   | 6                                          | 5     | 5     | 5     | 3    | 3      | 5             |

|                   | 31:26                                      | 25:21 | 20:16 | 15:11 | 10:8 | 7:5    | 4:0           |

| XSARI:<br>XSARIR: | 100001 <sub>2</sub><br>100011 <sub>2</sub> | RS    | Const | RD    | 0002 | DPcntl | SRA<br>00011, |

|                   | 6                                          | 5     | 5     | 5     | 3    | 3      | 5             |

#### **Format**

| XSAR  | RD,RS,RT |  |  |

|-------|----------|--|--|

| XSARI | RD,RS,2  |  |  |

## **Description**

This instruction implement a shift right arithmetic of a GPR. The low-order portion of GPR as defined by the operand size in is shifted right arithmetically the value in GPR or modulo 32.

#### **Operation**

GPR[RD] = xxxxxx

# **Flags Setting**

**CCsar**

# **Exceptions**

## 3.1.2.20XSHR[I][R] - X86 Shift Right Logical

## **Encoding**