# Data Sheet

VT1613

2-Channel AC'97

Codec

Revision 1.0 December 6, 2004

VIA TECHNOLOGIES, INC.

# **Copyright Notice:**

Copyright © 2004 VIA Technologies Incorporated. All Rights Reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of VIA Technologies Incorporated. The material in this document is for information only and is subject to change without notice. VIA Technologies Incorporated reserves the right to make changes in the product design without reservation and without notice to its users.

VT1613 may only be used to identify a product of VIA Technologies, Incorporated.

is a registered trademark of VIA Technologies, Incorporated.

Windows XP™, Windows 2000™, Windows NT™, Windows 98™, and Plug and Play™ are registered trademarks of Microsoft Corporation. PCI™ is a registered trademark of the PCI Special Interest Group.

All trademarks are the properties of their respective owners.

# **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is believed to be accurate and reliable as of the publication date of this document. However, VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

## Offices:

VIA Technologies Incorporated Taiwan Office: 1st Floor, No. 531 Chung-Cheng Road, Hsin-Tien Taipei, Taiwan ROC Tel: 886-2-2218-5452 FAX: 886-2-2218-5453

Home page: http://www.via.com.tw

VIA Technologies Incorporated USA Office: 940 Mission Court Fremont, CA 94539 USA Tel: 510-683-3300 FAX: 510-683-3301 or 510-687-4654

Home Page: http://www.viatech.com

# **REVISION HISTORY**

| <b>Document Release</b> | Date    | Revision                 | Initials |

|-------------------------|---------|--------------------------|----------|

| 1.0                     | 12/6/04 | Initial external release | JM       |

# TABLE OF CONTENTS

| REVISION HISTORY                         | ]   |

|------------------------------------------|-----|

| TABLE OF CONTENTS                        |     |

| LIST OF FIGURES                          | III |

| LIST OF TABLES                           | IV  |

| PRODUCT FEATURES                         | 1   |

| OVERVIEW                                 |     |

| PIN DIAGRAM                              | 3   |

| PIN DESCRIPTIONS                         | 5   |

| REGISTERS                                |     |

| REGISTER OVERVIEW                        |     |

| REGISTER DESCRIPTIONS                    |     |

| VENDOR DEFINED REGISTER (PAGE ID = 00H)  | 26  |

| EXTENDED CODEC REGISTERS (PAGE ID = 01H) | 28  |

| ELECTRICAL SPECIFICATIONS                | 29  |

| DIGITAL DC SPECIFICATIONS                |     |

| ANALOG PERFORMANCE CHARACTERISTICS       | 29  |

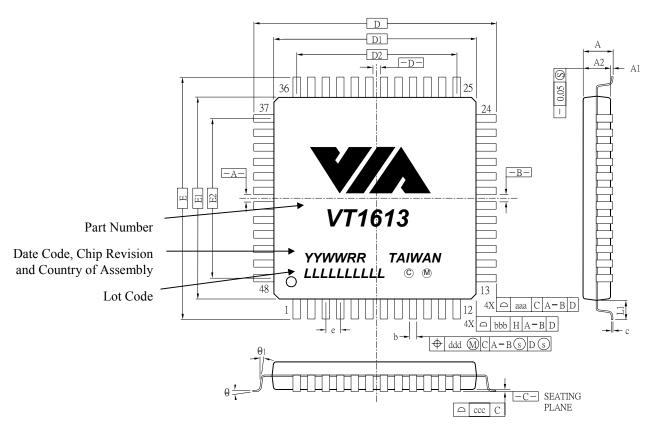

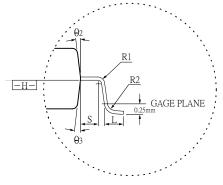

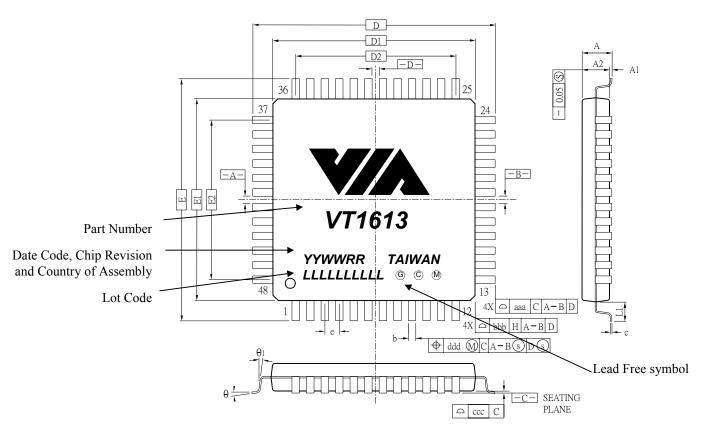

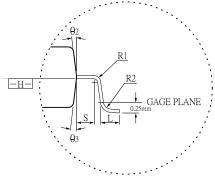

| MECHANICAL SPECIFICATIONS                | 33  |

# **LIST OF FIGURES**

| FIGURE 1. FUNCTIONAL BLOCK DIAGRAM                             |  |

|----------------------------------------------------------------|--|

| FIGURE 2. VT1613 PIN DIAGRAM (TOP VIEW)                        |  |

| FIGURE 3. MECHANICAL SPECIFICATION – 48-PIN LQFP               |  |

| FIGURE 4. MECHANICAL SPECIFICATION FOR LEAD FREE – 48-PIN LOFP |  |

# LIST OF TABLES

| TABLE 1. | PIN LIST (LISTED BY PIN NAME)                      | . 4 |

|----------|----------------------------------------------------|-----|

|          | PIN DESCRIPTIONS                                   |     |

|          | REGISTER MAP                                       |     |

|          | STEREO OUTPUT ATTENUATION                          |     |

|          | STEREO OUTPUT ATTENUATION                          |     |

|          | POWER DOWN CONTROL MAPPING TABLE                   |     |

|          | SPDIF VALIDITY AND CONFIGURATION MAPPING TABLE     |     |

|          | CHANNEL STATUS BIT FROM S/PDIF RX IN CONSUMER MODE |     |

| IADLE 0. | CHANNEL STATUS DIT FROM S/LDIF RA IN CONSUMER MUDE | 4   |

# VT1613 2-Channel AC'97 Codec

#### PRODUCT FEATURES

#### AC'97 V2.3 Audio Codec

Fully compliant with AC'97 Specification, Revision 2.3

## High Audio Quality

- Variable sampling rate converters

- 16-bit independent rate ADC architecture

- 18-bit independent rate DAC architecture

- Integrated Headphone Amps with mute at Front outputs.

#### Various Output Format

- 96KHz DAC for 2 channels

- 48KHz ADC

- Integrated S/PDIF TX with 96K, 48K, 44.1K and 32KHz support

- Integrated S/PDIF RX with 48K, 44.1K and 32KHz support

#### Added-on Function

- 1 integrated MIC biasing transistors

- Add 1.5dB analog gin boost to the headphone Amplifier

- 2 Microphones

- Add GPIO interrupt capability

- 1 GPIO pin

- Direct-Play feature: Play CD through OP Amp of Front Channels

- Analog and Digital power state to select direct-play mode or normal mode

- Play CD during PC power off

#### Power

- EAPD pin support

- Integrated Vref out power down feature

- Integrated Clean-ON™ Power-up de-Pop

- SNR exceeds 90dB

- Low power consumption mode

- 3.3V or 5V analog, 3.3V digital power supply

#### Package

- Pin compatible with VT1612A 2-Channel AC'97 Codec

- 48-Pin LQFP Package

# **OVERVIEW**

VIA Technologies' VT1613 18-bit audio codec conforms to the AC'97 Specification, Revision 2.3 and S/PDIF Input / Output specifications. The VT1613 integrates Sample Rate Converters on all channels. This codec is designed with aggressive power management to achieve low power consumption. When used with a 3.3V analog supply, power consumption is further reduced. The primary applications for this part are desktop and portable personal computers multimedia subsystems.

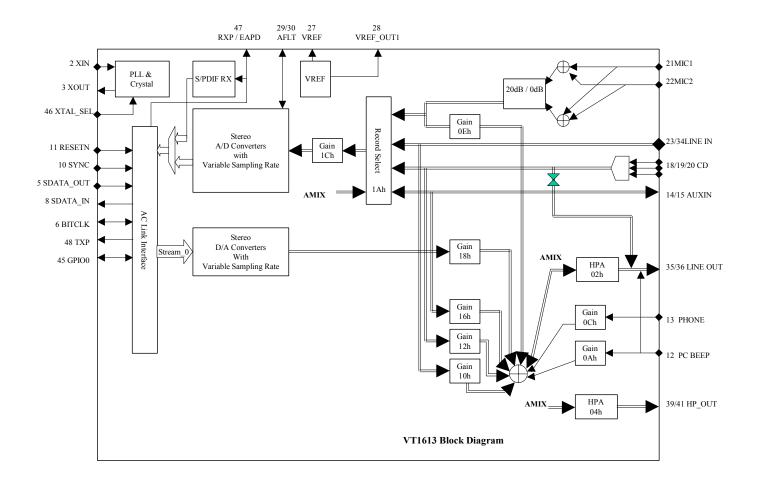

Figure 1. Functional Block Diagram

#### Pin Diagram

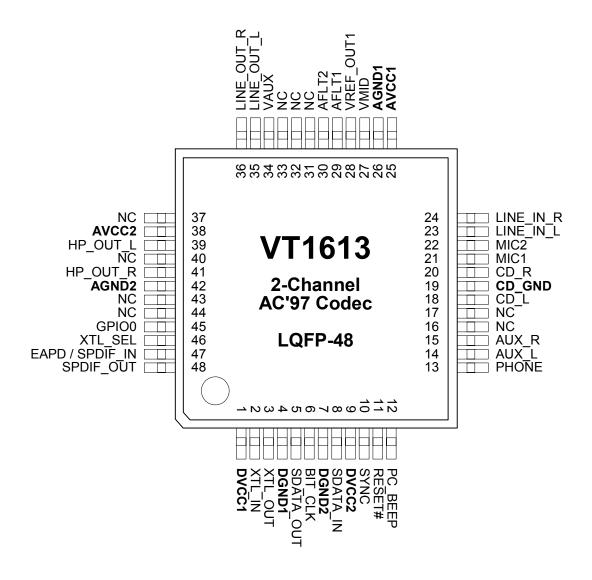

Figure 2. VT1613 Pin Diagram (Top View)

# Pin List

Table 1. Pin List (Listed by Pin Name)

| Pin# | Pin Name           | Туре | Pin#                           | Pin Name  | Type |

|------|--------------------|------|--------------------------------|-----------|------|

| 29   | AFLT1              | О    | 21                             | MIC1      | I    |

| 30   | AFLT2              | О    | 22                             | MIC2      | I    |

| 26   | AGND1              | P    | 16-17, 31-33,<br>37, 40, 43-44 | NC        | _    |

| 42   | AGND2              | P    | 12                             | PCBEEP    | I    |

| 14   | AUX_L              | I    | 13                             | PHONE     | I    |

| 15   | AUX_R              | I    | 11                             | RESET#    | I    |

| 25   | AVCC1              | P    | 8                              | SDATA_IN  | IO   |

| 38   | AVCC2              | P    | 5                              | SDATA_OUT | IO   |

| 6    | BIT_CLK            | IO   | 48                             | SPDIF_OUT | O    |

| 19   | CD_GND             | I    | 10                             | SYNC      | IO   |

| 18   | CD L               | I    | 34                             | VAUX      | I    |

| 20   | CD_R               | I    | 27                             | VMID      | I    |

| 4    | DGND1              | P    | 28                             | VREF_OUT1 | O    |

| 7    | DGND2              | P    | 2                              | XTL_IN    | I    |

| 1    | DVCC1              | P    | 3                              | XTL_OUT   | O    |

| 9    | DVCC2              | P    | 46                             | XTL_SEL   | IO   |

| 47   | EAPD /<br>SPDIF_IN | IO   |                                |           |      |

| 45   | GPIO0              | IO   |                                |           |      |

| 39   | HP_OUT_L           | О    |                                |           |      |

| 41   | HP_OUT_R           | O    |                                |           |      |

| 23   | LINE_IN_L          | I    |                                |           |      |

| 24   | LINE_IN_R          | I    |                                |           |      |

| 35   | LINE_OUT_L         | О    |                                |           |      |

| 36   | LINE_OUT_R         | O    |                                |           |      |

Note: I = Input, O = Output, P = Power / Ground, A = Analog

# **Pin Descriptions**

**Table 2. Pin Descriptions**

| Pin # | Pin Name           | Type | Description                                                              |

|-------|--------------------|------|--------------------------------------------------------------------------|

| 1     | DVCC1              | P    | Digital Supply Voltage, 3.3V only                                        |

| 2     | XTL_IN             | I    | 24.576 MHz Crystal or 24.576M/14.318MHz clock input                      |

| 3     | XTL_OUT            | О    | 24.576 MHz Crystal                                                       |

| 4     | DGND1              | P    | Digital Ground                                                           |

| 5     | SDATA_OUT          | IO   | AC'97 Serial Data Input Stream                                           |

| 6     | BIT_CLK            | IO   | 12.288 MHz Serial Data Clock (Internal pulled low).                      |

| 7     | DGND2              | P    | Digital Ground                                                           |

| 8     | SDATA_IN           | IO   | AC'97 Output Stream (Internal pulled low).                               |

| 9     | DVCC2              | P    | Digital Supply Voltage, 3.3V only                                        |

| 10    | SYNC               | IO   | 48 KHz Fixed Rate Sync Pulse / LRCLK                                     |

| 11    | RESET#             | I    | AC'97 Master Reset                                                       |

| 12    | PC_BEEP            | I    | PC Speaker Beep Pass Through                                             |

| 13    | PHONE              | I    | Telephony Subsystem Speakerphone                                         |

| 14    | AUX_L              | IO   | Auxiliary Audio Left Channel / Surround Back Left Output                 |

| 15    | AUX_R              | IO   | Auxiliary Audio Right Channel / Surround Back Right Output               |

| 16-17 | NC                 | _    | No Connect                                                               |

| 18    | CD_L               | I    | CD Audio Left Channel                                                    |

| 19    | CD_GND             | I    | CD Audio Analog Ground                                                   |

| 20    | CD_R               | I    | CD Audio Right Channel                                                   |

| 21    | MIC1               | I    | Desktop Microphone                                                       |

| 22    | MIC2               | I    | Second Microphone                                                        |

| 23    | LINE_IN_L          | I    | Line In Left Channel                                                     |

| 24    | LINE_IN_R          | I    | Line In Right Channel                                                    |

| 25    | AVCC1              | P    | Analog Supply Voltage, 5V or 3.3V                                        |

| 26    | AGND1              | P    | Analog Ground                                                            |

| 27    | VMID               | I    | Mixer Reference Voltage                                                  |

| 28    | VREF_OUT1          | О    | Reference Voltage Output                                                 |

| 29    | AFLT1              | О    | Left Channel Anti-Aliasing Filter Capacitor                              |

| 30    | AFLT2              | О    | Right Channel Anti-Aliasing Filter Capacitor                             |

| 31-33 | NC                 |      | No Connect                                                               |

| 34    | VAUX               | I    | Power-off CD enable                                                      |

| 35    | LINE_OUT_L         | О    | Line Out Left Channel (with built-in HP driver)                          |

| 36    | LINE_OUT_R         | O    | Line Out Right Channel (with built-in HP driver)                         |

| 37    | NC                 | _    | No Connect                                                               |

| 38    | AVCC2              | P    | Analog Supply Voltage, 5V or 3.3V                                        |

| 39    | HP_OUT_L           | O    | HP Out Left Channel                                                      |

| 40    | NC                 | _    | No Connect                                                               |

| 41    | HP_OUT_R           | О    | HP Out Right Channel                                                     |

| 42    | AGND2              | P    | Analog Ground                                                            |

| 43-44 | NC                 | _    | No Connect                                                               |

| 45    | GPIO0              | IO   | GPIO0 (Internal pulled high)                                             |

| 46    | XTL_SEL            | IO   | Crystal Selection (Internal pulled high)                                 |

| 47    | EAPD /<br>SPDIF_IN | IO   | External Power Amplifier Power Down (Internal pulled high) / SPDIF input |

| 48    | SPDIF_OUT          | О    | PCM/Non-Audio Sony/Philips Digital I/F Output (Internal pulled high)     |

# **REGISTERS**

# **Register Overview**

The following tables summarize all on-chip registers.

Table 3. Register Map

| Index | Register<br>Name               | D15     | D14   | D13   | D12   | D11   | D10   | D9   | D8   | <b>D7</b> | D6    | D5   | D4   | D3   | D2    | D1    | D0    |

|-------|--------------------------------|---------|-------|-------|-------|-------|-------|------|------|-----------|-------|------|------|------|-------|-------|-------|

| 00h   | Reset                          | _       | _     | _     | _     | _     |       | _    | ID8  | _         | ID6   | _    | _    | _    | _     | _     | _     |

| 02h   | Stereo Output<br>Volume        | Mute    |       | _     | ML4   | ML3   | ML2   | ML1  | ML0  | _         | _     | _    | MR4  | MR3  | MR2   | MR1   | MR0   |

| 04h   | HP Stereo<br>Output Volume     | Mute    |       | _     | ML4   | ML3   | ML2   | ML1  | ML0  | _         | _     | _    | MR4  | MR3  | MR2   | MR1   | MR0   |

| 0Ah   | PC Beep<br>Volume              | Mute    |       | _     |       |       |       | _    |      | _         | _     | _    | PV3  | PV2  | PV1   | PV0   | _     |

| 0Ch   | Phone Volume                   | Mute    | _     | _     | _     | _     | _     | _    | _    | _         | _     | _    | GN4  | GN3  | GN2   | GN1   | GN0   |

| 0Eh   | Mic In Volume                  | Mute    | _     | _     | GL4   | GL3   | GL2   | GL1  | GL0  | Mute      | 20dB  | _    | GN4  | GN3  | GN2   | GN1   | GN0   |

| 10h   | Line In Volume                 | Mute    |       | _     | GL4   | GL3   | GL2   | GL1  | GL0  | _         | _     | _    | GR4  | GR3  | GR2   | GR1   | GR0   |

| 12h   | CD In Volume                   | Mute    | 1     | _     | GL4   | GL3   | GL2   | GL1  | GL0  | _         | _     | _    | GR4  | GR3  | GR2   | GR1   | GR0   |

| 16h   | Aux In Volume                  | Mute    | _     | _     | GL4   | GL3   | GL2   | GL1  | GL0  | _         | _     | _    | GR4  | GR3  | GR2   | GR1   | GR0   |

| 18h   | PCM Out<br>volume              | Mute    | _     | _     | GL4   | GL3   | GL2   | GL1  | GL0  | _         | _     | _    | GR4  | GR3  | GR2   | GR1   | GR0   |

| 1Ah   | Record Select                  | _       | _     | _     | _     | _     | SL2   | SL1  | SL0  | _         | _     | _    | _    | _    | SR2   | SR1   | SR0   |

| 1Ch   | Record Gain                    | Mute    | _     | —     | _     | GL3   | GL2   | GL1  | GL0  | _         | _     | _    | _    | GR3  | GR2   | GR1   | GR0   |

| 20h   | General Purpose                | _       |       | _     | _     | DRSS1 | DRSS0 | _    | MS   | LPBK      | _     | _    | _    | _    | _     | _     | _     |

| 24h   | Audio Int. &<br>Paging         | I4      | 13    | I2    | _     | 10    | _     | _    | _    | _         | _     | _    | _    | PG3  | PG2   | PG1   | PG0   |

| 26h   | Power Down &<br>Status         | EAPD    |       | PR5   | PR4   | PR3   | PR2   | PR1  | PR0  | _         | _     | _    |      | REF  | ANL   | DAC   | ADC   |

| 28h   | Extended Audio ID              |         |       | _     |       | REV1  | REV0  | _    |      | _         | _     | _    |      | _    | SPDIF | DRA   | VRA   |

| 2Ah   | Ext. Audio Stat<br>/ Control   | VCFG    | _     | _     | _     | _     | SPCV  | _    | _    | _         | _     | SSA1 | SSA0 | _    | SPDIF | DRA   | VRA   |

| 2Ch   | PCM Front<br>DAC Rate          | SR15    | SR14  | SR13  | SR12  | SR11  | SR10  | SR9  | SR8  | SR7       | SR6   | SR5  | SR4  | SR3  | SR2   | SR1   | SR0   |

| 32h   | PCM LR ADC<br>Rate             | SR15    | SR14  | SR13  | SR12  | SR11  | SR10  | SR9  | SR8  | SR7       | SR6   | SR5  | SR4  | SR3  | SR2   | SR1   | SR0   |

| 3Ah   | S/PDIF Control                 | V       | DRS   | SSR1  | SSR0  | L     | CC6   | CC5  | CC4  | CC3       | CC2   | CC1  | CC0  | PRE  | COPY  | /PCM  | PRO   |

| 5Ah   | Vendor<br>Reserved<br>Register | D15     | AROMT | DROMT | _     | _     | BPDC  | _    | _    | INIT      | D2AL  | _    | _    | IB1  | IB0   | EQADC | EQDAC |

| 5Ch   | Vendor<br>Reserved<br>Register | VRPD1   | BIST  | _     | _     | _     | _     | _    | _    | HPE1      | _     | HPE0 | _    | _    | STMIC | _     | SMD   |

|       | PCI SVID                       | PVI15   | PVI14 | PVI13 | PVI12 | PVI11 | PVI10 | PVI9 | PVI8 | PVI7      | PVI6  | PVI5 | PVI4 | PVI3 | PVI2  | PVI1  | PVI0  |

| 64h   | PCI SID                        | PI15    | PI14  | PI13  | PI12  | PI11  | PI10  | PI9  | PI8  | PI7       | PI6   | PI5  | PI4  | PI3  | PI2   | PI1   | PIO   |

| 66h   | S/PDIF RX<br>Status            | L       | CC6   | CC5   | CC4   | CC4   | CC2   | CC1  | CC0  | Model     | Mode0 | Pre2 | Pre1 | Pre0 | COPY  | /PCM  | PRO   |

| 68h   | S/PDIF RX<br>Status            | Invalid | Lock  | Cal   | Ca0   | Fs3   | Fs2   | Fs1  | Fs0  | Cn3       | Cn2   | Cn1  | Cn0  | Sn3  | Sn2   | Sn1   | Sn0   |

| 6Ah   | S/PDIF RX<br>Control           | En      | D14   | D13   | D12   | D11   | _     | D9   | D8   | _         | _     | _    | _    |      | _     | D1    | SCMS  |

| 6Ch   | DAC Slot<br>Mapping            | FD3     | FD2   | FD1   | FD0   | _     | _     | _    |      | _         | _     | _    | _    | _    | _     | _     | _     |

| Index | Register<br>Name            | D15   | D14   | D13  | D12  | D11 | D10    | <b>D</b> 9 | D8   | <b>D7</b> | <b>D6</b> | <b>D5</b> | D4   | D3   | D2   | D1    | D0   |

|-------|-----------------------------|-------|-------|------|------|-----|--------|------------|------|-----------|-----------|-----------|------|------|------|-------|------|

| 6Eh   | ADC Slot<br>Mapping         | _     | _     | _    | _    | _   | _      | _          | _    | _         | _         |           |      |      | _    | _     | MV   |

| 70h   | ADC / SPDIF<br>RX Left Peak | D15   | D14   | D13  | D12  | D11 | D10    | D9         | D8   | D7        | D6        | D5        | D4   | D3   | D2   | D1    | D0   |

| / 411 | PLL Setting /<br>Debugging  | DAOVF | ADOVF | _    | _    | _   | CLK22M | BOUT       | BIN  | XIN       | TEST2     | RDY2      | EN2  | CS   | BYP  | RDY1  | EN1  |

| 76h   | Miscellaneous               | _     | _     | MS2R | MS1R | _   | _      | MS2L       | MS1L | L8ITP     | CD2SP     | TADC      | TDAC |      | GDAC | FRONT | _    |

| 78h   | GPIO Control                | GSI   | GOS   | _    | _    | _   | _      | _          | GW0  | _         | -         |           | GP0  | _    | _    | _     | GC0  |

| 7Ah   | GPIO Status                 | _     | _     | _    | _    | _   | _      | _          | GIS0 | GO0       | _         | _         | _    | _    | _    | _     | GI0  |

| 7Ch   | Vendor ID1                  | F7    | F6    | F5   | F4   | F3  | F2     | F1         | F0   | S7        | S6        | S5        | S4   | S3   | S2   | S1    | S0   |

| 7Eh   | Vendor ID2                  | T7    | T6    | T5   | T4   | T3  | T2     | T1         | T0   | REV7      | REV6      | REV5      | REV4 | REV3 | REV2 | REV1  | REV0 |

#### **Register Descriptions**

The register tables in this section also document the power-on default value ("Default") and access type ("Acc") for each register. All offset and default values are shown in hexadecimal unless otherwise indicated. Access type definitions used are RW (Read / Write), RO (Read / Only), "—" for reserved used (essentially the same as RO), and RWC (or just WC) (Read / Write 1's to Clear individual bits). Registers indicated as RW may have some read only bits that always read back a fixed value (usually 0 if unused); registers designated as RWC or WC may have some read-only or read write bits (see individual register descriptions for details).

#### Reset

Index: 00h Default Value: 0140h / 0140h

The Reset register is used to configure the hardware to a known state or to read the ID code of the part. ID8 and ID6 are set to 1b to report that the ADC and DAC are 18-bit resolution respectively. Writing data to this register will set all the mixer registers to their default values. For detailed description of the bits set to 0b, please refer to AC'97 Rev. 2.3 spec.

| Bit  | Attr. | Description |

|------|-------|-------------|

| 15:9 | RO    | -Reserved-  |

| 8    | RO    | 18-bit ADC  |

| 7    | RO    | -Reserved-  |

| 6    | RO    | 18-bit DAC  |

| 5:0  | RO    | -Reserved-  |

#### **Stereo Output Control**

Index: 02h Default Value: 8000h / 0000h

| Bit   | Attr. | Description                                                                                                                                                                                                                                                                             |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | RW    | Stereo Output Control                                                                                                                                                                                                                                                                   |

|       |       | 0: Normal                                                                                                                                                                                                                                                                               |

|       |       | 1: Mute                                                                                                                                                                                                                                                                                 |

| 14:13 | RO    | -Reserved-                                                                                                                                                                                                                                                                              |

| 12:8  | RW    | Master Output (Left Channel) Volume Control  These five bits select the level of attenuation applied to the Left channel of the Stereo Output signal.  The level of attenuation is programmable from 0dB to -46.5dB in 1.5dB increments, providing a total of 32 programmable levels.   |

| 7:5   | RO    | -Reserved-                                                                                                                                                                                                                                                                              |

| 4:0   | RW    | Master Output (Right Channel) Volume Control  These five bits select the level of attenuation applied to the Right channel of the Stereo Output signal.  The level of attenuation is programmable from 0dB to -46.5dB in 1.5dB increments, providing a total of 32 programmable levels. |

#### **Headphone Stereo Output Control**

Index: 04h Default Value: 8000h / 0000h

| Bit   | Attr. | Description                                                                                               |

|-------|-------|-----------------------------------------------------------------------------------------------------------|

| 15    | RW    | Stereo Output Control                                                                                     |

|       |       | 0: Normal                                                                                                 |

|       |       | 1: Mute                                                                                                   |

| 14:13 | RO    | -Reserved-                                                                                                |

| 12:8  | RW    | Master Output (Left Channel) Volume Control                                                               |

|       |       | These five bits select the level of attenuation applied to the Left channel of the Stereo Output signal.  |

|       |       | The level of attenuation is programmable from 0dB to -46.5dB in 1.5dB increments, providing a total       |

|       |       | of 32 programmable levels.                                                                                |

| 7:5   | RO    | -Reserved-                                                                                                |

| 4:0   | RW    | Master Output (Right Channel) Volume Control                                                              |

|       |       | These five bits select the level of attenuation applied to the Right channel of the Stereo Output signal. |

|       |       | The level of attenuation is programmable from 0dB to -46.5dB in 1.5dB increments, providing a total       |

|       |       | of 32 programmable levels.                                                                                |

**Table 4. Stereo Output Attenuation**

|    | M4 | М3 | M2 | M1 | M0 | Level (dB) |

|----|----|----|----|----|----|------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0.0        |

| 1  | 0  | 0  | 0  | 0  | 1  | -1.5       |

| 2  | 0  | 0  | 0  | 1  | 0  | -3.0       |

| 3  | 0  | 0  | 0  | 1  | 1  | -4.5       |

| 4  | 0  | 0  | 1  | 0  | 0  | -6.0       |

| 5  | 0  | 0  | 1  | 0  | 1  | -7.5       |

|    |    |    | •• |    |    |            |

|    |    | •• | •• | •• | •• |            |

| 28 | 1  | 1  | 1  | 0  | 0  | -42.0      |

| 29 | 1  | 1  | 1  | 0  | 1  | -43.5      |

| 30 | 1  | 1  | 1  | 1  | 0  | -45.0      |

| 31 | 1  | 1  | 1  | 1  | 1  | -46.5      |

#### **PC Beep Input Volume Control**

Index: 0Ah Default Value: 8000h / 8000h

| Bit  | Attr. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | RW    | PC Beep Input Mute Control                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |       | 0: Normal                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |       | 1: Mute                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14:5 | RO    | -Reserved-                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4:1  | RW    | PC Beep Input Volume Control  These four bits select the level of attenuation applied to the PC beep input signal. The level of attenuation is programmable from 0dB to -45dB in 3dB increments, providing a total of 16 programmable levels. The beep gain is set at 0dB when PV[4:1] = 0h. Even though the default of the input volume control is mute, as long as RESET# is active, PC Beep will be passively routed to the line outputs. |

| 0    | RO    | -Reserved-                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### **Phone Input Volume Control**

Index: 0Ch Default Value: 8008h / 8008h

| Bit  | Attr. | Description                                                                                      |

|------|-------|--------------------------------------------------------------------------------------------------|

| 15   | RW    | Phone Input Mute Control                                                                         |

|      |       | 0: Normal                                                                                        |

|      |       | 1: Mute                                                                                          |

| 14:5 | RO    | -Reserved-                                                                                       |

| 4:0  | RW    | Phone Input Volume Control                                                                       |

|      |       | These five bits select the gain applied to the Phone Input signal. The gain is programmable from |

|      |       | -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable levels.                |

#### **MIC Input Volume Control**

Index: 0Eh Default Value: 8808h / 8808h

| Bit   | Attr. | Description                                                                                             |

|-------|-------|---------------------------------------------------------------------------------------------------------|

| 15    | RW    | MIC Input Mute Control                                                                                  |

|       |       | 0: Normal                                                                                               |

|       |       | 1: Mute                                                                                                 |

| 14:13 | RO    | -Reserved-                                                                                              |

| 12:8  | RW    | Left Channel Gain Control                                                                               |

|       |       | These five bits select the gain applied to the LEFT channel of the MIC Input signal. The gain is        |

|       |       | programmable from -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable             |

|       |       | levels. Those bits and bit 7 are only active if STMIC in register 5Ch is set to 1.                      |

| 7     | RW    | 0: Normal                                                                                               |

|       |       | 1: Mute                                                                                                 |

| 6     | RW    | MIC Boost Control                                                                                       |

|       |       | 0: Fixed 20dB gain disabled                                                                             |

|       |       | 1: Fixed 20dB gain enabled                                                                              |

| 5     | RO    | -Reserved-                                                                                              |

| 4:0   | RW    | Mic Input Volume Control                                                                                |

|       |       | These five bits select the gain applied to the Mic Input signal. The gain is programmable from - 34.5dB |

|       |       | to 12dB in 1.5dB increments, providing a total of 32 programmable levels.                               |

## **Line Input Volume Control**

Index: 10h Default Value: 8808h / 8808h

| Bit   | Attr. | Description                                                                                        |

|-------|-------|----------------------------------------------------------------------------------------------------|

| 15    | RW    | Line Input Mute Control                                                                            |

|       |       | 0: Normal                                                                                          |

|       |       | 1: Mute                                                                                            |

| 14:13 | RO    | -Reserved-                                                                                         |

| 12:8  | RW    | Left Channel Gain Control                                                                          |

|       |       | These five bits select the gain applied to the left channel of the Line Input signal. The gain is  |

|       |       | programmable from -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable        |

|       |       | levels.                                                                                            |

| 7:5   | RO    | -Reserved-                                                                                         |

| 4:0   | RW    | Right Channel Gain Control                                                                         |

|       |       | These five bits select the gain applied to the right channel of the Line Input signal. The gain is |

|       |       | programmable from -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable        |

|       |       | levels.                                                                                            |

#### **CD Input Volume Control**

Index: 12h Default Value: 8808h / 8808h

| Bit   | Attr. | Description                                                                                      |

|-------|-------|--------------------------------------------------------------------------------------------------|

| 15    | RW    | CD Input Mute Control                                                                            |

|       |       | 0: Normal                                                                                        |

|       |       | 1: Mute                                                                                          |

| 14:13 | RO    | -Reserved-                                                                                       |

| 12:8  | RW    | Left Channel Gain Control                                                                        |

|       |       | These five bits select the gain applied to the left channel of the CD Input signal. The gain is  |

|       |       | programmable from -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable      |

|       |       | levels.                                                                                          |

| 7:5   | RO    | -Reserved-                                                                                       |

| 4:0   | RW    | Right Channel Gain Control                                                                       |

|       |       | These five bits select the gain applied to the right channel of the CD Input signal. The gain is |

|       |       | programmable from -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable      |

|       |       | levels.                                                                                          |

#### **Auxiliary Input Volume Control**

Index: 16h Default Value: 8808h / 8808h

|       |       | Deliuit value: 000011 000011                                                                                                                                                                                                     |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Attr. | Description                                                                                                                                                                                                                      |

| 15    | RW    | Auxiliary Input Mute Control                                                                                                                                                                                                     |

|       |       | 0: Normal                                                                                                                                                                                                                        |

|       |       | 1: Mute                                                                                                                                                                                                                          |

| 14:13 | RO    | -Reserved-                                                                                                                                                                                                                       |

| 12:8  | RW    | Left Channel Gain Control These five bits select the gain applied to the left channel of the AUX input signal. The gain is programmable from -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable levels.   |

| 7:5   | RO    | -Reserved-                                                                                                                                                                                                                       |

| 4:0   | RW    | Right Channel Gain Control These five bits select the gain applied to the right channel of the AUX input signal. The gain is programmable from -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable levels. |

#### **PCM Output Volume Control**

Index: 18h Default Value: 8808h / 0808h

| Bit   | Attr. | Description                                                                                                                                                                                                                       |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | RW    | PCM Output Mute Control                                                                                                                                                                                                           |

|       |       | 0: Normal                                                                                                                                                                                                                         |

|       |       | 1: Mute                                                                                                                                                                                                                           |

| 14:13 | RO    | -Reserved-                                                                                                                                                                                                                        |

| 12:8  | RW    | Left Channel Gain Control                                                                                                                                                                                                         |

|       |       | These five bits select the gain applied to the left channel of the PCM output signal. The gain is programmable from -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable levels.                             |

| 7:5   | RO    | -Reserved-                                                                                                                                                                                                                        |

| 4:0   | RW    | Right Channel Gain Control These five bits select the gain applied to the right channel of the PCM output signal. The gain is programmable from -34.5dB to 12dB in 1.5dB increments, providing a total of 32 programmable levels. |

**Table 5. Stereo Output Attenuation**

|    | G4 | G3 | G2 | G1 | G0 | Level (dB) |

|----|----|----|----|----|----|------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 12.0       |

| 1  | 0  | 0  | 0  | 0  | 1  | 10.5       |

| 2  | 0  | 0  | 0  | 1  | 0  | 9.0        |

| 3  | 0  | 0  | 0  | 1  | 1  | 7.5        |

| 4  | 0  | 0  | 1  | 0  | 0  | 6.0        |

| 5  | 0  | 0  | 1  | 0  | 1  | 4.5        |

| 6  | 0  | 0  | 1  | 1  | 0  | 3.0        |

| 7  | 0  | 0  | 1  | 1  | 1  | 1.5        |

| 8  | 0  | 1  | 0  | 0  | 0  | 0.0        |

| 9  | 0  | 1  | 0  | 0  | 1  | -1.5       |

| 10 | 0  | 1  | 0  | 1  | 0  | -3.0       |

| 11 | 0  | 1  | 0  | 1  | 1  | -4.5       |

| 12 | 0  | 1  | 1  | 0  | 0  | -6.0       |

| 13 | 0  | 1  | 1  | 0  | 1  | -7.5       |

| 14 | 0  | 1  | 1  | 1  | 0  | -9.0       |

| 15 | 0  | 1  | 1  | 1  | 1  | -10.5      |

| 16 | 1  | 0  | 0  | 0  | 0  | -12.0      |

| 17 | 1  | 0  | 0  | 0  | 1  | -13.5      |

| 18 | 1  | 0  | 0  | 1  | 0  | -15.0      |

| 19 | 1  | 0  | 0  | 1  | 1  | -16.5      |

| 20 | 1  | 0  | 1  | 0  | 0  | -18.0      |

| 21 | 1  | 0  | 1  | 0  | 1  | -19.5      |

| 22 | 1  | 0  | 1  | 1  | 0  | -21.0      |

| 23 | 1  | 0  | 1  | 1  | 1  | -22.5      |

| 24 | 1  | 1  | 0  | 0  | 0  | -24.0      |

| 25 | 1  | 1  | 0  | 0  | 1  | -25.5      |

| 26 | 1  | 1  | 0  | 1  | 0  | -27.0      |

| 27 | 1  | 1  | 0  | 1  | 1  | -28.5      |

| 28 | 1  | 1  | 1  | 0  | 0  | -30.0      |

| 29 | 1  | 1  | 1  | 0  | 1  | -31.5      |

| 30 | 1  | 1  | 1  | 1  | 0  | -33.0      |

| 31 | 1  | 1  | 1  | 1  | 1  | -34.5      |

#### **Record Select Control**

Index: 1Ah Default Value: 0000h / 0404h

| Bit   | Attr. | Description |            |           |                                     |  |  |  |

|-------|-------|-------------|------------|-----------|-------------------------------------|--|--|--|

| 15:11 | RO    | -Reser      | -Reserved- |           |                                     |  |  |  |

| 10:8  | RW    | Recor       | d Source   | Select (  | Left Channel) (SL[2:0])             |  |  |  |

|       |       | These       | bits deter | rmine the | record source for the left channel. |  |  |  |

|       |       | SL2         | SL1        | SL0       | Left Record Source                  |  |  |  |

|       |       | 0           | 0          | 0         | MIC                                 |  |  |  |

|       |       | 0           | 0          | 1         | CD (L)                              |  |  |  |

|       |       | 0           | 1          | 0         | reserved                            |  |  |  |

|       |       | 0           | 1          | 1         | Aux In (L)                          |  |  |  |

|       |       | 1           | 0          | 0         | Line In (L)                         |  |  |  |

|       |       | 1           | 0          | 1         | Stereo Mix (L)                      |  |  |  |

|       |       | 1           | 1          | 0         | Mono Mix                            |  |  |  |

|       |       | 1           | 1          | 1         | Phone                               |  |  |  |

| 7:3   | RO    | -Reser      | ved-       |           |                                     |  |  |  |

| 2:0   | RW    | Recor       | d Source   | Select (  | Right Channel) SR[2:0]              |  |  |  |

|       |       | These       | bits deter | rmine the | record source for the right channel |  |  |  |

|       |       | SR2         | SR1        | SR0       | Right Record Source                 |  |  |  |

|       |       | 0           | 0          | 0         | MIC                                 |  |  |  |

|       |       | 0           | 0          | 1         | CD (R)                              |  |  |  |

|       |       | 0           | 1          | 0         | reserved                            |  |  |  |

|       |       | 0           | 1          | 1         | Aux In (R)                          |  |  |  |

|       |       | 1           | 0          | 0         | Line In (R)                         |  |  |  |

|       |       | 1           | 0          | 1         | Stereo Mix (R)                      |  |  |  |

|       |       | 1           | 1          | 0         | Mono Mix                            |  |  |  |

|       |       | 1           | 1          | 1         | Phone                               |  |  |  |

## **Record Gain Control**

Index: 1Ch Default Value: 8000h / 0000h

| Bit   | Attr. | Description                                                                                       |

|-------|-------|---------------------------------------------------------------------------------------------------|

| 15    | RO    | Record Mute Control                                                                               |

|       |       | 0: Normal                                                                                         |

|       |       | 1: Mute                                                                                           |

| 14:12 | RO    | -Reserved-                                                                                        |

| 11:8  | RW    | Record Gain Control (Left Channel)                                                                |

|       |       | These four bits select the gain applied to the LEFT channel recording source. The gain is         |

|       |       | programmable from 0dB to 22.5dB in 1.5dB increments, providing a total of 16 programmable levels. |

|       |       | The gain is set at 0dB when $GL[3:0] = 0h$ .                                                      |

| 7:4   | RO    | -Reserved-                                                                                        |

| 3:0   | RW    | Record Gain Control (Right Channel)                                                               |

|       |       | These four bits select the gain applied to the RIGHT channel recording source. The gain is        |

|       |       | programmable from 0dB to 22.5dB in 1.5dB increments, providing a total of 16 programmable levels. |

|       |       | The gain is set at 0dB when $GR[3:0] = 0h$ .                                                      |

## **General Purpose**

Index: 20h Default Value: 0000h / 0000h

| Bit   | Attr. | Description                                                                                                        |

|-------|-------|--------------------------------------------------------------------------------------------------------------------|

| 15:12 | RO    | -Reserved-                                                                                                         |

| 11:10 | RW    | Double Rate Slot Select (DRSS[1:0]) 00: PCM L, R n+1 data is on slots 10,11 01: PCM L, R n+1 data is on slots 7, 8 |

| 9     | RO    | -Reserved-                                                                                                         |

| 8     | RW    | MS (MIC Select)                                                                                                    |

| 7     | RW    | Loopback Mode  0: DAC/ADC Loopback disabled  1: DAC/ADC Loopback enabled                                           |

| 6:0   | RO    | -Reserved-                                                                                                         |

#### **Audio Interrupt and Paging Mechanism**

Index: 24h Default Value: 0001h / 0001h

| Bit   | Attr. | Description Description                                                                                       |

|-------|-------|---------------------------------------------------------------------------------------------------------------|

| 15    |       |                                                                                                               |

| 13    | RW    | Interrupt Status 0 Interrupt is cleared                                                                       |

|       |       | 1: Interrupt was generated                                                                                    |

|       |       | 1. Interrupt was generated                                                                                    |

|       |       | Interrupt event is cleared by writing a 1 to this bit. The interrupt bit will change regardless of condition  |

|       |       | of interrupt enable (I0) status. An interrupt in the GPI in slot 12 in the AC link will follow this bit       |

|       |       | change when interrupt enable (I0) is un-masked. If this bit is set, one or both of I3 or I2 must be set to    |

|       |       | indicate the interrupt cause.                                                                                 |

| 14:13 | RO    | Interrupt Cause                                                                                               |

|       | -     | I [2]= 0 - Reserved                                                                                           |

|       |       | I [3]= 0 - GPIO status change did not cause interrupt (default)                                               |

|       |       | 1: GPIO status change caused interrupt.                                                                       |

|       |       | These bits will indicate the cause(s) of an interrupt. This information should be used to service the         |

|       |       | correct interrupting event(s). If the Interrupt Status (bit I4) is set, one or both of these bits must be set |

|       |       | to indicate the interrupt cause. Hardware must reset these bits back to zero when the Interrupt Status        |

|       |       | bit is cleared.                                                                                               |

| 12    | RO    | -Reserved-                                                                                                    |

| 11    | RW    | Interrupt Enable                                                                                              |

|       |       | 0: Interrupt generation is masked                                                                             |

|       |       | 1: Interrupt generation is un-masked                                                                          |

|       |       |                                                                                                               |

|       |       | Software should not un-mask the interrupt unless ensured by the AC '97 controller that no conflict is         |

|       |       | possible with modem slot 12- GPI functionality. AC '97 2.2. Compliant controllers will not likely             |

| 10.4  | D.O.  | support audio codec interrupt infrastructure.                                                                 |

| 10:4  | RO    | -Reserved-                                                                                                    |

| 3:0   | RW    | Page Selector                                                                                                 |

|       |       | 0h: Vendor Specific 1h: Page ID 01(see correspondent definition register 60h-6Fh)                             |

|       |       | 2h-Fh – Reserved Pages                                                                                        |

|       |       | This register is used to select a descriptor of 16 word pages between registers 60h. to 6Fh. A value of       |

|       |       | Oh is used to select vendor specific space to maintain compatibility With AC '97 2.2 vendor specific          |

|       |       | registers.                                                                                                    |

|       |       | System software can determine implemented pages by writing the page number and reading the value              |

|       |       | back. If the value read back does not match the value written, the page is not implemented.                   |

|       |       | All implemented pages must be in consecutive. (i.e., page 2h cannot be implemented without page 1h)           |

#### **Power Down and Status**

Index: 26h Default Value: 0000h / 0000h

| Bit  | Attr. | Description                                                                                           |

|------|-------|-------------------------------------------------------------------------------------------------------|

| 15   | RW    | Enable Amplifier Power Down                                                                           |

|      |       | The signal polarity at pin 47, EAPD is identical to bit description                                   |

|      |       | 0: External Power Amplifier active                                                                    |

|      |       | 1: Powerdown External Power Amplifier                                                                 |

| 14   | RW    | -Reserved-                                                                                            |

| 13:8 | RO    | Power Down Mode Bits PR[5:0]                                                                          |

|      |       | These read/write bits are used to control the power down states of the VT1613. Each power down        |

|      |       | function bit is enabled by setting the respective bit high. When either PR2 or PR3 is 1, the analog   |

|      |       | mixer circuit is powered down. Particularly, PR5 has no effect unless PR0, PR1 and PR4 are all set to |

|      |       | "1". This implies that the codec can be woken up by a warm reset, because warm reset clears PR4,      |

|      |       | which in turn disables the function of PR5. The register bit, however will not be cleared by a warm   |

|      |       | reset. The power down modes controlled by each bit is described in the table below.                   |

|      |       | Bit Function                                                                                          |

|      |       | PRO ADC and Mux Powerdown                                                                             |

|      |       | PR1 DAC Powerdown                                                                                     |

|      |       | PR2 Mixer Powerdown (VREF on)                                                                         |

|      |       | PR3 Mixer Powerdown (VREF off)                                                                        |

|      |       | PR4 AC-Link Powerdown (BIT_CLK off) PR5 Internal Clock Disabled                                       |

| 7.1  | DO    | PR5 Internal Clock Disabled -Reserved-                                                                |

| 7:4  | RO    | 10001100                                                                                              |

| 3    | RO    | 1: Vref at normal level                                                                               |

| 2    | RO    | 1: Analog circuit (mixer, volume controletc) ready                                                    |

| 1    | RO    | 1: DAC ready to accept data                                                                           |

| 0    | RO    | 1: ADC ready to transmit data                                                                         |

Note: Bit[3:0] are status bits. These bits are used to monitor the readiness of some sections of the VT1613. Reading a "1" from any of these bits would be an indication of "ready" status.

**Table 6. Power Down Control Mapping Table**

|       | ADC | DAC | Mixer | Vref | AC-  | Internal | EAPD | HP    | HP    |

|-------|-----|-----|-------|------|------|----------|------|-------|-------|

|       |     |     |       |      | Link | Clock    |      | Amp 1 | Amp 1 |

| PR0   | PD  |     |       |      |      |          |      |       |       |

| PR1   |     | PD  |       |      |      |          |      |       |       |

| PR2   |     |     | PD    |      |      |          |      | PD    | PD    |

| PR3   | PD  | PD  | PD    | PD   |      |          |      | PD    | PD    |

| PR4   | PD  | PD  |       |      | PD   |          |      |       |       |

| PR5   | PD  | PD  |       |      | PD   | PD       |      |       |       |

| PR7   |     |     |       |      |      |          | High |       |       |

| 5C[7] |     |     |       |      |      |          |      |       | PD    |

| 5C[5] |     |     |       |      |      |          |      | PD    |       |

#### **Extended Audio ID**

Index: 28h Default Value: 097Ch

| Bit   | Attr. | Description                                                                 |

|-------|-------|-----------------------------------------------------------------------------|

| 15:12 | RO    | -Reserved-                                                                  |

| 11:10 | RO    | AC'97 Revision ID                                                           |

|       |       | REV[1:0]=10 indicates Codec is AC '97 revision 2.3 compliant.               |

| 9:3   | RO    | -Reserved-                                                                  |

| 2     | RO    | Sony/Philips Digital Audio Interface                                        |

|       |       | 1: Feature implemented in compliance to "S/PDIF Output for AC '97, Rev 1.0" |

| 1     | RO    | Double Rate PCM Audio                                                       |

|       |       | 1: Feature implemented in compliance to AC '97 2.2 Appendix A               |

| 0     | RO    | Variable Sampling Rate PCM Audio                                            |

|       |       | 1: Feature implemented in compliance to AC '97 2.2 Appendix A               |

#### **Extended Audio Status/Control**

Index: 2Ah Default Value: 3830h

|       | _     | Detautt value, 303011                                                                                   |

|-------|-------|---------------------------------------------------------------------------------------------------------|

| Bit   | Attr. | Description                                                                                             |

| 15    | RW    | S/PDIF Valid Configuration (VCFG)                                                                       |

|       |       | Determines S/PDIF transmitter behavior when data is not being transmitted. When asserted, this bit      |

|       |       | forces the de-assertion of the S/PDIF "Validity" flag, which is bit 28 transmitted in each S/PDIF sub-  |

|       |       | frame.                                                                                                  |

| 14:11 | RO    | -Reserved-                                                                                              |

| 10    | RO    | S/PDIF Configuration Valid                                                                              |

|       |       | 0: S/PDIF configuration (SPSA, SSR, DAC rate, DRS) invalid (not supported)                              |

|       |       | 1: S/PDIF configuration (SPSA, SSR, DAC rate, DRS) valid (supported)                                    |

| 9:6   | RO    | -Reserved-                                                                                              |

| 5:4   | RW    | S/PDIF Slot Assignment                                                                                  |

|       |       | These bits determine the S/PDIF data source from AC-link slot selection. The default state reflects the |

|       |       | pervasive design feature of common AC'97 digital controllers supporting slots 3 & 4.                    |

|       |       | 00: AC-link slots 3 & 4 (front stereo pair)                                                             |

|       |       | 01: AC-link slots 7 & 8 (surround pair)                                                                 |

|       |       | 10: AC-link slots 6 & 9 (LFE & Center pair)                                                             |

|       |       | 11: AC-link slots 10 &11 (default):                                                                     |

| 3     | RO    | -Reserved-                                                                                              |

| 2     | RW    | Sony/Philips Digital Audio Interface                                                                    |

|       |       | 0: The S/PDIF transmitter is off by default                                                             |

|       |       | 1: Set this bit to turn on the S/PDIF transmitter.                                                      |

| 1     | RW    | Double Rate Mode Control                                                                                |

|       |       | 0: Disable                                                                                              |

|       |       | 1: Enable Double-Rate Audio mode in which data from PCM L and PCM R in output slots 3 and 4 is          |

|       |       | used in conjunction with PCM L (n+1) and PCM R (n+1) data, to provide DAC streams at twice the          |

|       |       | sample rate designated by the PCM Front Sample Rate Control Register.                                   |

| 0     | RW    | Variable Sampling Rate Mode control                                                                     |

|       |       | 0: Fixed 48 KHz sampling rate                                                                           |

|       |       | 1: Enable VSR                                                                                           |

Table 7. SPDIF Validity and Configuration Mapping Table

| V<br>Index 3A[15] | VCFG<br>Index 2A[15] | S/PDIF Channel Status Bit 28                                                           | S/PDIF Data Bit                                                       |

|-------------------|----------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 0                 | 0                    | 0: if valid data is available to transfer 1: if no valid data is available to transfer | Valid data, or repeat the previous data if no valid data is available |

| 0                 | 1                    | 0                                                                                      | Valid data, or 24'b0 if no valid data available                       |

| 1                 | 0                    | 1                                                                                      | Repeat the previous data                                              |

| 1                 | 1                    | 1                                                                                      | 24'b0                                                                 |

#### PCM Front, Surround and Center DAC Sample Rate

Index: 2Ch Default Value: BB80h / BB80h (fixed)

| Bit  | Attr. | Description                                                                                            |

|------|-------|--------------------------------------------------------------------------------------------------------|

| 15:0 | RW    | Main stereo + Center or all DAC Sample Rate (in Hz)                                                    |

|      |       | 16-bit unsigned value representing the sample rate. The default value is 48 KHz (48000 = BB80h).       |

|      |       | This register controls all eight DAC output rate providing a sample accurate synchronization among the |

|      |       | channels. Registers 2Eh and 30h are read only and always reflect the setting in register 2Ch when read |

|      |       | back. The value is reset to BB80h if VRA bit in register 2A is cleared to 0.                           |

#### **PCM ADC Sample Rate**

Index: 32h Default Value: BB80h / BB80h (fixed)

| Bit  | Attr. | Description                                                                                      |

|------|-------|--------------------------------------------------------------------------------------------------|

| 15:0 | RW    | ADC Sample Rate (in Hz)                                                                          |

|      |       | 16-bit unsigned value representing the sample rate. The default value is 48 KHz (48000 = BB80h). |

|      |       | The value is reset to BB80h if VRA bit in register 2A is cleared to 0.                           |

| Valid Sampling Rate | Value in Registers |

|---------------------|--------------------|

| 48K                 | BB80h              |

| 44.1K               | AC44h              |

| 32K                 | 7D00h              |

| 24K                 | 5DC0h              |

| 22.05K              | 5622h              |

| 16K                 | 3E80h              |

| 12K                 | 2EE0h              |

| 11.025K             | 2B11h              |

| 8K                  | 1F40h              |

Note: When a sampling rate value programmed is not supported, the hardware will choose a rate that's close to the desired rate. The driver should always read back the register content to see if the programmed rate is supported.

Also, in I2S mode, the sampling rates are fixed at 48K (BB80h).

#### **S/PDIF Control**

Index: 3Ah Default Value: 2000h / 2000h

This read / write register controls the S/PDIF functionality. The register manages the bit fields propagated as channel status (or subframe in the V case). With the exception of V, this register should only be written when the S/PDIF transmitter is disabled (SPDIF bit at 2Ah\_2 is "0"). This ensures that control and status information start up correctly at the beginning of S/PDIF transmission.

| Bit   | Attr. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | RW    | Validity (V) This bit affects the "Validity flag", bit[28] transmitted in each subframe, and enables the S/PDIF transmitter to maintain connection during error or mute conditions. The behavior of the S/PDIF transmitter with respect to this bit depends on the value of the VCFG bit in the Extended Audio Status and Control register. The behavior of the transmitter is defined in the definition of the Extended Audio Status and Control Register (Index 2Ah) |

| 14    | RW    | <b>Double Rate S/PDIF</b> When DRS is enabled "1" and SPSA is configured {"01", "10", or "11"} the S/PDIF transmitter uses AC-link slots 3&4 + {7&8, 6&9, or 10&11} to supply data at Fs = 96 kHz.  Note: Double rate S/PDIF should only be enabled if register 6E[15:12] = 3'b0011, that is, the front L/R jack is plugged into pin 35/36.                                                                                                                            |

| 13:12 | RW    | S/PDIF Sample Rate 00: 44.1KHz 01: 10: 48KHz (default) 11 32KHz                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11    | RW    | Generation Level Programmed according to IEC standards.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10:4  | RW    | Category Code Programmed according to IEC standards.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3     | RW    | Preemphasis  0: Default is no Preemphasis.  1: Indicates filter preemphasis is 50/15μs.                                                                                                                                                                                                                                                                                                                                                                                |

| 2     | RW    | Copyright  0: Copyright is not asserted (default).  1: Indicates copyright is asserted.                                                                                                                                                                                                                                                                                                                                                                                |

| 1     | RW    | Non-Audio Samples  0: Indicates samples are linear PCM suitable for direct conversion to audio playback  1: Set this bit for transmitting non-PCM audio samples such as AC-3.                                                                                                                                                                                                                                                                                          |

| 0     | RW    | Professional  0: Indicates Consumer mode (default).  1: Set Professional mode. Set this bit in conjunction with /PCM bit (above) for AC-3.                                                                                                                                                                                                                                                                                                                             |

# Vendor Reserved

Index: 5Ah Default Value: 0000h / 0000h

| Index: 5A | h     | Default Value: 0000h / 0000h                                                                             |

|-----------|-------|----------------------------------------------------------------------------------------------------------|

| Bit       | Attr. | Description                                                                                              |

| 15        | RW    | In AC'97 mode, this bit is fixed at 0.                                                                   |

|           |       | In I2S mode, this bit is readable / writable.                                                            |

|           |       | 0: I2S data format                                                                                       |

|           |       | 1: Left Justified data format                                                                            |

| 14        | RW    | ADC ROM Test Mode                                                                                        |

|           |       | 0: Normal                                                                                                |

|           |       | 1: Enable ADC ROM test mode                                                                              |