# biomation

# MODEL 8100 WAVEFORM RECORDER

OPERATING AND SERVICE MANUAL

# biomation

# MODEL 8100 WAVEFORM RECORDER

OPERATING AND SERVICE MANUAL

# biomation

# MODEL 8100 WAVEFORM RECORDER

OPERATING AND SERVICE MANUAL

# OPERATING & SERVICE MANUAL

# MODEL 8100

# Table of Contents

| Section |                          | Page         |

|---------|--------------------------|--------------|

| I       | General Information      | 1            |

|         | 1.1 Certification        | 1            |

|         | 1.2 Warranty             | 1            |

|         | 1.3 Instrument Descript  | ion 1        |

|         | 1.4 Specifications       | 2            |

|         |                          |              |

| II      | <u>Installation</u>      | 4            |

|         | 2.1 Introduction         | 4            |

|         | 2.2 Unpacking and Inspe  | ection 4     |

|         | 2.3 Storage and Shipmen  | it 4         |

|         | 2.4 Power Connection     | 4            |

|         | 2.5 Preparation for Use  | 5            |

|         | 2.6 Initial Warm-up      | 5            |

|         |                          |              |

| III     | Principles of Operation  | 6            |

|         | 3.1 Introduction         | 6            |

|         | 3.2 Basic Functional De  | scription 7  |

|         | 3.3 Operational Function | ons 8        |

|         | 3.4 Data Acquisition Li  | mitations 13 |

| Section |       | ]                                                 | Page |

|---------|-------|---------------------------------------------------|------|

| IV      | Opera | ation                                             | 14   |

|         | 4.1   | Introduction                                      | 14   |

|         | 4.2   | Front Panel Controls and Connectors               | 14   |

|         | 4.3   | Rear Panel Controls and Connectors                | 23   |

|         | 4.4   | Set Up Procedure                                  | 27   |

|         | 4.5   | Operating Procedures                              | 30   |

|         |       |                                                   |      |

| V       | Digi  | tal Control Interface                             | 34   |

|         | 5.1   | Introduction                                      | 34   |

|         | 5.2   | Connector Definitions                             | 35   |

|         | 5.3   | Signal Specifications                             | 36   |

|         | 5.4   | Data Output Only Operation                        | 44   |

|         | 5.5   | Full Digital Control Operation                    | 46   |

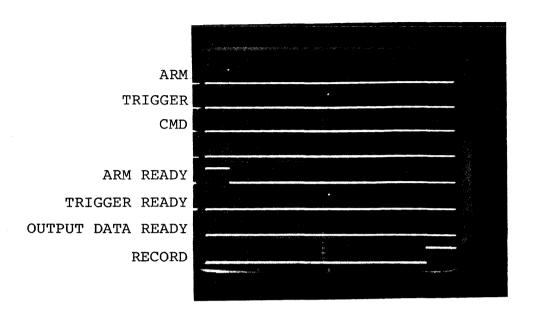

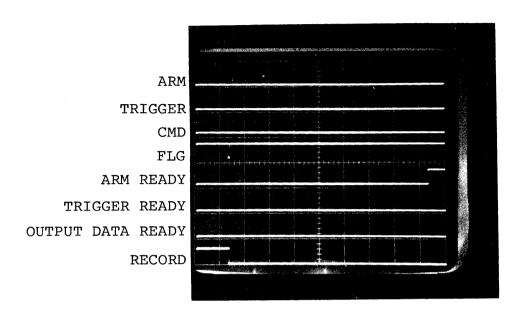

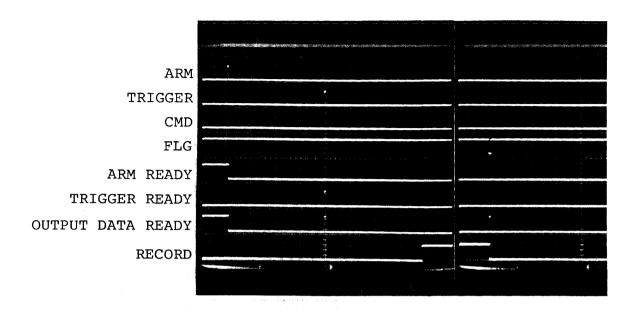

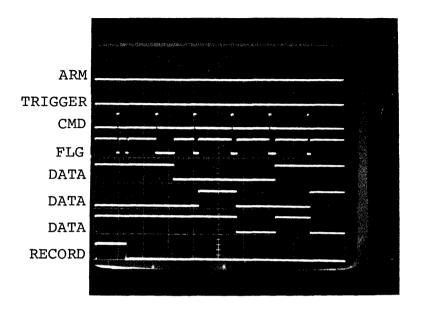

|         | 5.6   | Interface Timing Diagrams                         | 62   |

|         | 5.7   | Fast Turn Around Program                          | 63   |

|         |       |                                                   |      |

| VI      | Calil | oration Procedures                                | 64   |

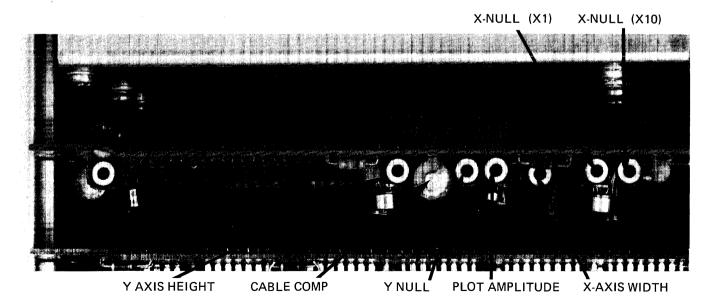

| •       | 6.1   | Calibration of Display Output                     | 64   |

|         | 6.2   | Recalibration of the Internal Circuits            | 65   |

|         | 6.3   | Required Test Equipment and Test Aids             | 65   |

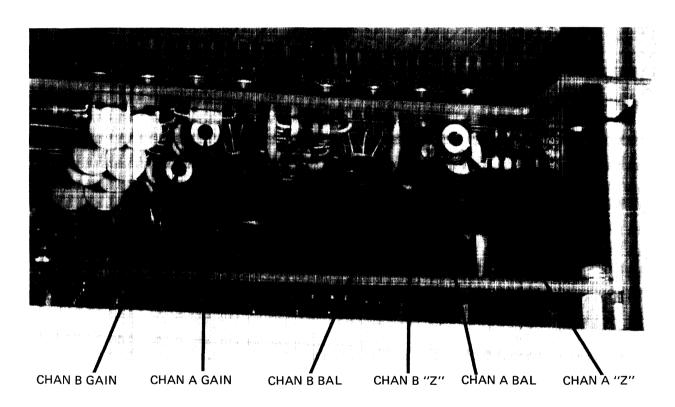

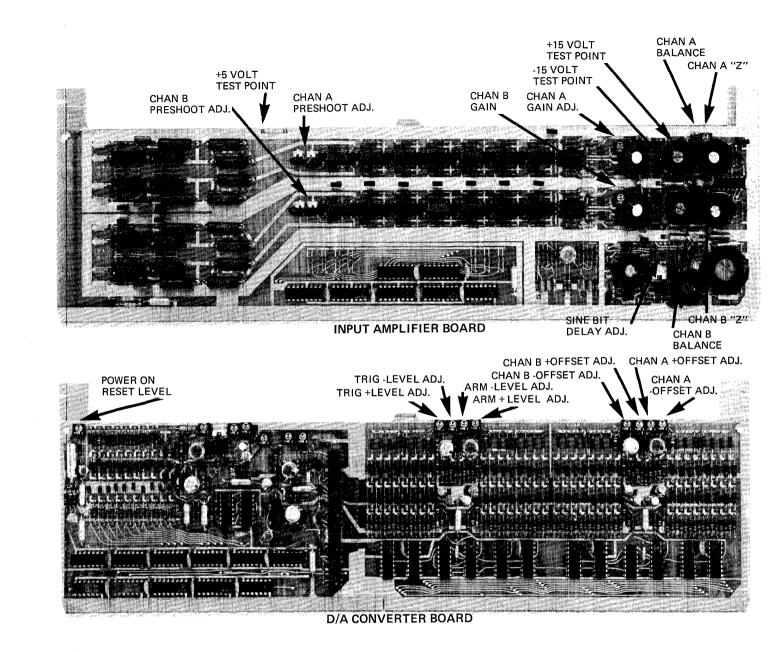

|         | 6.4   | Input Amplifier Gain Adjustment                   | 66   |

|         | 6.5   | Input Amplifier Gain Adjustment                   | 67   |

|         | 6.6   | (Supplemental) Offset Level Calibration (Digital) | 70   |

|         | 6.7   | Arm and Trigger Level Calibration                 | 70   |

|         | 6.8   | Internal Arm/Trigger Level                        | 73   |

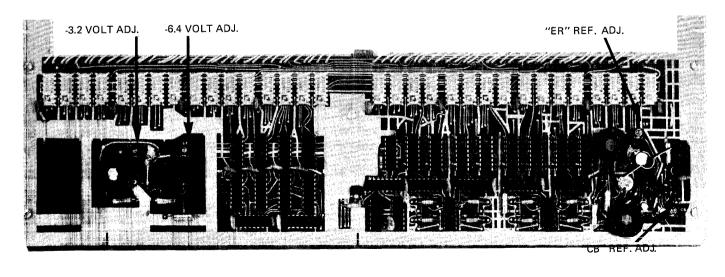

|         | 6.9   | Crossover Adjustment                              | 77   |

|         | 6.10  | Analog-to-Digital Converter Alignment             | 79   |

| Section |                                                                          | Page |  |

|---------|--------------------------------------------------------------------------|------|--|

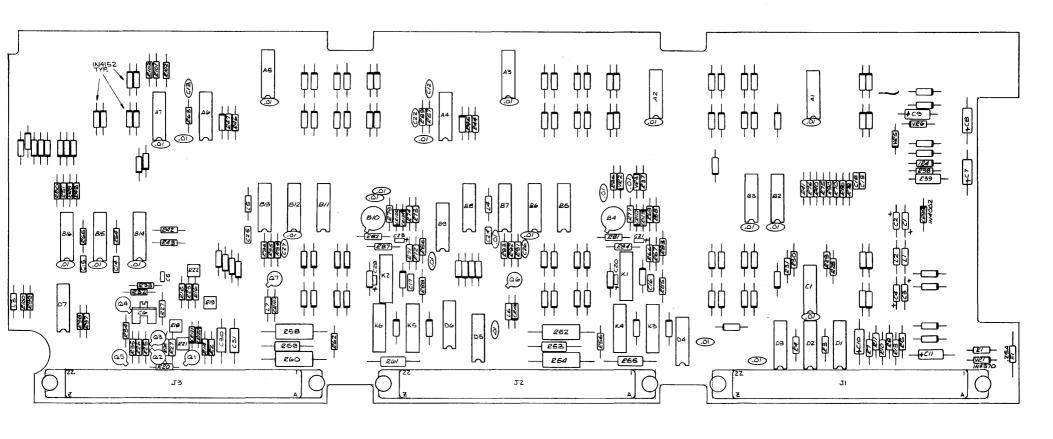

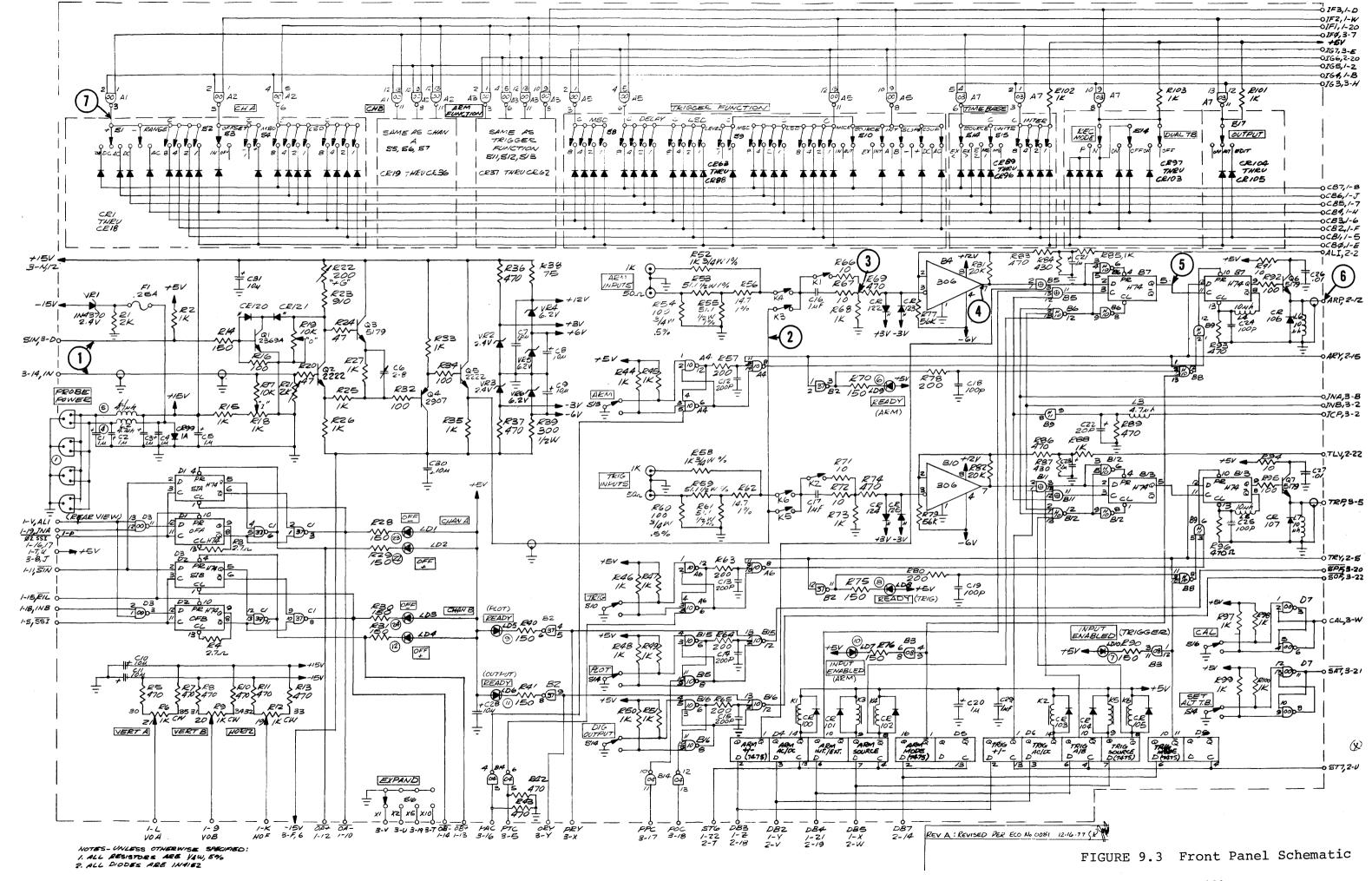

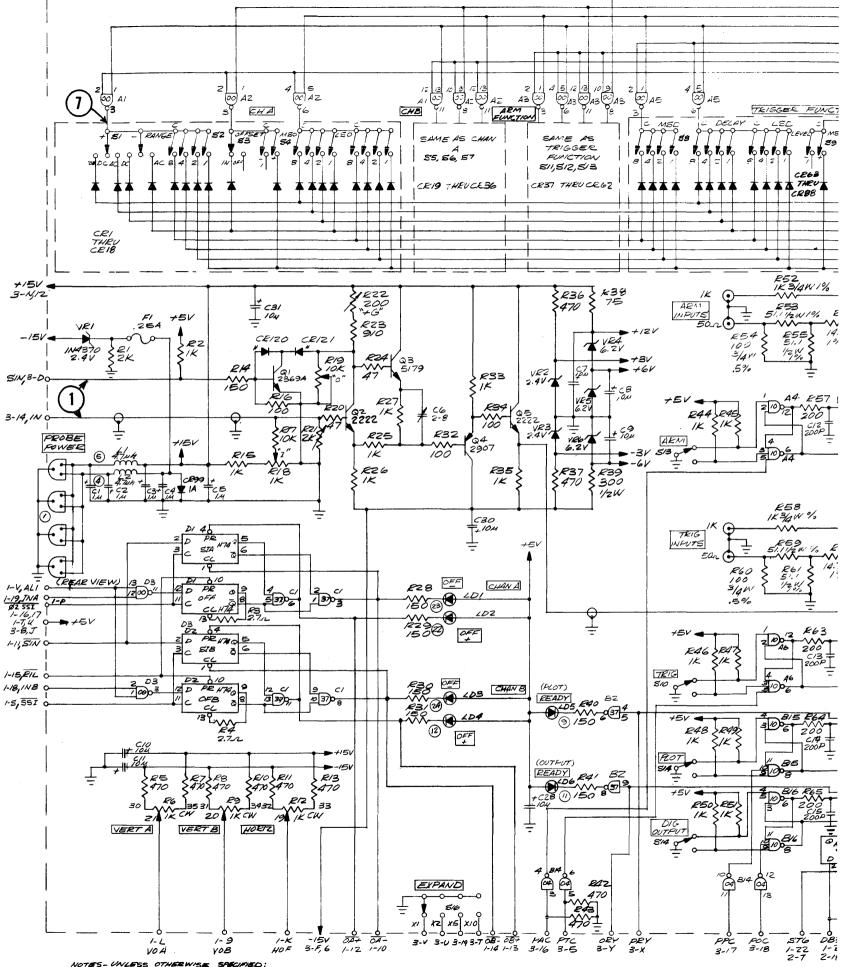

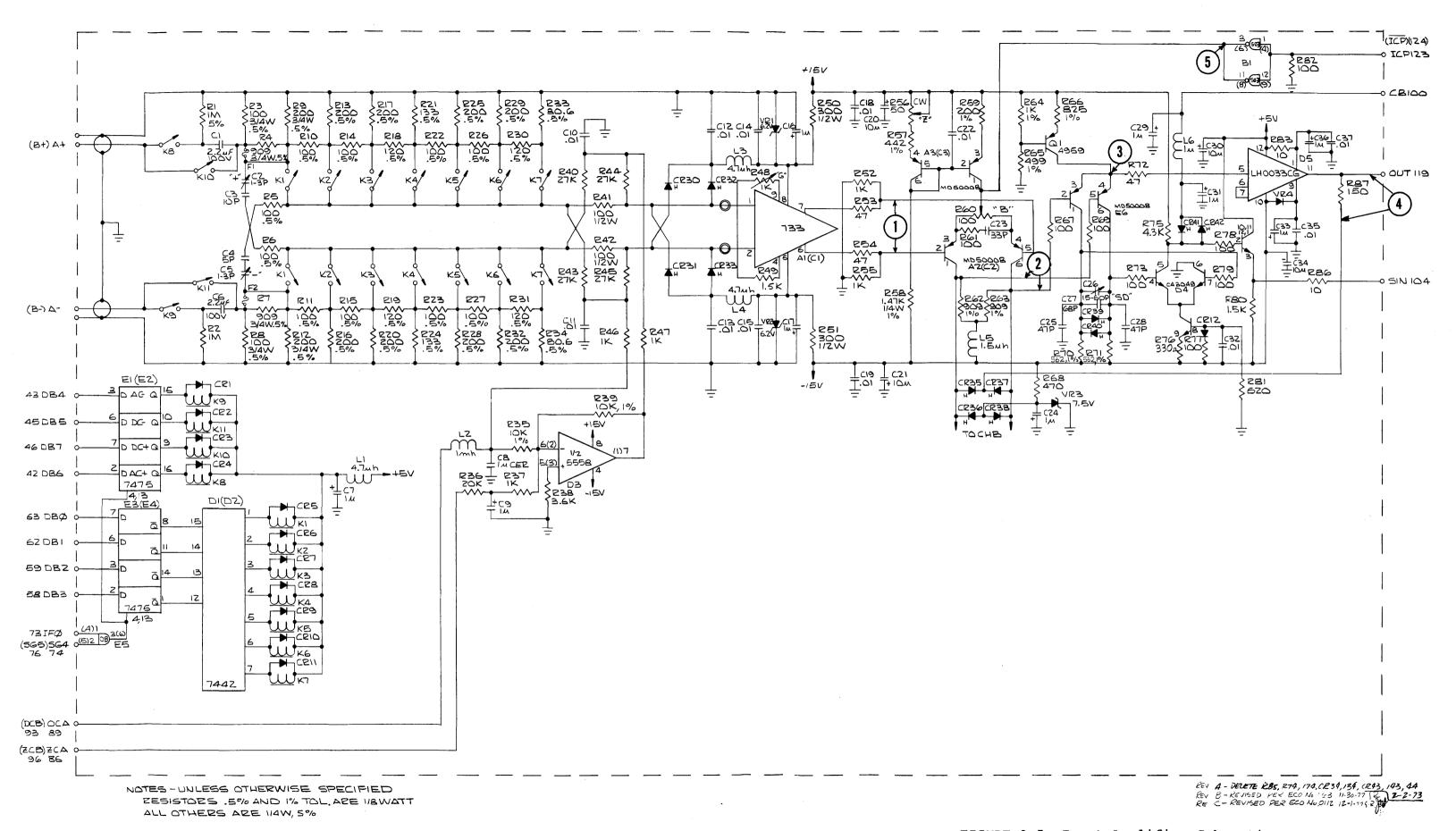

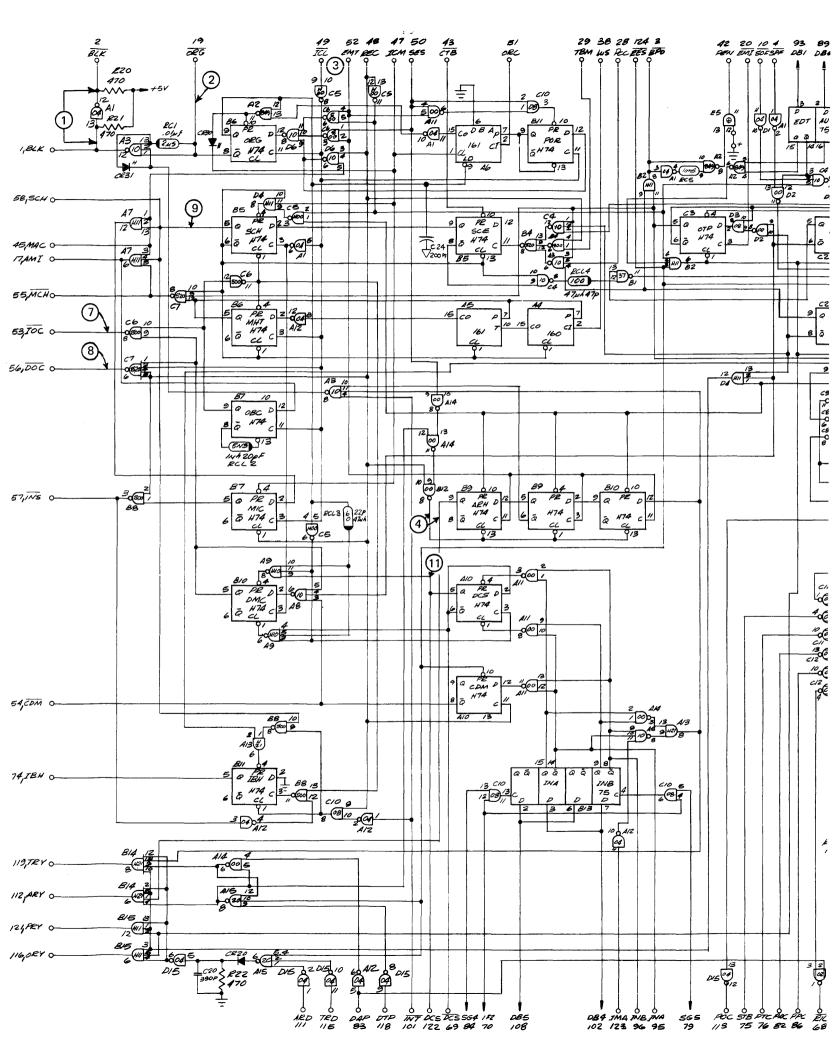

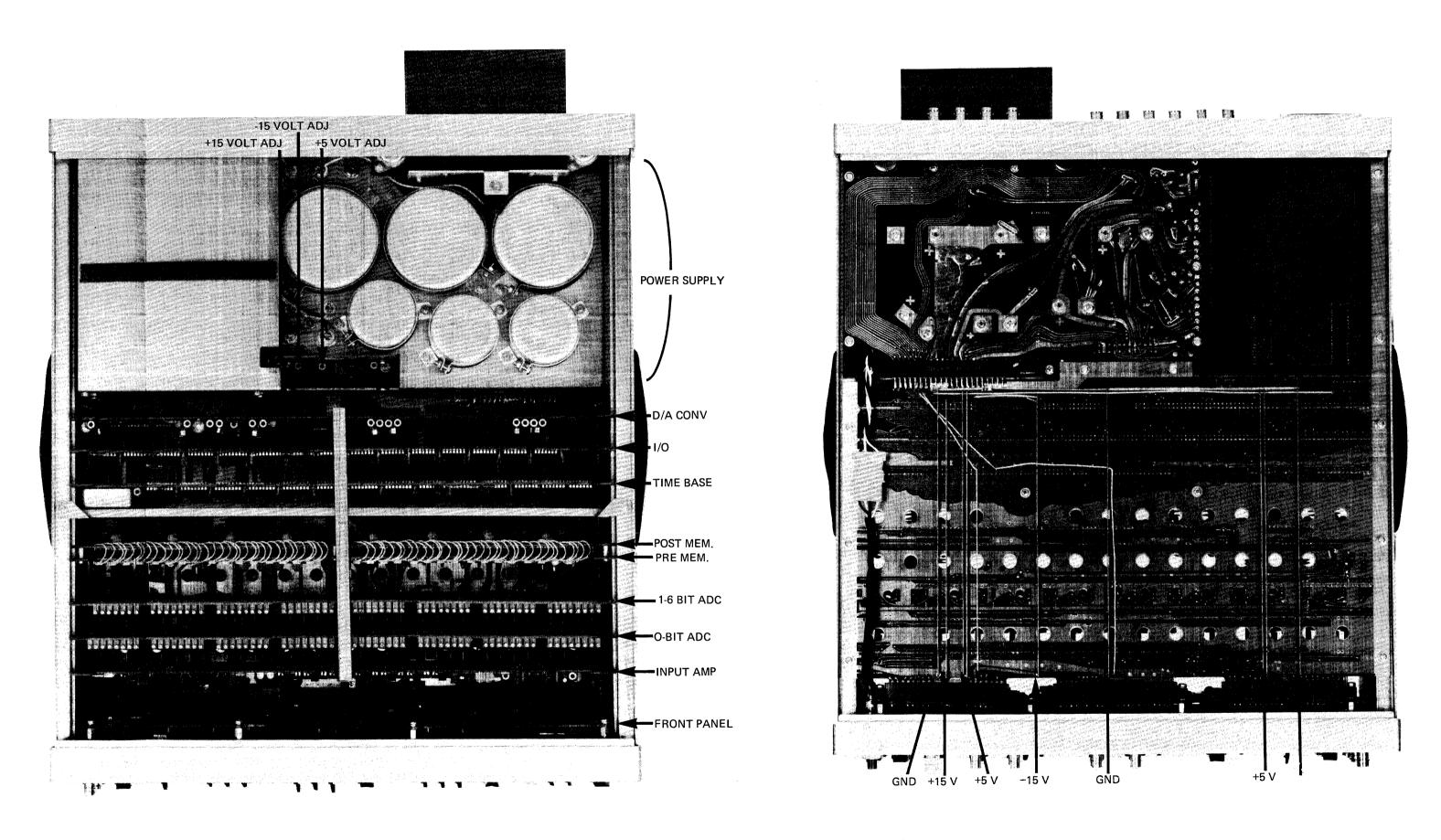

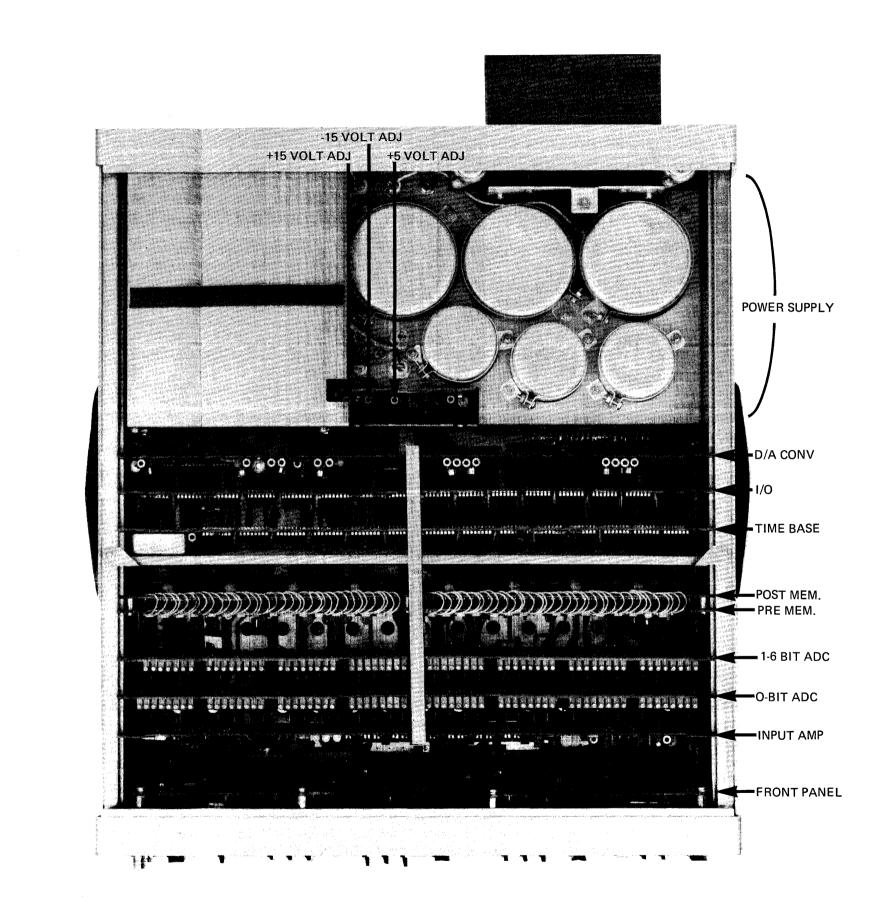

| VII     | Technical Description                                                    | 80   |  |

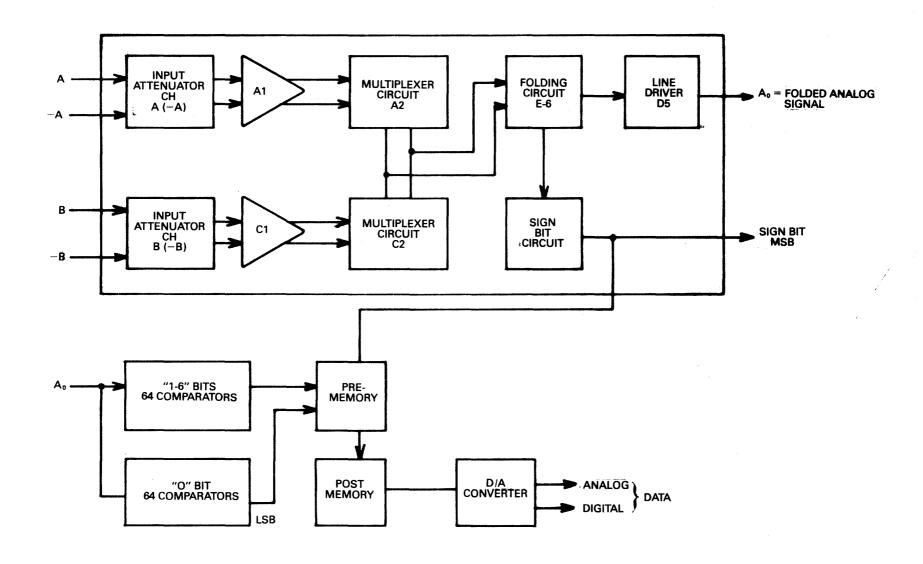

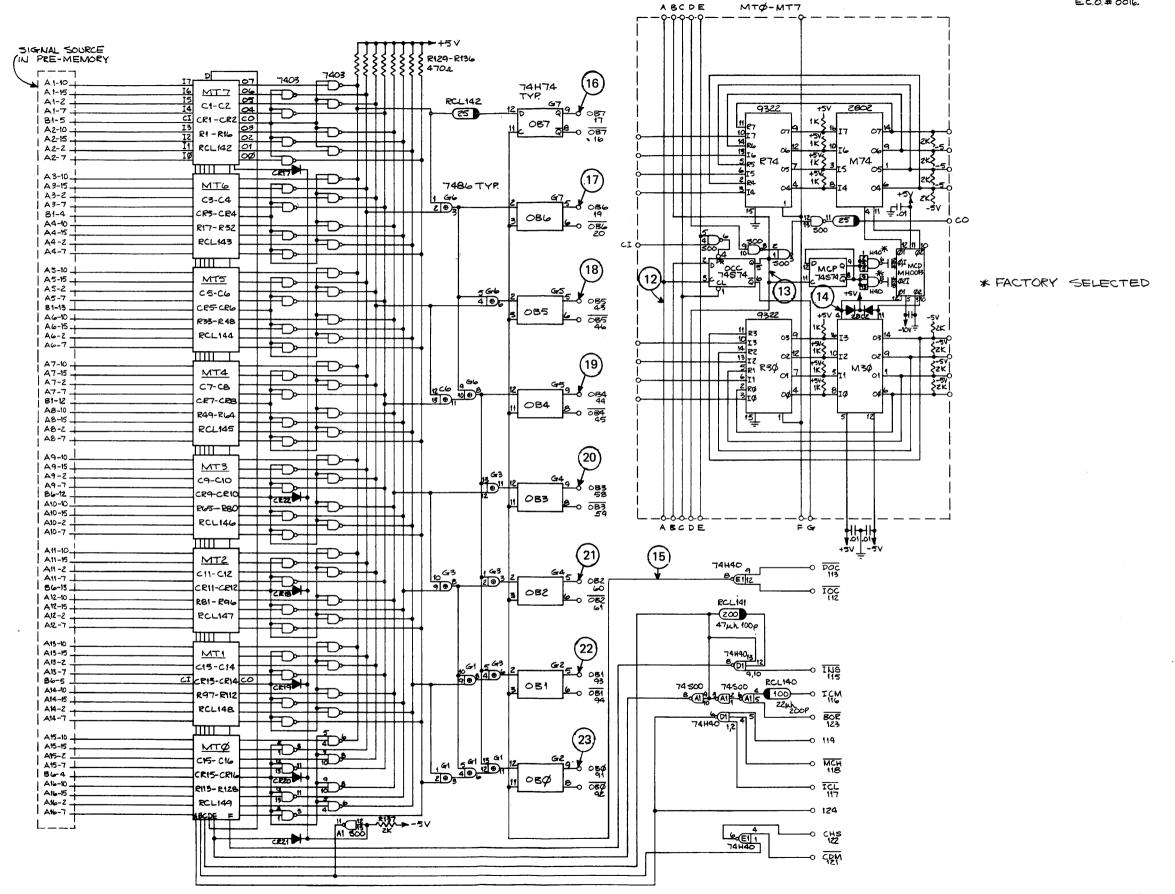

|         | 7.1 General Functional Description                                       | 80   |  |

|         | 7.2 Data Flow                                                            | 80   |  |

|         | 7.3 Internal/External Program Functions                                  | 82   |  |

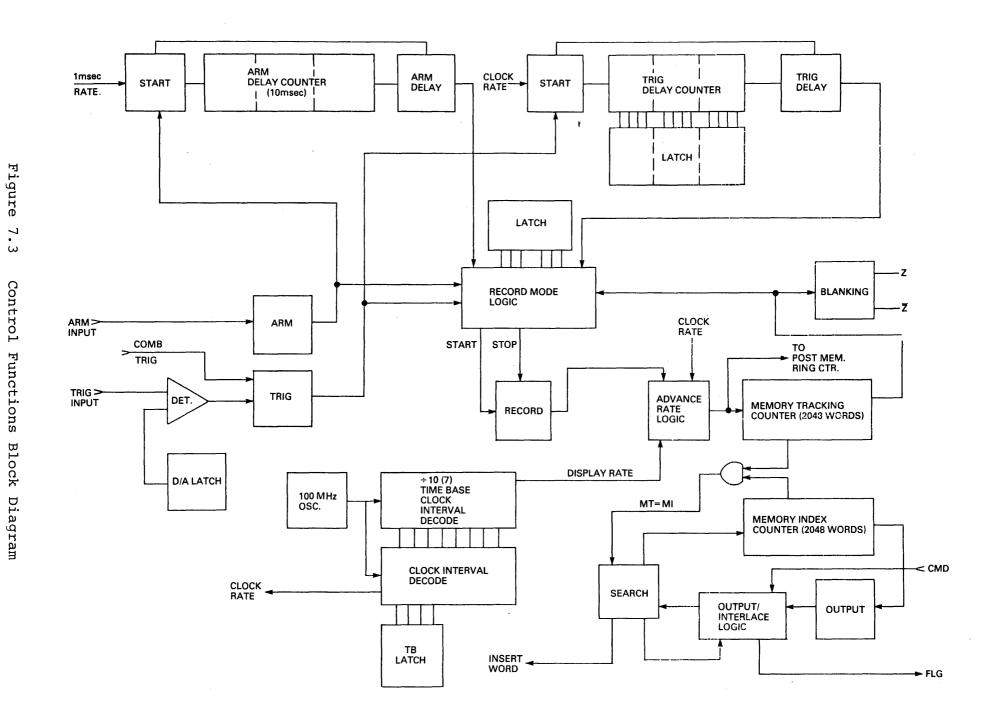

|         | 7.4 Control Functions                                                    | 82   |  |

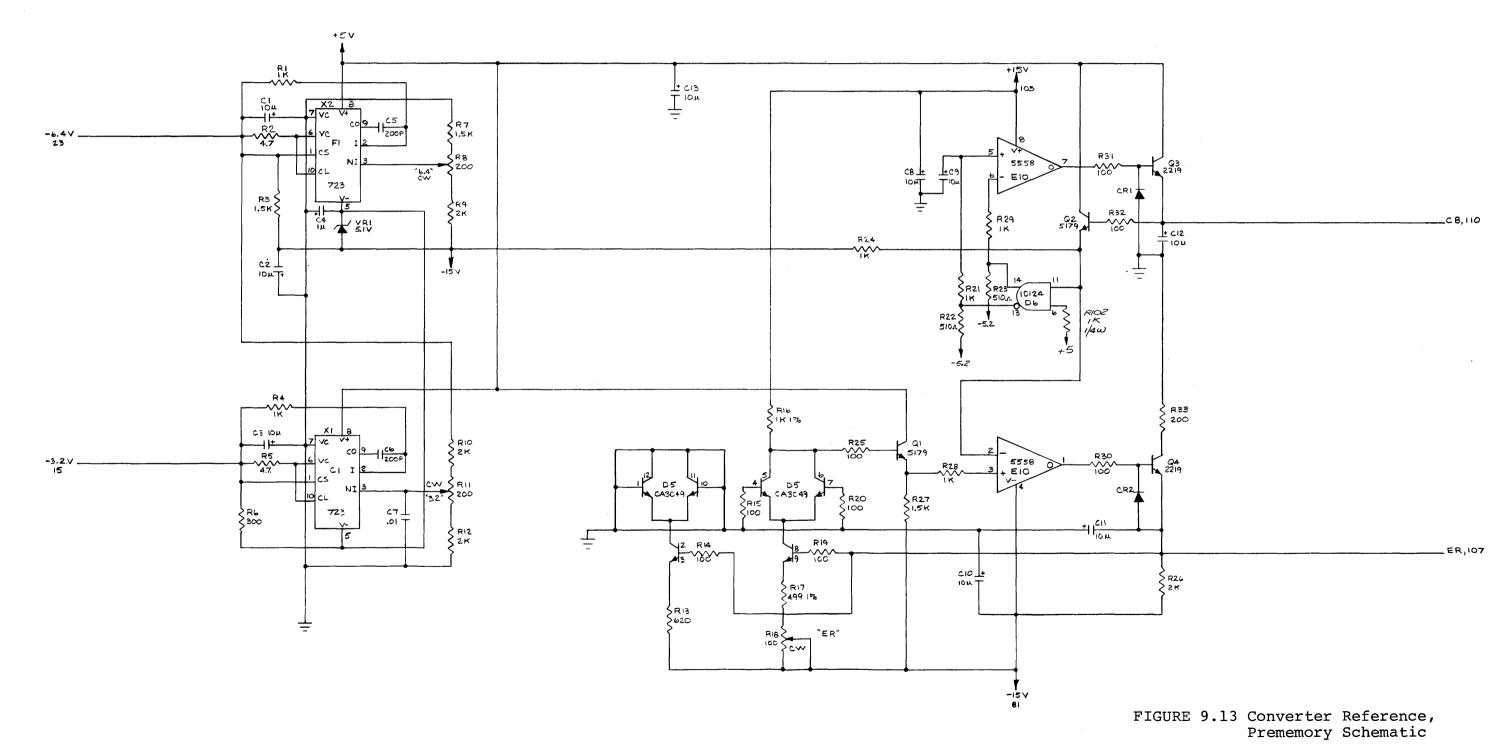

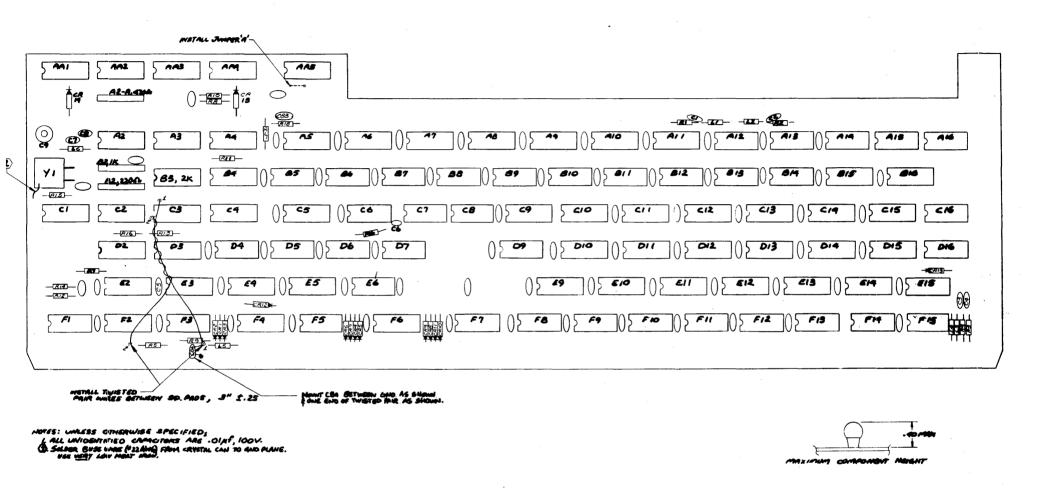

|         | 7.5 Circuit Description                                                  | 87   |  |

|         |                                                                          |      |  |

| VIII    | Maintenance                                                              | 107  |  |

|         | 8.1 Diagnostic Procedure                                                 | 107  |  |

|         | 8.2 External Program Diagnostic Procedure                                | 127  |  |

|         |                                                                          |      |  |

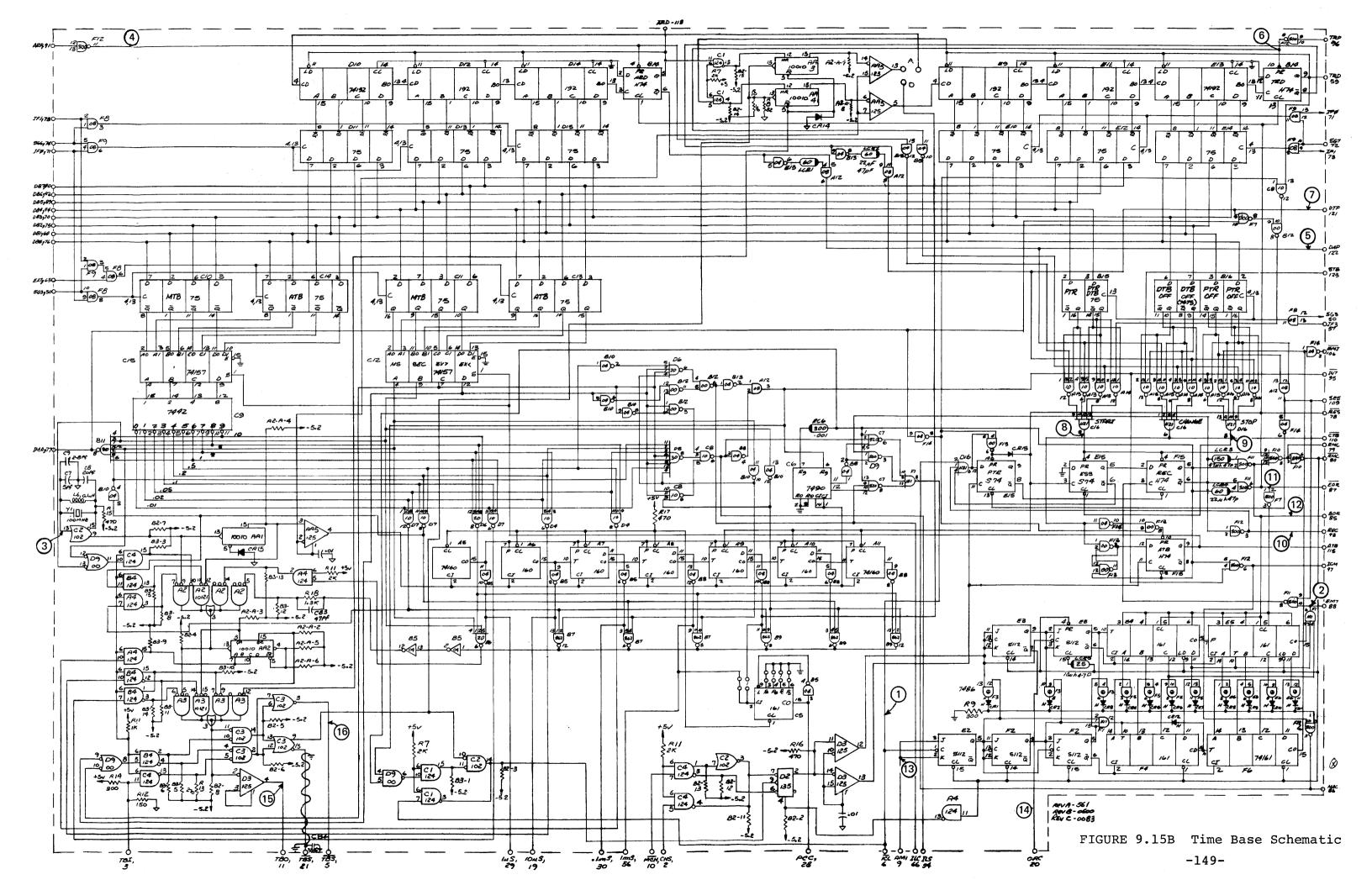

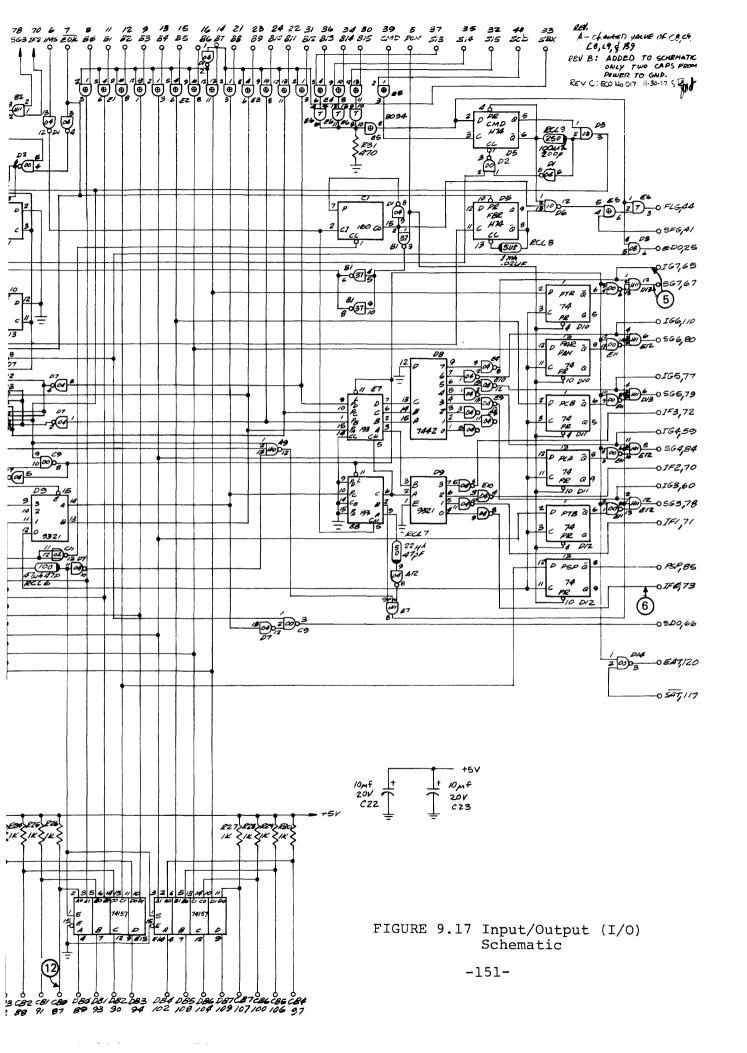

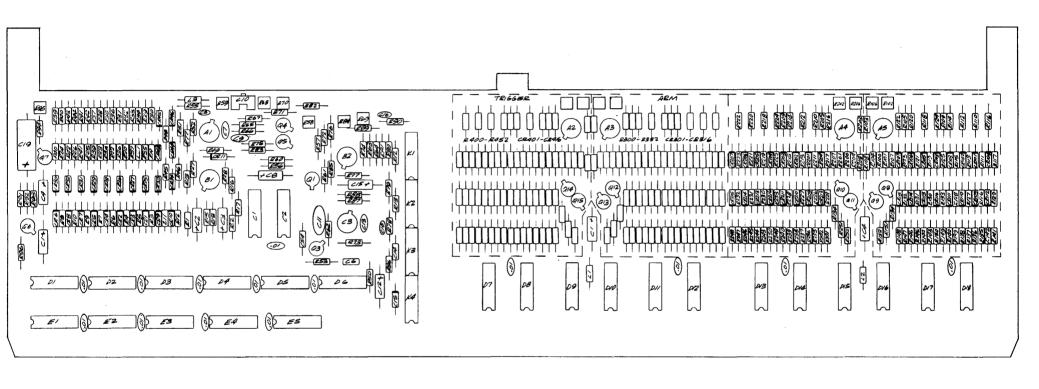

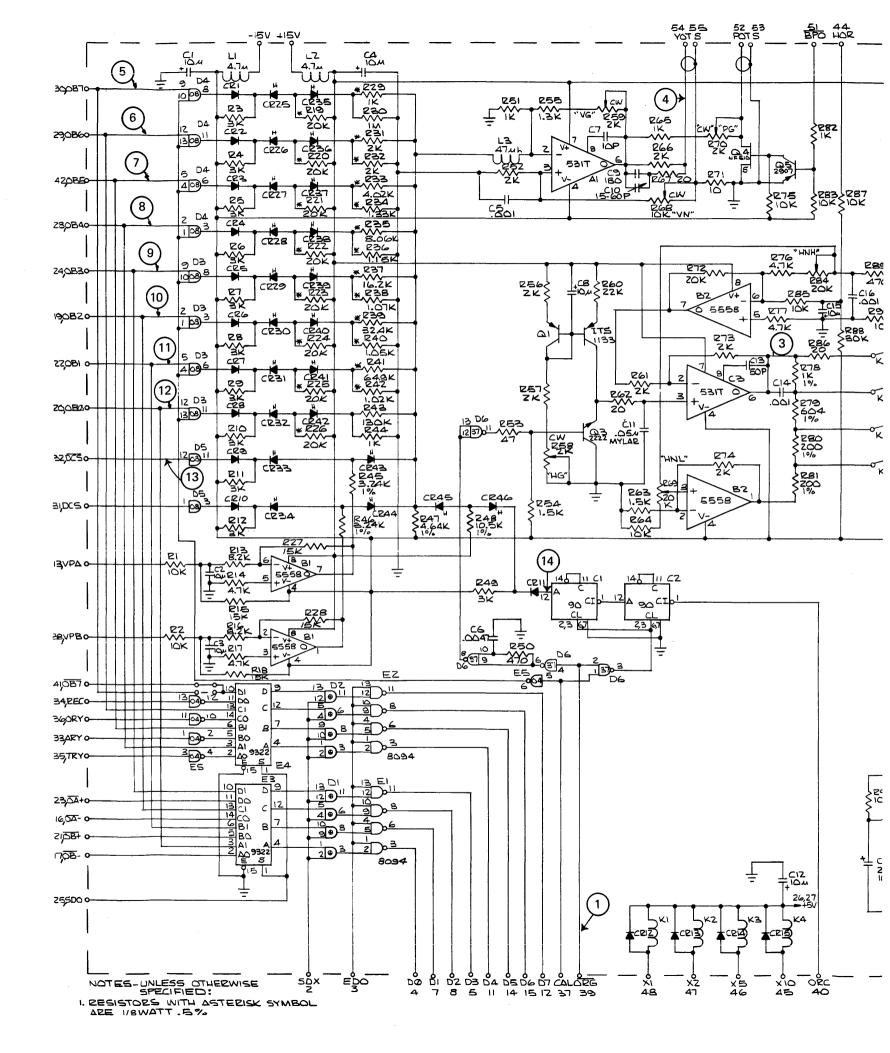

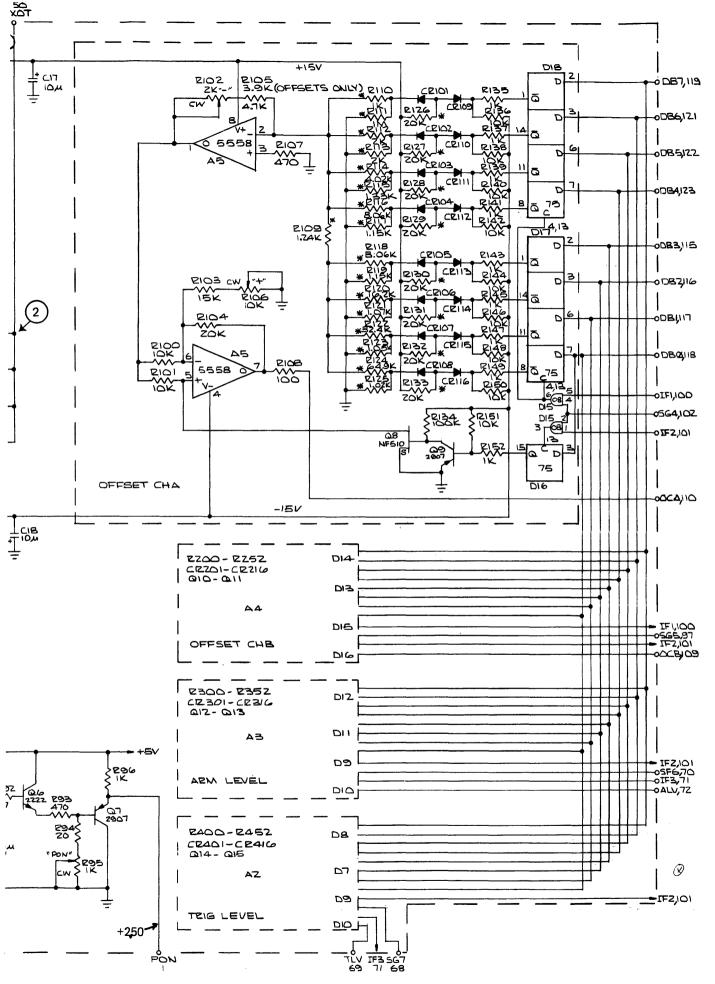

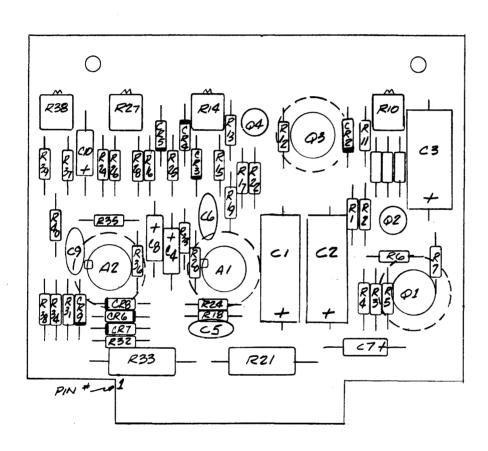

| IX      | Schematics, Mechanical Drawings and Maintenance Diagnostic Illustrations | 130  |  |

#### SECTION I

#### GENERAL INFORMATION

# 1.1 Certification

Gould Inc. certifies that this instrument was thoroughly tested and inspected and found to meet its published specifications when it was shipped from the factory.

# 1.2 Warranty

All Gould Inc. products are warranted against defects in materials and workmanship. This warranty applies for one year from the date of delivery, or, in the case of certain major components listed in the operating manual, for the specified period. We will repair or replace products that prove to be defective during the warranty period. If a unit fails within thirty days of delivery, Gould Inc. will pay all shipping charges relating to the repair of the unit. Units under warranty, but beyond the thirty day period, should be sent to Gould Inc. prepaid and Gould Inc. will return the unit prepaid. Units out of the one year warranty period, the customer will pay all freight charges. IN THE EVENT OF A BREACH OF GOULD INC.'S WARRANTY GOULD INC. SHALL HAVE THE RIGHT IN ITS DISCRETION EITHER TO REPLACE OR REPAIR THE DEFECTIVE GOODS OR TO REFUND THE PORTION OF THE PUR-CHASE PRICE APPLICABLE THERETO. THERE SHALL BE NO OTHER REMEDY FOR BREACH OF THE WARRANTY. IN NO EVENT SHALL GOULD INC. BE LIA-BLE FOR THE COST OF PROCESSING, LOST PROFITS, INJURY TO GOODWILL, OR ANY SPECIAL OR CONSEQUENTIAL DAMAGES. THE FOREGOING WARRANTY IS EXCLUSIVE OF ALL OTHER WARRANTIES, WHETHER EXPRESSED OR IMPLIED, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICU-LAR PURPOSE.

# 1.3 Instrument Description

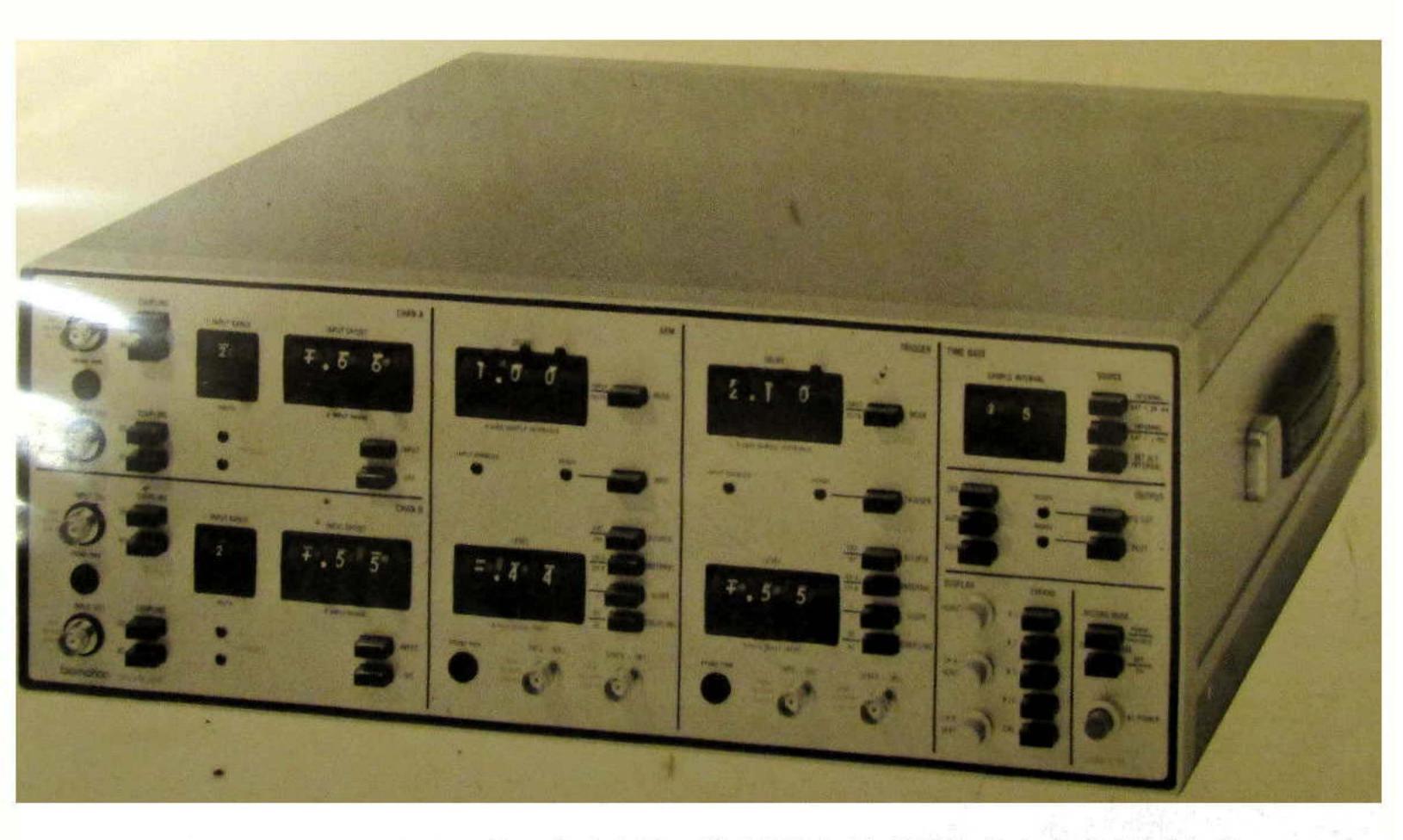

The Model 8100 Waveform Recorder is a compact solid state electronic instrument that stores the digital equivalent of electrical waveforms in memory. The outputs of the Model 8100 can be interfaced to display instruments such as oscilloscopes, CRT displays, plotters or strip chart recorders. It can also be interfaced directly to digital computers and is readily interfaced to digital recorders, time share terminals, magnetic tape storage devices, etc., as a part of a data acquisition system.

The Model 8100 is a bench-type instrument with tilt-up stand and may also be rack mounted, occupying a 7-inch vertical space in a standard 19" wide rack. Specifications for the Model 8100 are shown on the following pages.

NOTE: The total record time is given as 2048 times the sample interval and the memory length is stated as 2024 words. This apparent discrepancy is due

to the fact that, although the physical size of the digital memory is 2048 words, only (the first) 2024 words are guaranteed to contain accurate data.

# 1.4 Specifications

#### **ANALOG INPUT CHARACTERISTICS**

**Channels.** Two independent channels, each differential or single ended. Dual channel operation (inputs sampled alternately) is permissible for sample intervals of 100 nS or greater.

**Impedance.** 50  $\Omega$  each input to ground. Unit will power and accommodate standard FET active probes to achieve 10 M $\Omega$ , 10 pf input impedance, with 10:1 voltage division.

**Range.**  $\pm 50$  mV to  $\pm 5$  V full scale (100 mV to 10 V peak to peak). Independent selection on each channel by 7 position (1, 2, 5 sequence) lever switch. Attenuator accuracy  $\pm 3\%$  on any position.

Maximum Voltage. 25 V peak, 8 V RMS.

Coupling. AC or DC for each input of each channel. Time constant of 100  $\mu$ S on AC coupling.

Offset. Zero to  $\pm$  0.99 of full scale. Selections in increments of 0.01 of full scale.

Offscale Indicators. ± Offscale indicators to indicate signals beyond range of A/D.

**Bandwidth.** DC to 25 MHz for DC coupling on all ranges. Low frequency 3 dB cutoff of 1.5 KHz on AC coupling.

**Overload Recovery.** Less than 10 nS for recovery from 500% (5X) overload. Less than 50 nS for 10X overload. Subject to maximum input voltages above.

Common Mode Rejection. 40 dB from DC to 10 MHz.

DC Stability. Drift, including offset, of less than 5% of full scale over 24 hours.

**Gain Stability.** Gain changes less than 3% over 24 hours, less than 1% over ten minutes.

#### **ANALOG TO DIGITAL CONVERTER**

Resolution. 8 Bits (1 part in 256, or .4%) at all sampling rates.

Effective Aperture Uncertainty. Less than 2 nS.

Bit Rate. 800 Megabits per second at .01  $\mu$ S sample interval.

# TIME BASE AND MEMORY

Sample Interval. INTERNAL. Selectable.  $01~\mu S$  to 10~S, in a 1, 2, 5 sequence with range multipliers of  $\mu S$ , mS, S. EXTERNAL. Via rear panel BNC connector, TTL level (0 to +5~V), samples on negative going edge. Continously variable intervals between following bands:  $.02~\mu S$  to .25~m S, .25~m S to 1~m S, and greater than 1~m S. Minimum pulse width 10~n S.

Time Base. 100 MHz crystal controlled oscillator.

**Memory.** 8 bits X 2048 words. First 2024 words specified to contain valid data. In dual channel operation, 1012 words shared per channel. Dynamic MOS shift register.

**Total Record Time.** 2048 times sample interval. Varies from 20  $\mu$ S to 20 000 S (5.55 hrs.) when using internal sample interval selection.

#### ARM AND TRIGGER FUNCTIONS

These specifications apply equally to both functions.

Auto. Function provided automatically at a fixed interval internally.

Input. MANUAL. Front panel pushbutton.

INTERNAL. Selectable either Channel.

**EXTERNAL.** Front panel BNC; 50  $\Omega$ , 1 K $\Omega$  impedance.

**Slope.** Selectable positive or negative.

Coupling. Selectable AC or DC. DC only for internal, dual channel.

**Level. INTERNAL.** Adjustable from 0 to  $\pm$  0.99 in increments of 0.01 of input range.

**EXTERNAL.** Adjustable in increments of 0.05 V (50  $\Omega$  input) or 0.5 V (1 K $\Omega$  input).

Width. Greater than 50 nS.

Amplitude Change. INTERNAL. 5% of input range. EXTERNAL. Greater than 200 mV.

Maximum Input Voltage. 50  $\Omega$  INPUT. 25 V peak, 8V RMS. 1 K $\Omega$  INPUT. 100 V peak, 30 V RMS.

**Delay. ADJUSTMENT.**Selectable in increments of 10 sample intervals from 0 to 9990 sample intervals.

**STABILITY.**  $\pm$  one sample interval.

Synchronizing Connectors. Rear Panel BNC connectors for event distribution among several 8100s.

# **RECORD MODES.**

**Normal.** Unit will accept trigger after (delayed) arm. Recording begins at (delayed) trigger. Recording stops after 2048 sample intervals.

**Pretrigger.** Recording starts with arm signal, and stops with (delayed) trigger signal. Mode provides storage of entire leading edge of a pulse while detecting a trigger from any part of the pulse, allowing user to look back in time.

**Dual Time Base.** A given record sweep may start at one sample interval and switch to another sample interval during the sweep. Usable in both Normal and Pre-trigger Modes. Not usable when one sample interval is greater than 0.5 mS and the other is less than 0.5 mS; whenever the alternate, or second, sample interval is 0.01  $\mu$ S.

#### **ANALOG OUTPUT**

X Out. Repetitive 1 Vpp ramp, 1 mS period. Origin adjustable between -1 V and + 0.2 V. Sweep expansion selectable X1, X2, X5, X10 (1 V, 2 V, 5 V, 10 V ramp).

Y Out. Repetitive analog reconstruction of data in memory. Full scale amplitude 0.8 V, internally adjustable from 0.5 V to 1.2 V. Origin adjustable ± 1X full scale. Independent position adjustment for channels A and B.

**Z Out.** Nominal 0 to + 5 V pulse, 24  $\mu$ S duration. Used for display scope time base trigger, or for CRT display blanking.

**Z Out.** Nominal + 5 to 0 V pulse, 24 μS duration. Used for display scope time base trigger, or for CRT display blanking.

Display Calibrate. Full scale square wave with period of 400 sample intervals. Applied to Y Out BNC connector via front panel pushbutton.

Plot. When in Edit Mode, front panel pushbutton initiates single analog output of memory contents for input to an YT plotter or strip chart recorder. Standard output rate is 10 mS per point (20 S total plot time), 20 mS per point for dual channel output. Optional rates

Pen. 1 mS positive TTL pulse coincident with start of plot output. Optionally available as an inverted pulse (TTL level), or as a positive TTL level during entire plot output.

#### **DIGITAL INTERFACE**

Control Signals. Command input, Flag output, TTL levels (0 to +5 V). Selectable positive or negative true.

Digital Output. OFF. Digital output not available. Unit automatically reverts to display mode when not recording.

> AUTO. Single data output (2048 words) at end of record sweep. Reverts to display output after data output completed.

EDIT. Output mode enabled upon demand.

DATA OUTPUT. 8 bit parallel, TTL levels. No output when not addressed. Selectable positive or negative true. Asynchronous transfer under Flag/Command handshake control. Average data rates continuous from 10 K to 2 M words/sec. Data rates less than 10 K words/sec. exhibit up to 1 mS latency.

Programming. PROGRAMMABILITY. All front panel controls are programmable, except display controls and power switch.

> PROGRAM INPUT. 16 bit parallel, TTL levels. Selectable positive or negative true. Three bit address assignment and three bit address field.

#### **MISCELLANEOUS**

Size. HEIGHT. 6.25 in (16 cm).

WIDTH. 17 in (43 cm).

DEPTH. 21 in (53 cm), exclusive of front panel controls and

connectors.

WEIGHT. Approx. 60 lbs. (27.2 Kg).

Power. Approx. 200 W, 115/230 V RMS, 50-60 Hz.

#### SECTION II

#### Installation

#### 2.1 Introduction

This section contains information on unpacking, inspection, repacking, storage and installation of the Model 8100.

# 2.2 Unpacking and Inspection

Inspect instrument for shipping damage as soon as it is unpacked. Check for broken knobs and connectors; inspect cabinet and panel surfaces for dents and scratches. If the instrument is damaged in any way or fails to operate properly, notify the carrier immediately. For assistance of any kind, including help with instruments under warranty, contact your local Gould Inc., Biomation Division representative or Gould Inc., Biomation Division in Santa Clara, California, U.S.A.

# 2.3 Storage and Shipment

To protect valuable electronic equipment during storage or shipment, always use the best packaging methods available. Contract packaging companies in many cities can provide dependable custom packaging on short notice. A factory approved shipping carton can also be obtained by contacting Biomation.

# 2.4 Power Connection

Line voltage: the Model 8100 may be operated from either 115 or 230 volt ( $\pm 10\%$ ) power lines. The line cord connector contains a line filter.

The desired line voltage may be selected as follows: disconnect the line cord at the instrument. Using a narrow blade screwdriver, slide the voltage selection switch so that the proper line voltage appears on the switch.

For 115 V operation, use a 3A slow blow fuse. For 230 V operation, use a 1.5A slow blow unit.

<u>CAUTION</u>: Before plugging instrument into AC power line, be sure line voltage switch is properly positioned.

Power cable: the Model 8100 is equipped with a detachable 3-wire power cable. Proceed as follows for installation:

a) Connect line-cord plug (3-socket connector) to AC line jack at rear of instrument.

b) Connect plug (2-blade with round grounding pin) to 3-wire (grounded) power outlet. Exposed portions of instrument are grounded through the round pin on the plug for safety. When only a 2-blade outlet is available, use a connector adapter, then connect the short wire from the side of the adapter to ground.

# 2.5 Preparation for Use

The Model 8100 can be operated in a self-contained system by simply connecting it to a CRT display or oscilloscope. Or it can be interfaced with other types of instrumentation for data storage or analysis. The following sections of this manual cover operation, setups and interface requirements.

# 2.6 Initial Warm-up

Although the Model 8100 is a solid state instrument, a brief warm-up period of approximately 10 minutes is required for the input amplifier and the analog-to-digital converter to reach thermal stabilization.

#### SECTION III

# Principles of Operation

#### 3.1 Introduction

The Model 8100 Waveform Recorder presents new standards of performance for digital data acquisition equipment. The unit is a member of a class of electronic instruments that uses digital techniques to record a defined time segment of an analog signal. Thus, the waveshape, during the selected period of time, is recorded and held in the instrument's memory. The information stored in the memory can be output in any or all of the following three ways:

- 1. A reconstructed analog signal is available repetitively along with an appropriate sweep ramp and a retrace blanking signal to produce a flicker-free display on a CRT or oscilloscope.

- 2. The reconstructed analog signal is available at very slow rates for hard copy recording on a strip chart or XT recorder.

- 3. The signal is available in digital form for input to a digital recorder and/or a digital computer for off-line signal analysis or processing.

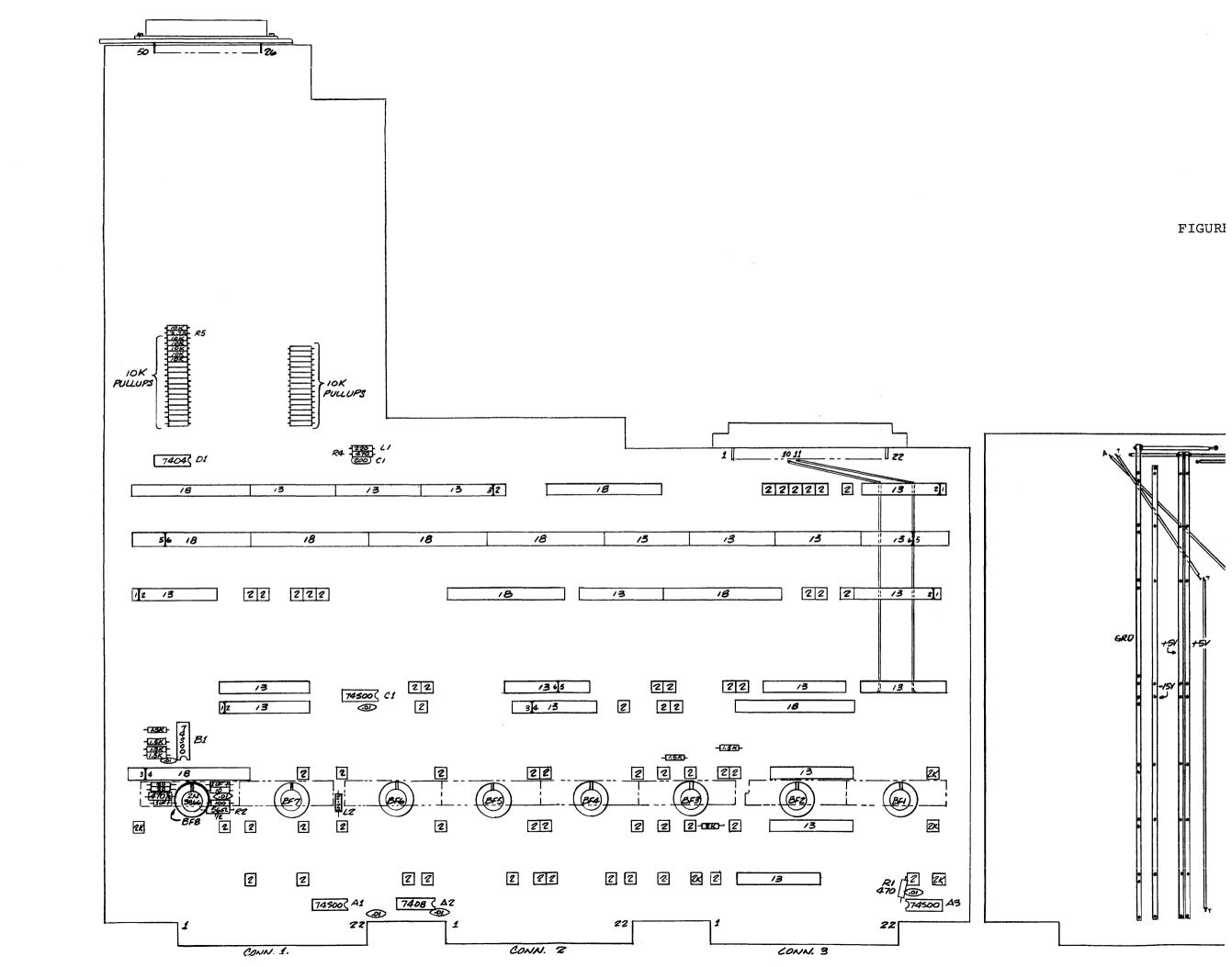

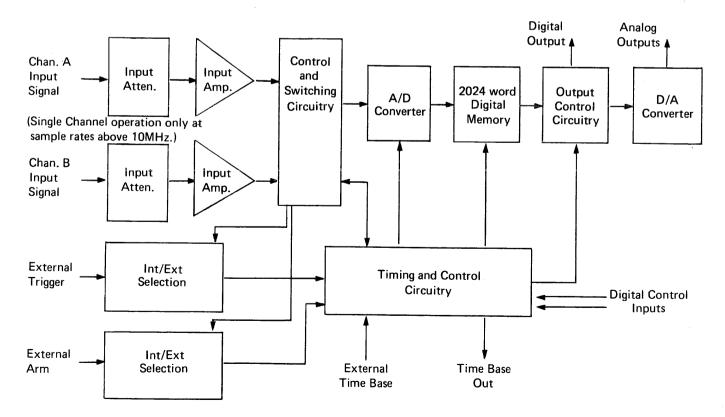

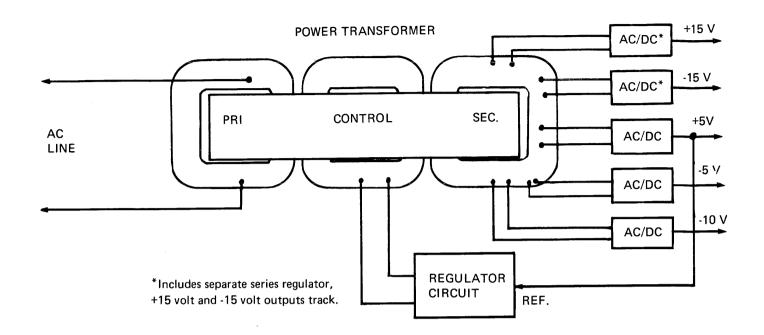

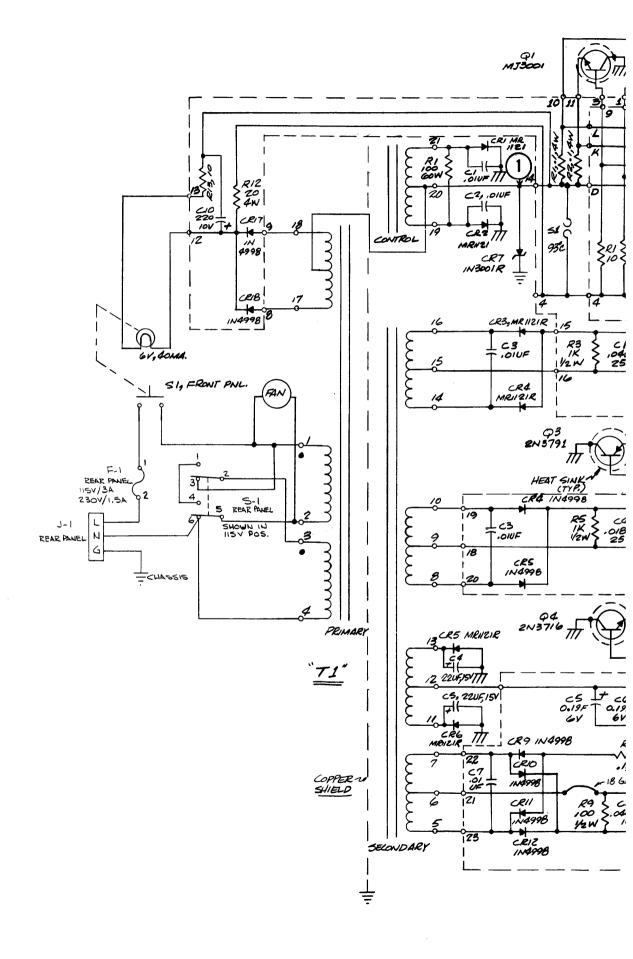

Figure 3.1

# 3.2 Basic Functional Description

The waveform recorder as an electronic instrument is conceptually quite simple. Its basic form consists of an A/D converter integrally connected with a digital memory, both of which are regulated by common timing and control circuitry. A digital-to-analog converter is also included to produce an analog output in addition to the digital output. Versatile arming, triggering and other user functions are also featured. A simplified block diagram of the Model 8100 is shown in Figure 3.1.

## 3.2.1 Signal Inputs

Two signal input channels are provided with an input attenuator and amplifier for each channel. Each channel is useable independently and provides a choice of single-ended, inverted, or a balanced input. The two input channels are also useable simultaneously at sample rates up to 10 MHz (100 nsec sample intervals) with half of the memory used for the samples from each input. When both input channels are used, successive samples are taken alternatively by each input channel. This results in an effective sample rate per channel of one-half of the selected sample rate for the unit.

### 3.2.2 Arm and Trigger Inputs

Signals to provide the Arm and Trigger Functions for the Model 8100 can be independently derived from the input signal from either channel or from external sources. External Arm and Trigger inputs are provided for five volt or fifty volt full-scale signals. Synchronizing connections are also available to permit simultaneous arming and/or triggering of multiple units.

### 3.2.3 External Time Base Input and Time Base Output

An external time base input is provided to permit the sampling rate to be determined by an external oscillator. The circuitry is arranged such that the sample rate will be at the same rate as the external time base input signal when this input is being used. If a nonlinear external sample rate is used, it must be constrained to <0.25 msec, 0.25 msec to 1.0 msec, or >1.0 msec intervals. Alternatively, the internally derived sampling frequency is provided via an output connector to permit the synchronization of other devices to the sampling frequency in the unit.

# 3.2.4 Digital Control Inputs

A comprehensive digital control interface is provided that permits remote digital control of all controls and functions of the unit with the exception of the analog output display controls and the on/off power switch. This interface accepts digital instructions as successive 16 bit words, stores each instruction and executes each desired function. Refer to Section 5.5 for a detailed description of the Digital Control Inputs.

#### 3.2.5 Digital Output

The digital output is arranged such that it can be accessed and

controlled in conjunction with the digital control inputs. operational status of the unit as well as the digital data in the unit's memory can be output under the direction of the digital control inputs. Alternatively, the digital data in the memory can be output directly under the control of simple front panel functions and the device receiving the data. output data is available for asynchronous transfer under flag/ command "handshake" control. IMPORTANT - Once the digital output of the data is initiated, the unit is prohibited from accepting an Arm or Trigger signal. This prevents the stored data from being changed until it has been "dumped". Average data rates are continuous from 1 x 10 $^{\circ}$  to 2 x 10 $^{\circ}$  words/sec. Data rates less than 1 x 10 words/sec will exhibit up to 1.0 msec latency, i.e., if more than 100 usec occurs between data request commands, delays of up to 1.0 msec will occur between output data Flags. When in the digital output mode, further recording is inhibited. Refer to Section V for a detailed description of the digital output functions.

# 3.2.6 Analog Outputs

A reconstructed analog signal output is provided in two forms. The Y display output presents the reconstructed signal repetitively (approximately once each millisecond) to permit the signal to be continuously displayed without flicker on a cathode-ray-tube display or oscilloscope. The unit also produces a synchronized sweep ramp output (X output) to provide the horizontal deflection signal for the CRT plus a direct (Z output) and inverted (Z output) retrace blanking signal for CRT display. The reconstructed analog signal is also available (but not simultaneously) for output to a strip-chart recorder or YT plotter. The standard plot time is 20 sec. No compatible sweep ramp is provided in conjunction with the plot output, but a "pen" signal is produced to facilitate the use of this feature. When two channel operation is used, each channel is displayed on alternate output sweeps and each channel may be plotted separately. As with the digital output. Arm or Trigger signals are prohibited during a Plot output sweep.

#### 3.3 Operational Functions

Operation of the Model 8100 Waveform Recorder resembles in many respects the operation of an oscilloscope. The 8100 does, however, provide greater flexibility, settability and range of control functions than normally found on most oscilloscopes, as well as operational features not possible with an oscilloscope. Anyone familiar with the use of modern laboratory oscilloscopes should be able to efficiently operate the Model 8100 after a relatively short learning period.

The operation of the Model 8100 is basically concerned with the signals or events that determine the initiation and termination of the sampling and recording of the input signal. The following subparagraphs describe the various signals and events and their interrelationships in the functional operation of the unit.

#### 3.3.1 Sweep and Sweep Time

In the following discussions the terms "sweep" and "sweep time" are often used. The term "sweep" is used to designate the succession of samples taken on the input signal during a recording sequence. The term "sweep time" is used to designate the amount of time required to fill the memory with contiguous samples of the input signal. When this term is used, it is normally assumed that the entire sweep was accomplished at a single linear sample rate.

#### 3.3.2 Arm, Trigger and End-of-Sweep Functions

The Arm, Trigger and end-of-sweep functions, together with two adjustable delays (associated with the Arm and Trigger events) control the sequence-of-events in the operation of the record cycle of the Model 8100. The effect of each of these functions or events on the sequence-of-events is dependent upon the operational configuration or mode of operation selected for the unit. This interdependence will be described in a later paragraph.

The Arm function could also be termed "trigger #1" or trigger reset. Detection of an event to "Arm" the unit has all of the flexibility of the Trigger function, i.e., it can be derived internally from the input signal of either channel or from a separate external input. The detection threshold is adjustable over the entire input signal range and can be selected for positive or negative signal transitions, and the detection level can be based on the dc value of signal or the relative value by removal of the dc component. In addition, all of these criteria for the Arm function can be bypassed by selection of the Auto Arm function which provides an automatic Arm event for each successive record sequence. The essential thing to remember is that the Arm and its attendant delay function must occur prior to the Trigger event, or succinctly: no Arm -- no Trigger!

The Delayed Arm function is self explanatory. The amount of delay is adjustable from 10 sample intervals minimum (see P 65B) up to five times the sweep time.

The Trigger function could also be called "Trigger #2," and detection of the event to provide this function has all of the flexibility of the Arm function described above including an Auto Trigger function for the trigger event for each successive record sequence.

Similarly, the Delayed Trigger Function is available and is adjustable from 10 sample intervals minimum (see p 65B) up to five times the sweep time.

The end-of-sweep function, or the EOS function as it is sometimes abbreviated, occurs 2048 sample intervals after recording commences.

# 3.3.3 Modes of Operation

The operational modes for the record sequence in the Model

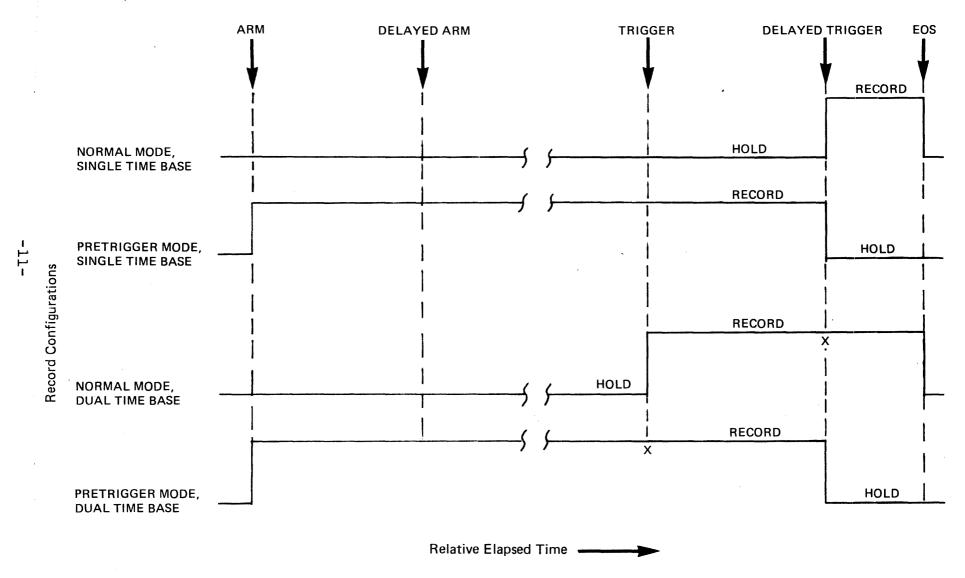

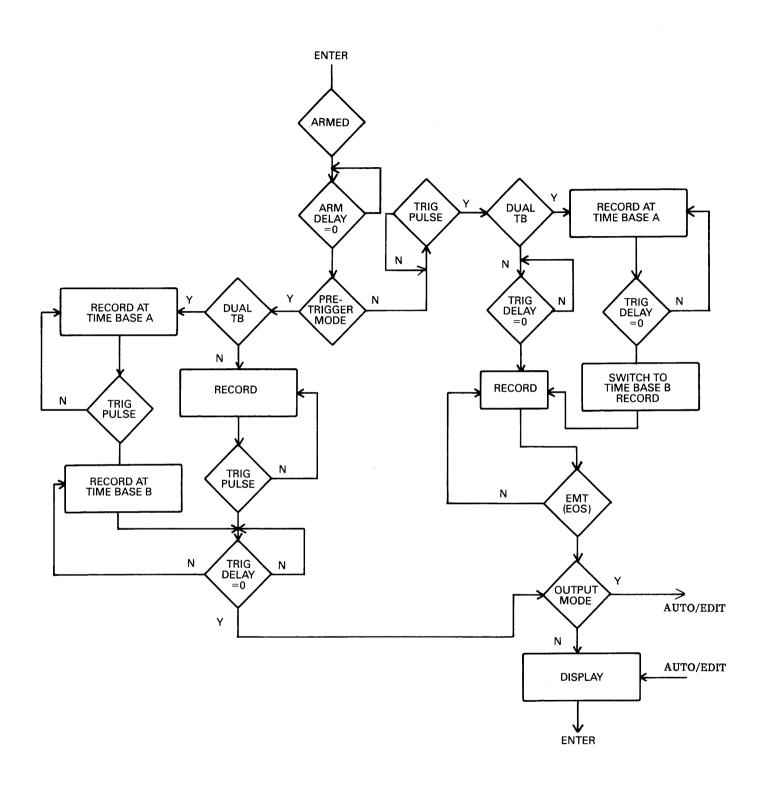

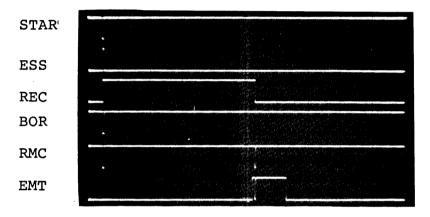

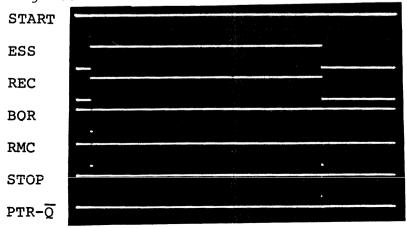

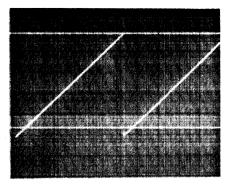

8100 are determined by the record mode selected and the choice of the Single or Dual Time Base function. Two basic record modes are provided. They are called Normal mode and Pretrigger mode. The time base function selection and the record mode selection provide four basic record configurations under the control of the Arm, Trigger and EOS events described in the preceding paragraphs. These four record configurations are illustrated graphically in Figure 3.2.

#### 3.3.3.1 Normal Record Mode, Single Time Base

In the normal record mode with the dual time base turned off (single time base), the record cycle is initiated by the Delayed Trigger, and it is ended at the end-of-sweep (EOS). This operation configuration can be used in various ways depending on the setting of the Arm and Trigger delays. With both delays set to zero, a straight-forward Normal sweep mode is produced.

If the Arm Delay is set for a significant delay time, a mode of operation sometimes referred to as "trigger holdoff" is produced. Trigger hold-off is useful to examine a relatively short-lived signal that occurs at low repetition rates. If the signal is such that the only signal (or trigger) perturbations are those which are the object of investigation, then there is no problem. However, it often occurs that the signal under investigation is accompanied with unwanted perturbations which are capable of triggering the unit. The Arm Delay can be used in such cases to "holdoff" the acceptance of a trigger until the unwanted perturbations have passed. In this way the desired information in the memory will not be disturbed.

The Normal sweep mode can also be configured for "delayed sweep" operation by setting the trigger delay to a significant value. The delayed sweep mode of operation is used in situations where the only good trigger signal precedes the data to be recorded. In many cases the delay between the trigger and the desired information is greater than the optimum sweep time. In these cases the signal would not be recorded with sufficient resolution to be useful. By delaying the initiation of the sweep with the Trigger Delay and sampling the signal at a faster rate, the information can be recorded with good resolution.

#### 3.3.3.2 Pretrigger Mode, Single Time Base

Pretrigger recording is a unique feature of Biomation Waveform Recorders. Pretrigger recording allows the capture or recording of signals that are not known to be significant for recording until after the signal has occurred. Another good use of this mode is in cases where the only good trigger available follows the information of interest.

In the normal recording modes the memory is filled with new information when the trigger occurs, or later. In the pretrigger recording mode of operation the memory is continuously being updated after the unit has been "Armed," and will discard information (from the "other end" of the memory) at the same rate. When the trigger occurs, the recording function ceases after the selected Trigger Delay time. If the Trigger Delay is zero, the memory will contain the information for the signal which occurred for one complete sweep time

# **Controlling Events**

X = SWITCHING POINT BETWEEN TIME BASE A AND TIME BASE B

Figure 3.2 Model 8100 Record Modes

prior to the trigger. The delay set on the Trigger Delay in this mode will determine which portion of the signal in the memory occurred after the trigger. Thus, any portion of the sweep time can be set to occur before or after the trigger event in the Pretrigger record mode of operation by simply adjusting the Trigger Delay setting. In this mode, the Arm Delay determines what portion of the memory will be filled before allowing a Trigger. If the sum of the Arm Delay and Trigger Delay is set to a total of 2000 sample intervals or more, one can be sure that the entire memory will be filled with useful data during each measurement cycle.

#### 3.3.3.3 Dual Time Base Operation

The dual time base operation of the Model 8100 permits the recording to begin at one sweep rate and conclude with a different sweep rate, i.e., sampling of the input signal in the dual time base rate and switches to sample intervals at another linear rate for the conclusion of the recording period. The point at which the switching occurs is dependent upon the front panel control settings and the record mode selected as described in the succeeding paragraphs. The Dual Time Base operation is useable for most combinations of sample intervals for each portion of the record sequence with the following exceptions:

- 1. The Dual Time Base function is not useable when one sample interval is less than 0.5 msec and the other sample interval is greater than 0.5 msec.

- 2. The Dual Time Base function is not useable when the second sample interval (alternate time base) is 0.01 usec, i.e., if the alternate time base is set for a sample interval of 0.01 usec, Dual Time Base operation is not specified to provide accurate sampling and storage of the input signal.

#### 3.3.3.4 Normal Sweep Mode, Dual Time Base

This mode of recording permits the recording of an input signal with portions of the signal recorded at two independent rates. This is particularly useful in studying waveforms which contain fast and slow components. The point at which the record rate switches from the first sweep rate to the next is determined by the setting of the Trigger Delay. Thus, recording is initiated by the Trigger, the rate is changed by the Delayed Trigger, and the recording is terminated by the EOS. "Trigger holdoff" operation is available in this mode through use of the Arm Delay as described above, but delayed sweep cannot be accommodated because the Trigger Delay is used for the record rate switching.

#### 3.3.3.5 Pretrigger Mode, Dual Time Base

This mode is essentially the same as the Pretrigger Record mode described above with the addition of the switching of the record rate by the Trigger. This mode is very convenient for recording at a slow rate a long period of time (but relatively few samples) prior to a

trigger event, and then recording at a rapid rate (good time resolution) the signal occurring after the trigger event.

# 3.4 Data Acquisition Limitations

The Model 8100 is basically an all-digital instrument. The user should not overlook this fact because, by its very nature, the digital approach to signal storage has certain limitations. There are some conditions under which these limitations can seriously affect the quality of the information stored. This section will deal with these limitations.

#### 3.4.1 Sampling Rate

The sampling theorum states that the sampling rate must be at least twice the highest input frequency to be measured. In practical situations any complex waveform, such as a sine wave, should have at least five data points throughout the full cycle in order to adequately display the signal details. The sampling limitation can easily be demonstrated by taking a high frequency continuous signal, such as a sine wave, and operating the Model 8100 through all of its available sweep speeds. It will be observed that at slow sweep speeds a very respectable signal can be obtained which bears a little or no relationship to the input signal. This limitation can be avoided by the use of the proper sweep time or with an external low pass filter to attenuate the frequencies above the band of interest.

# 3.4.2 Output Smoothing

The digital information coming out of the Model 8100 memory goes through a smoothing digital-to-analog converter. This converter makes the output appear to be a somewhat continuous trace rather than a series of points normally expected from a digital instrument. The most important thing to remember is that the digital information contained in the memory may indicate a faster risetime than the visual presentation because of the smoothing circuit employed in obtaining the visual presentation.

#### 3.4.3 Amplitude Resolution

The Model 8100 converts all analog input signals to an accuracy of 8 binary bits. This means that the resolution can be no better than 1 part in 256, or 0.4% of the full scale amplitude. Note that resolution does not imply an accuracy specification. Resolution is 0.4%; accuracy depends on resolution, drift, gain tolerance, signal slew rate vs A/D aperture, and amplifier bandwidth, among other things.

#### SECTION IV

#### Operation

#### 4.1 Introduction

This section identifies and describes front panel controls, rear panel connections and typical operating procedures. Included are complete descriptions of front panel controls and their effective ranges, location and proper use of rear panel connectors, setup procedures prior to using the Model 8100, and step by step operating procedures for various modes of operation. A thorough understanding of this section is essential to the successful use of the instrument.

#### 4.2 Front Panel Controls and Connectors

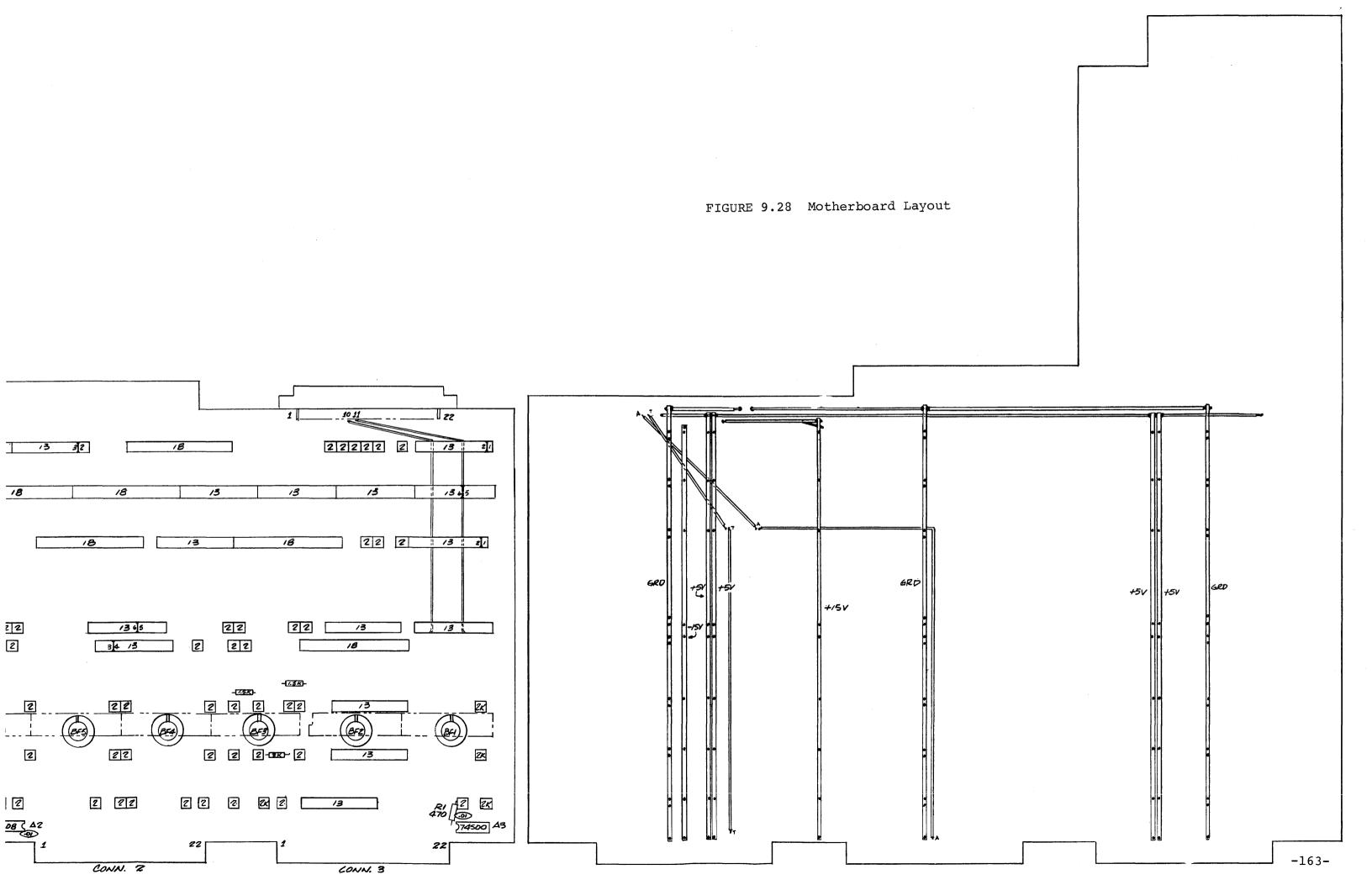

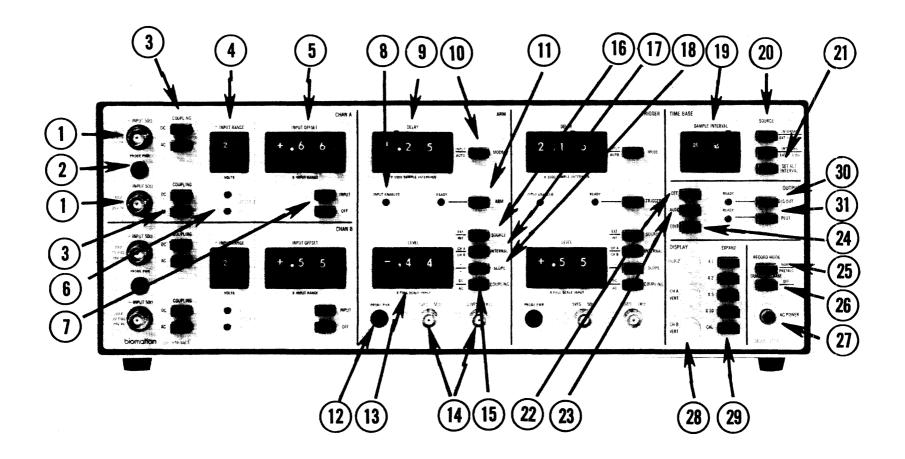

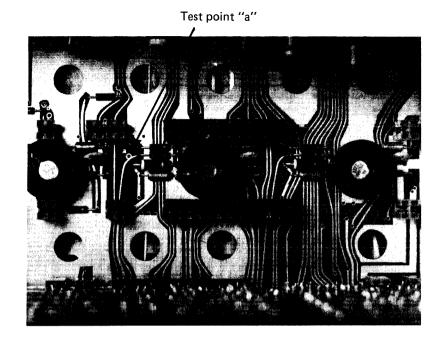

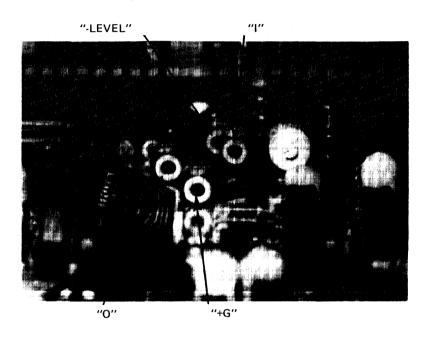

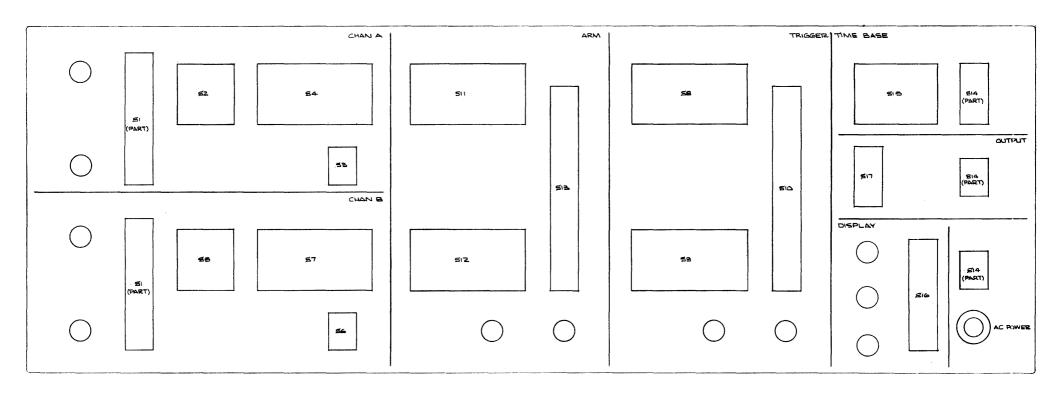

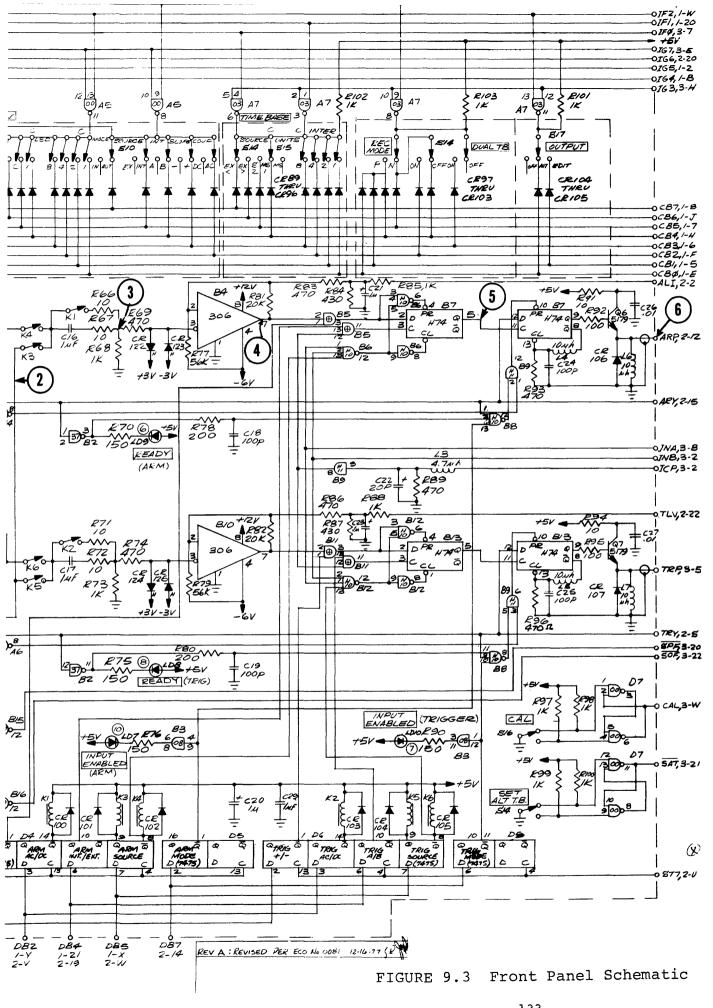

#### 4.2.1 Control Clusters

The controls of the Model 8100 are divided into eight groups called "control clusters." The groups contain separate controls with related functions. For convenience, they are presented together with a photograph of the front panel in Figure 4.1. The eight control clusters are as follows:

Channel A Input Time Base

Channel B Input Output Modes

Arm Display

Trigger Record Modes

# 4.2.2 Digital Switches

Advantage has been gained through the digital nature of the unit by permitting the extensive use of digital control switches in lieu of the more common analog "knob". This facilitates the readability and more importantly, the repeatability of the control settings. Use of this type of controls by the uninitiated does require some familiarization.

Two types of digital switches are used on the Model 8100. One is a novel multiposition switch resembling a common "Thumbwheel" switch, but utilizing a convenient "lever" to set the desired position. The other type used is a two-position pushbutton, also called a latching pushbutton switch. The control functions are given adjacent to each of these pushbuttons as a dual legend separated by a line. The upper legend designates the function selected when the pushbutton is out (unlatched) and the lower (bottom) legend is for the function selected with the pushbutton in (latched). In other words, Upper function: push button out; Lower function: push button in.

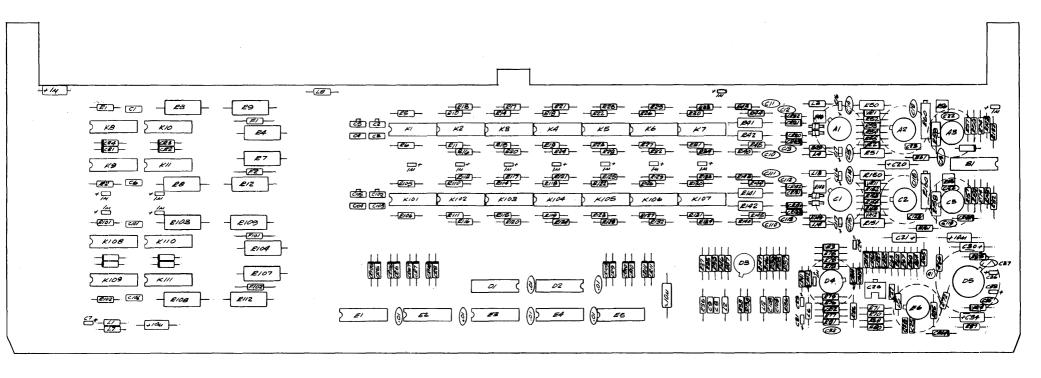

Figure 4.1 Front Panel Functions

# 4.2.3 Channel A Input Controls\*

### Signal Input Connectors (1)

Impedance 50 ohms to ground. Two BNC type connectors are used for the positive and negative voltage input.

#### Probe Power Output (2)

Provides 30 ma of +15 V and -12.6 V to power active FET probes such as the hp 1124A which gives input impedances of 10 megohm, 10 pf.

# Coupling (3)

Four pushbutton switches marked either dc or ac are associated with the two input connectors. If all four pushbuttons are not depressed, neither input is connected. If one pushbutton is depressed, single ended or inverted input will result with the indicated coupling, and if a pushbutton associated with each connector is depressed, a balanced input results.

# Input Range (4)

Full scale voltage ranges from  $\pm 0.05$  V to  $\pm 5$  V are selected by the digital lever switch. A 1-2-5 sequence gives plus and minus 0.05, 0.1, 0.5, 1, 2, and 5 volts full scale.

# Input Offset (5)

Level compensation from 0 to  $\pm 0.99$  times the input range is available. By off-setting a unipolar signal to center it around zero, the maximum possible resolution may be obtained.

\*Note: These identical functions and controls are provided for Input Channel B.

These indicators light if the input signal exceeds 100% of the input range at any time during the recording period. The indication is reset when the unit is Armed for the next recording cycle.

Input/Off (7)

These buttons connect or disconnect the input amplifier to the measurement circuitry. They also control the output sweep information in dual channel operation.

#### 4.2.4 Arm Controls

Input Enabled Indicator (8)

Lights when "INPUT" (10) is selected - see below. This indicates that an Arm signal must be provided for each complete record cycle.

Delay (9)

Determines the time between detection of the arming signal and the arming of the unit. Digital lever-switches provide delays from 0 to 9990 sample intervals selectable in intervals of 10 samples. A 10 sample interval delay exists between receipt of the Arm signal and when the unit will accept a trigger, and between the Trigger and start of recording. See p 65B.

Mode (10)

Selects "INPUT" or "AUTO" mode of operation. In INPUT mode, the ARM command is derived manually by push button, internally from the signal, or from an external pulse. In AUTO mode the unit Arms itself without waiting for a selected event. AUTO mode must be initiated by depressing the Arm push button.

-17.

#### Arm Pushbutton and Ready Light (11)

The Arm pushbutton is used to manually Arm the unit and to initiate the Auto-arm function. When the unit is ready to be Armed (i.e., is unarmed), the Ready Light is on. The Ready Light will also be extinguished by the timely occurrance of an internal or external Arm signal.

#### Probe Power Output (12)

Provides the same voltages as connector (2) above. This permits an FET active probe to be used on the 50 ohm Arm input (14).

#### Level (13)

Determines the level at which the unit Arms. The digital lever-switch is adjustable from 0 to  $\pm 0.99$  in increments of 0.01 of the Input Range for internal mode. For external Arm signals the 0.01 increments are the equivalent of 0.05 V on the 50 ohm input, or 0.5 V on the 1 K ohm input.

# Arm Signal Input Connectors (14)

Two BNC connectors are provided for the input of Arm signals from external sources. (The Arm signal enables the unit to recognize a trigger. See section 3.32.) The level control (13) determines the "Arming" level with respect to the appropriate full scale input voltage:

- 5 V full scale 50 ohms input impedance.

- 50 V full scale 1000 ohms impedance.

Power for an active probe to be used with the 50 ohm input is provided (12).

## Coupling (15)

A pushbutton that selects ac or dc coupling for the Arm circuitry. The coupling is to either Internal or External sources, as selected by the Source switch (16). Use is limited to dc only when Internal is selected and two channel operation is used.

#### Source (16)

Selects the source of the arming command. EXT (switch 16 out) selects Arm signals from the two BNC connectors (14). INT (switch 16 in) causes the unit to Arm when the input signal itself crosses the selected level (13) at the selected slope (18).

### Internal (17)

This pushbutton selects whether the Arm signal is derived from Channel A or Channel B when the Source button is set to INT. Arm signals from Channel A are used when the pushbutton is out, and from Channel B when the pushbutton is in.

# Slope (18)

Selects positive or negative slope for the Arm signal whether derived from Internal or External signals. Positive slope is required when the pushbutton is out (+), negative when the button is in (-).

# 4.2.5 Trigger Controls

These controls cause the unit to begin or end a measurement sweep as described in section 3.32. They are identical to the Arm controls described in 4.23, except that the controls all apply to Trigger instead of Arm.

#### 4.2.6 Time Base Controls

#### Sample Interval (19)

Digital lever-switches select the recording sample interval (linear record rate) of the internal time base. Intervals from 0.01 microsecond to 10 seconds are selectable with intervals of 0.01, 0.02, 0.05, 0.1, 0.2, 0.5, 1, 2, 5, 10  $\mu$ sec, msec, or seconds.

#### Source Internal/External (20)

Two bushbutton switches select the internal time base or permit an external clock signal to control the sample rate. With both buttons out, the internal source is selected. Pushing in the upper button permits clock pulses to be input with intervals from 20 ns to 0.25 ms per pulse. Pushing in the lower button (with the upper button out) permits clock pulses to be input with intervals of 1 ms per pulse or slower. Depressing both buttons permits external sampling pulses with intervals between 1 ms and 0.25 ms to be input.

#### Set Alternate Interval (21)

When used in the Dual Time Base mode (see section 3.33), this button is used to enter the alternate time base. In this mode the unit switches to an alternate (second) sample interval at a point controlled by the trigger delay setting. To select the alternate sample interval, set the SAMPLE INTERVAL switch to the second interval and momentarily depress the SET ALT INTERVAL button (21). This "stores" the information in internal registers. Change the SAMPLE INTERVAL switch to the desired first interval, and the two time bases are selected. CAUTION: The "stored" sample interval will be lost "erased" on loss of line power and will be indeterminate until reset.

# 4.2.7 Output Controls

These pushbuttons control the digital and plotter outputs of the Model 8100.

# Output Off (22)

With OFF depressed, the unit automatically switches to Display mode at the end

of the record period. No digital data is output and no plot output is possible.

# Automatic Output (23)

With AUTO depressed the unit automatically switches to the OUTPUT mode after the record sweep. Display is inhibited until the data has been clocked out of the 8100. Record is also prohibited until the data has been clocked out (2048 words) or until the output is switched OFF. After output, the Display mode will return and no further digital output can occur until after a subsequent record cycle.

#### Edit (24)

The EDIT mode permits the user to see the display before initiating digital output or a plot output sweep. The unit remains in Display until output is initiated by pushing the DIG OUT button (30) (or through the digital interface - see section V) to initiate the digital output, or the PLOT button (31) to initiate the plot output. In EDIT, the digital output or the plot sweep may be repeated on demand as many times as desired.

# Digital Output Initiate (30)

The DIG OUT pushbutton manually initiates the output of digital information in EDIT mode. The Ready light indicates that the record sweep is complete and the digital information is ready to be output.

# Plot (31)

This button causes the analog output to a plotter to be initiated in EDIT mode. During output the analog level being output is displayed on the screen. After a two channel record cycle, plots of the data from each channel can be selectively plotted by selecting the "input" selector (7) for the desired output channel and deselecting the unwanted channel by placing its Input (7) OFF.

# 4.2.8 Display Controls

Position Controls (28)

Control the position of the display output on the CRT face. The HORIZ and EXPAND are functional only when using the X output for the display sweep. Separate vertical position adjustments CH A VERT and CH B VERT are provided for two-channel operation.

Sweep Expand (29)

The Expand buttons enable the horizontal resolution of the display to be increased. In X1 the full 2000 points are displayed. By use of the X2, X5 and X10 buttons, protions of the recorded information may be "enlarged" to give a more detailed picture. For example, in the X10 position only 200 points are displayed along the X-axis. The HORIZ Control (28) enables the 200 points displayed to be selected anywhere on the recorded waveshape.

Calibrate (29)

The CAL button causes a full scale square wave with a period of 400 samples to be displayed for calibration and positioning on the scope face. It does <u>not</u> imply a calibrated input injected into the input.

#### 4.2.9 Record Mode Controls

Normal/Pretrigger Mode (25)

Selects the mode of recording used (see section 3.33). With the pushbutton in, "Pretrigger" recording is selected. With it out, "Normal" recording will occur (see section 3.3).

Dual Time Base On/Off (26)

Selects the Switched Time Base mode of operation (see section 3.3).

#### 4.2.10 AC Power Switch (27)

An illuminated switch indicates ac power on.

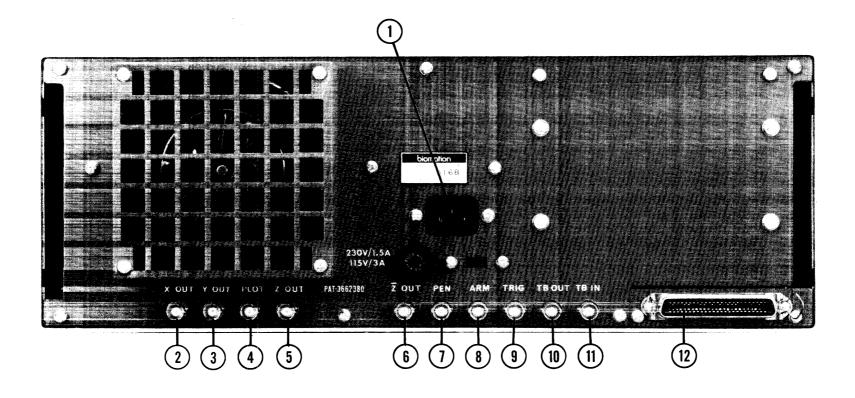

# 4.3 Rear Panel Controls and Connectors

Figure 4.2 shows the rear panel connections.

# 4.3.1 Display Outputs

X OUT (2)

A +1'.V peak ramp of 1 ms duration is provided for sweeping X-Y CRT displays. The origin is adjustable between -1 V and +0.2 V. The Sweep Expand buttons (#29 in Fig. 4.1) increase the ramp amplitude proportionately (2 V for X2, 5 V for X5, etc.).

Y OUT (3)

The analog representation of the stored signal is produced here for use with an X-Y display. Signal is .8 V full scale with origin adjustable ± 1.0 V dc and amplitude (internally) adjustable from .5 V to 1.2 V.

# 4.3.2 Blanking Voltages

Z OUT (5) and  $\overline{Z}$  OUT (6)

Provide signals for retrace blanking or oscilloscope trigger.  $\overline{Z}$  OUT is a TTL voltage level from 0 to +5 V (nominal) at the start of the display period. It stays positive for 2000 words (lms) and returns to 0 V for 24  $\mu s$  during retrace. Z Out is held at 0 V during display and goes to +5 V during retrace.

# 4.3.3 Plot Output (4)

Figure 4.2 Rear Panel Functions

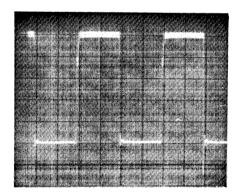

Analog output to drive a strip chart or YT recorder is provided when the front panel PLOT pushbutton is pushed. The standard plot sweep time is 20 seconds, optionally to 200 seconds.

Pen (7)

A 1 ms positive TTL pulse (+3 V) is provided at the start of the Plot Output period for pen or plotter control. Optionally available as a negative going pulse from +5 volts or a positive level during the entire plot sweep or a positive level whenever not in plot output.

## 4.3.4 Synchronizing Connections

Multiple 8100 units may share the same Arm and Trigger commands. The ARM (8) and/or TRIGGER (9) connectors of the units can be interconnected. For this operation the one unit is set to trigger as desired. The other units have the Arm and/or Trigger SOURCE set to EXT, and the Arm and/or Trigger LEVEL set to about +0.5 to avoid possible noise trigger. The end of the interconnecting cable/s should use  $50\Omega$  terminations.

NOTE: These are not inputs for external arm and trigger commands.

#### 4.3.5 Time Base

The time base selected by the front panel SAMPLE INTERVAL switch is available at TB OUT (10). This may be used to synchronize an experiment to the 8100 or as an external time base source for a second 8100. In that application it is connected to the TB IN connector (11) of the second unit. When an external time base is selected by the Time Base Source buttons (#20 in Fig. 4.1), it is supplied to the TB IN connector (11).

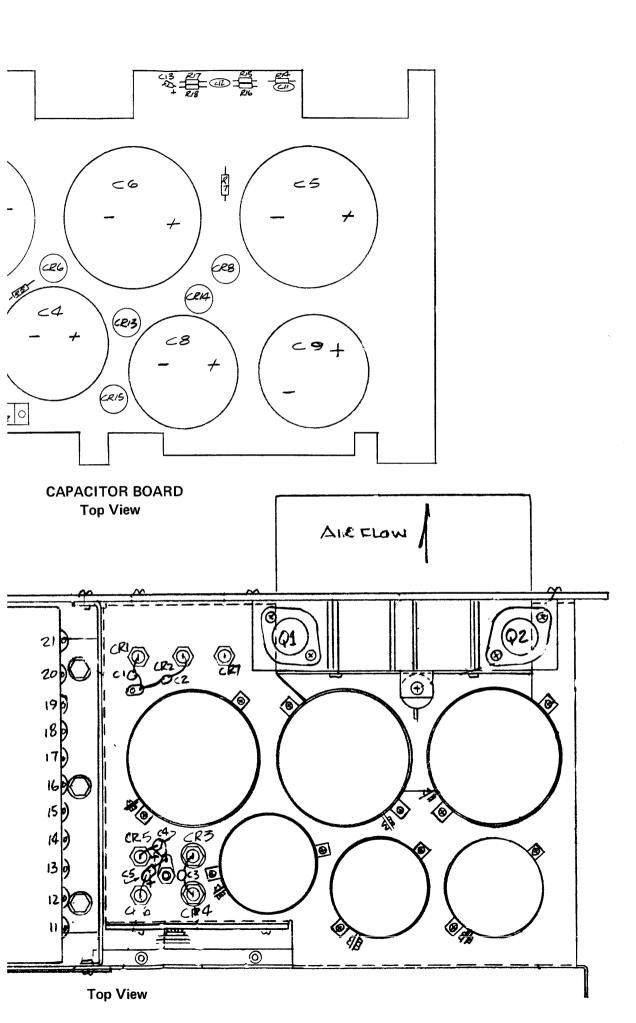

4.3.6 AC Line Connector, Fuse holder, and Line Voltage Selector (1).

The connector housing contains a line filter. Note the fuse ratings printed on the

rear panel. When changing line voltage, ensure that the proper fuse is used. The line voltage selector may be changed using a small screwdriver. Leave line cord unplugged while changing fuse and selector.

#### 4.4 Set Up Procedure

#### 4.4.1 Initial Set Up

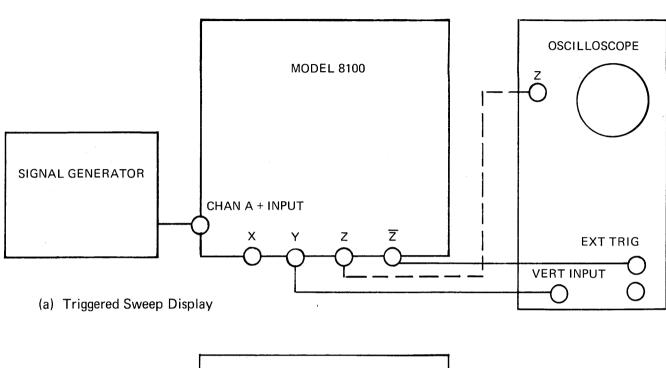

This section describes the connection of a Model 8100 with a CRT display or oscilloscope and the steps to record and display a known signal.

Before connecting the unit to line power, check the voltage selector switch on the rear panel to ensure that it is set to the proper line voltage and be sure that the correct size fuse (as printed on the rear panel) is installed.

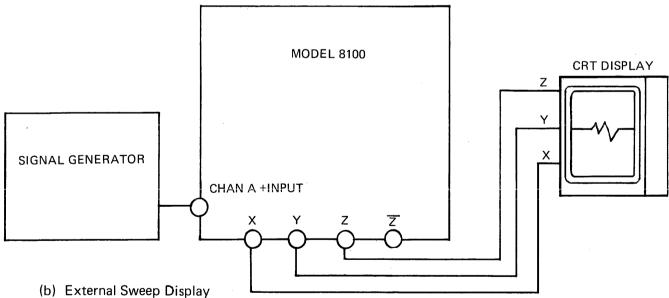

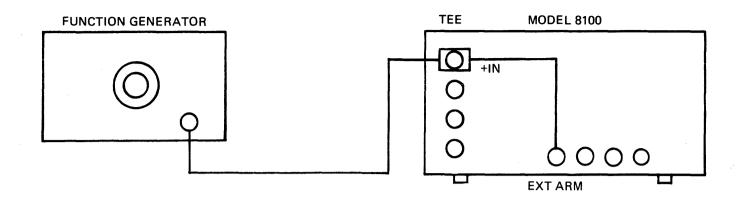

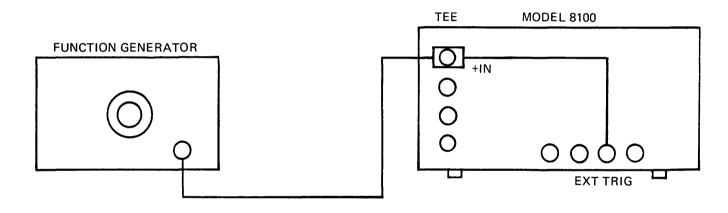

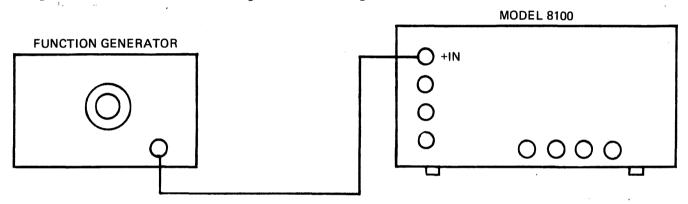

Connect the Model 8100 to a function generator and CRT display as shown in Figure 4.3a or 4.3b. It may be necessary to use the  $\overline{z}$  output of the 8100 for the retrace blanking signal as CRT drive circuitry varies greatly in the polarity of this input. NOTE - connection of the retrace blanking signal is optional when using the triggered horizontal sweep of an oscilloscope as in Figure 4.3a. If the retrace blanking signal is not used, a slightly displaced (in the X direction) "double" signal may be observed whenever the Model 8100 is repetitively triggered in rapid succession. CAUTION - Some older "tube type" oscilloscopes have a high voltage on their  $\overline{z}$  axis inputs. THIS COULD DAMAGE THE MODEL 8100's  $\overline{z}$  or  $\overline{z}$  OUTPUT.

Set the oscilloscope and function generator as follows:

Vertical sensitivity 0.1 V/div., dc coupled

Vertical position Middle of display

Horizontal sweep 0.1 ms/div. (Fig. 4.3a)

Horizontal sensitivity 0.1 V/div., dc coupled (Fig. 4.3b)

Trigger input +, dc coupled, External (Fig. 4.3a)

Function Generator 5 KHz, 2 volts peak-to-peak

Set the Model 8100 as follows:

#### CHAN A

SIGNAL INPUT +INPUT 50Ω

COUPLING DC (in)

±INPUT RANGE 1V

INPUT OFFSET 0.00

INPUT/OFF INPUT (upper switch in)

Figure 4.3 Display Interconnections

#### CHAN B

INPUT/OFF OFF (lower switch in)

Other CHAN B settings are arbitrary since the channel is off.

ARM

DELAY 0.00

MODE AUTO (in)

ARM Momentarily depress to

initiate Auto operation

All other ARM settings are arbitrary since arming is now automatic.

TRIGGER

DELAY 0.00

MODE INPUT (out)

SOURCE INT (in)

INTERNAL CH A (out)

SLOPE + (out)

COUPLING dc (out)

LEVEL +0.10

TIME BASE

SAMPLE INTERVAL 0.2 µs

SOURCE INTERNAL (both switches out)

OUTPUT OFF (in)

DISPLAY X1

RECORD MODE

NORM/PRETRIG NORM (out)

DUAL TIME BASE OFF (out)

Depress the CAL button.

Adjust the HORIZ and CH A VERT and/or the scope display position controls to center the full scale square wave.

Release the CAL button. Two complete periods of the 5 KHz input signal should be displayed on the CRT. If the signal is not full scale (same amplitude as the CAL square wave), see Section VI on Calibration and Maintenance Procedures.

# 4.5 Operating Procedures

In this section several modes of operation will be discussed and illustrated. A pulse generator capable of generating a single pulse upon manual command and able to drive a 50 ohm load is required.

Set the generator to give repetitive pulses  $100~\mu s$  wide, going from 0~V to slightly over +1 V and occurring at a 2~KHz rate.

# 4.5.1 Normal Mode

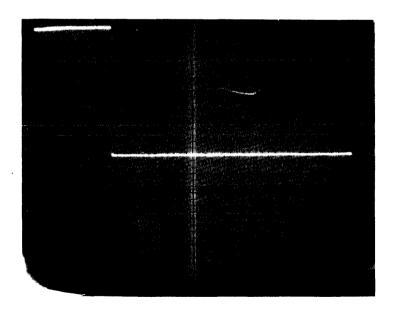

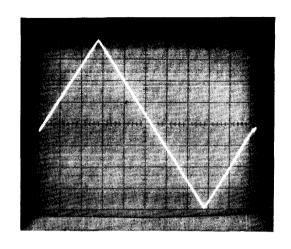

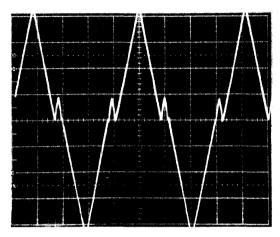

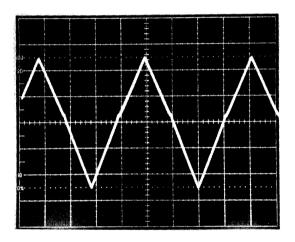

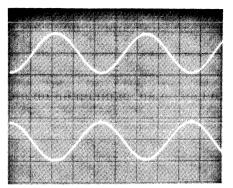

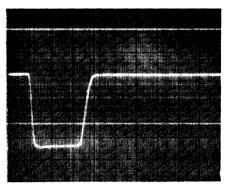

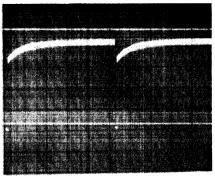

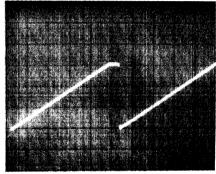

Set the Model 8100 and oscilloscope exactly as described in Section 4.41 above. The + OFFSCALE lamp will be lit. Reduce the amplitude of the input pulse to just under +1 V. The + OFFSCALE light should go out and the display should resemble Fig. 4.4.

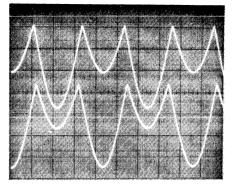

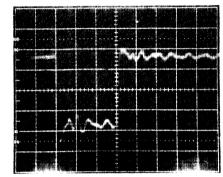

Figure 4.4 Zero Centered Measurement Signal

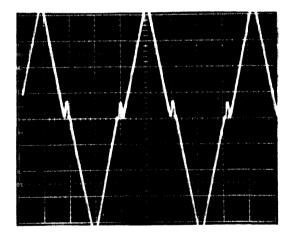

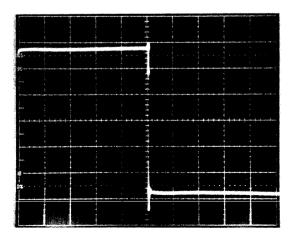

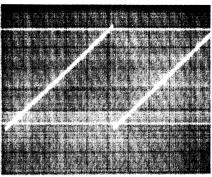

Change the INPUT RANGE to 0.5 V and the INPUT OFFSET to -0.99. The display should now resemble Figure 4.5.

Figure 4.5 Offset Measurement Signal

# 4.5.2 Pretrigger Mode

Make the following setting changes in the controls:

ARM

DELAY 1.00

MODE INPUT (out)

SOURCE EXT (out)

TRIGGER

DELAY 1.10

RECORD MODE PRETRIG (in)

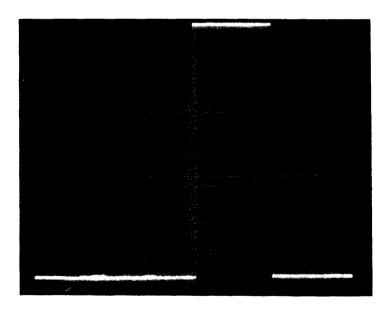

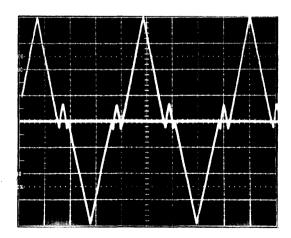

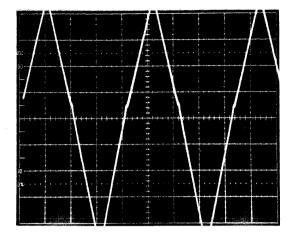

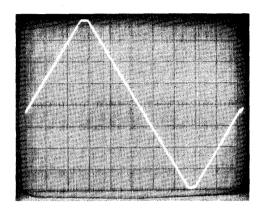

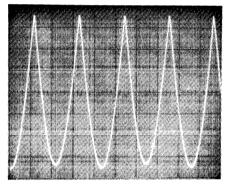

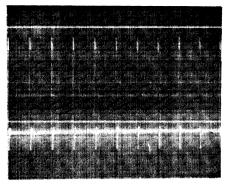

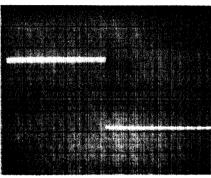

Press the TRIGGER push button then press the ARM pushbutton. The display should resemble Fig. 4.6. The pulse will be in the center of the screen. 1100 readings were taken after the trigger, and about 900 were retained from before the trigger.

For a more graphic example, change the Pulse Generator settings for a pulse width of approximately 100 ms and Single Pulse operation. Change the 8100 Sample Interval to 1 ms. Press the ARM button to cause recording to begin (see Section 3.33). The unit is now taking data, and a display of the base line will be shown. Produce a single pulse from the Pulse Generator. The pulse will move onto the display screen from right to left and stop at the center.

NOTE: In Pretrigger Recording, recording begins at Arm and terminates when the Trigger Delay has run out. Trigger is prohibited until the arm delay has run out. To insure that the memory contains continuous meaningful data, always make the sum of Arm and Trigger Delays greater than 2.05 so that at least 2048 new samples will be stored before recording is terminated.

Figure 4.6 Pretrigger Recording, Illustrating about One-Half of Recorded Signal Contains "Prior-Event" Data.

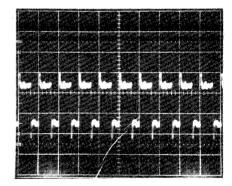

## 4.5.3 Switched Time Base Mode

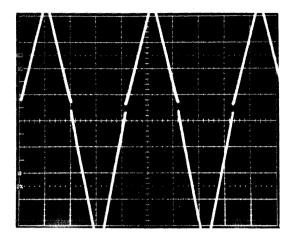

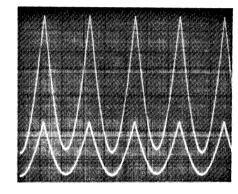

Return the settings to those used in paragraph 4.41 (except set the Channel A Input Offset to -0.99). The Switched Time Base mode will be used to illustrate a pulse at 50 ns per point (Time Base A), and after 400 samples will change time base to the 0.2  $\mu$ s per point (Time Base B) as used in paragraph 4.41.

Set the generator for 50 µsec repetitive pulses of 1.5 V amplitude at a 20 KHz rate. Change Sample Interval switch to 0.2 µs per point. Press the SET ALT INTERVAL. Set Sample Interval switch to 50 ns per point. The A and B time bases are now set. Set Trigger Delay to 0.40. Set Dual Time Base pushbutton to ON (in). The display should change to show one wide pulse and about 6 narrow pulses. Change the Trigger Delay and observe the shifting of the point of change in the sampling rate.

#### SECTION V

## Digital Control Interface

### 5.1 Introduction

The Model 8100 provides a versatile and comprehensive digital monitoring and control interface for remote and/or automatic operation and readout. This interface is designed to be especially convenient for operation with a digital computer (or computer terminal). In addition, the Model 8100 contains the necessary control, isolation and timing circuitry to allow it to be connected in parallel on a time-share "port" of a digital controller along with other like or similar devices. Conversely, the digital control interface can be hard-wired to simply output the data in the digital memory of the Model 8100 upon front panel and/or remote commands.

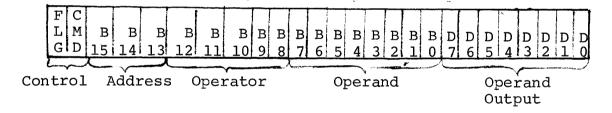

The digital control is effected via a bit-parallel, word-serial data exchange. That is, digital control functions are executed by successive digital "words" made up of a number of parallel bits. The versatility of this interface is greatly enhanced by a field of pins in the interface connector which allows the user (or system designer) to independently assign the logical definition of each sub-field of bits in the control "word". This is readily done with appropriate ground straps on the mating connector.

This field of hard-wire programming pins also contains three pins for assigning the "address" of the unit. Thus, a number of units can be connected in parallel on a digital "bus" and individually controlled.

Virtually all front panel control functions (except the power-on switch and the display positioning controls) can be exercised via the digital interface. However, not all of these controls need be under remote control at any one time. The remote control can be applied to the functions by control groups (such as the Arm or Trigger control groups). Thus, any control group or combination of control groups may be under remote digital control. Also, control of a control group or groups can be released for manual front panel operation and/or put under remote operation with the proper digital instruction.

Note that none of the front panel controls include an External or Remote position. This is because the digital interface has the ability to usurp control from the front panel without regard to the physical position of the manual buttons and knobs.

# 5.2 Connector Definitions

The 50-pin rear panel connector, J1, provides the physical interface for digital output and control. The connector is an Amphenol Micro-Ribbon 57-40500. The mating connector is an Amphenol part number 57-30500.

The pin assignments for the digital interface are listed in the following table:

| Pin # | Mnemonic       | Description                                        |

|-------|----------------|----------------------------------------------------|

| 1     | В0             | Input Data 2 (Least Significant Bit)               |

| 2     | B1             | Input Data 21                                      |

| 3     | B2             | Input Data 2 <sup>2</sup> Input                    |

| 4     | B3             | Input Data 2 <sup>3</sup> Operand                  |

| 5     | B4             | Input Data 2                                       |

| 6     | B5             | Input Data 2 <sup>5</sup>                          |

| 7     | В6             | Input Data 2 <sup>6</sup>                          |

| 8     | в7             | Input Data 2 <sup>7</sup>                          |

| 9     | B8             | Input Data 28                                      |

| 10    | В9             | Input Data 29 \Operator                            |

| 11    | B10            | Input Data 2 <sup>10</sup> (Function               |

| 12    | B11            | Input Data 2 <sup>11</sup> Code)                   |

| 13    | B12            | Input Data 2 <sup>12</sup>                         |

| 14    | B13            | Input Data 213                                     |

| 15    | B14            | Input Data 2 <sup>14</sup> Address                 |

| 16    | B15            | Input Data 215 (Most Significant Bit)              |

| 17    | CMD            | Command - An input used with Flag to               |

|       |                | regulate the data exchange.                        |

| 18    | $\mathtt{FLG}$ | Flag - An output used with Command to              |

|       |                | regulate the data exchange.                        |

| 19    | <b>T</b>       | Defines Pos or Neg logic for Inputs B0 thru B12    |

| 20    | _ 1.           | Defines address state for Bl3                      |

| 21    | Logic          | Defines address state for Bl4 Address              |

| 22    | Definition     | Defines address state for B15 Assignment           |

| 23    | Field          | Defines Pos or Neg logic for                       |

| 2.4   |                | CMD input.                                         |

| 24    |                | Defines Pos or Neg logic for                       |

| 25    | 1              | FLG output.                                        |

| 25    |                | Defines Pos or Neg logic for Outputs D0 through D7 |

| 26    | D0             | Output Data for 2 (LSB)                            |

| 27    | DI             | Output Data for 21                                 |

| 28    | D2             | Output Data for 2 <sup>2</sup>                     |

| 29    | D3             | Output Data for 2 <sup>3</sup> Output              |

| 30    | D3             | Output Data for 2 Operand                          |

| 31    | D5             | Output Data for 2 <sup>5</sup>                     |

| 32    | D6             | Output Data for 2 <sup>6</sup>                     |

| 33    | D7             | Output Data for 27 (MSB)                           |

| 34    | <b>.</b> .     | +5 V DC                                            |

| 35-50 | Ground         | Signal Common and Chassis                          |

| 33 30 | 310 and        | J 00:00:0:: 0::0 0::0===0                          |

## 5.3 Signal Specifications

This section describes the electrical and timing characteristics of the input and output signals for digital output and control of the Model 8100.

## 5.3.1 Inputs

The inputs comprise 16 input data connections (B0 through B15) and one control line (CMD). Each of these lines accepts standard TTL digital signals (2.4 to 5.0 V high, 0 to 0.4 V low) and presents a load approximating that of one and one-half TTL gates, i.e. each input line requires a nominal current sink of 2 mA to input a "low". The inputs can be positive or negative true (Pos or Neg Logic), depending upon the ground-strapping of the appropriate pins in the Logic Definition Field (pins 19 and 23, see 5.33 below.)

## 5.3.2 Outputs

The outputs comprise eight output data connections (D0 through D7) and one control line (FLG). The FLG output is a supervisory data exchange bit used in conjunction with the CMD input. The output data lines are only active when the unit is correctly "addressed". That is, the outputs do not present any signal nor place any load on the output lines unless the address code on the input address lines (B13, B14, B15) corresponds to the code as programmed on the address definition pins in the Logic Definition Field (20, 21 and 22). Each of the output lines is capable of driving up to 30 standard TTL loads (maximum fan-out = 30). The outputs will be positive or negative true (Pos or Neg logic), depending upon the connections in the Logic Definition Field (pins 24 and 25, see below).

## 5.3.3 Logic Definition Field Connections

The Logic Definition Field of pins in the interface allows the user to define the "polarity" or "sense" of the digital input and output lines, and to define the "address" to be assigned to the unit for digital control. Each sub-field of digital information bits (lines) can be independently assigned to be positive or negative true (Pos or Neg logic).

Positive true is defined to be the representation of a binary "one" by a positive (high) signal and the representation of a binary "zero" by a zero (low) signal. Conversely, negative true or negative logic is defined to be the representation of a binary "one" by a zero (low) signal and the representation of a binary "zero" by a positive (high) signal.

Positive true or positive logic signals are defined for a selected group of data bits by leaving the appropriate pin in the Logic Definition Field open-circuited. Conversely, negative logic will be defined by connecting the appropriate pin to ground. For example, negative logic inputs will be accepted on the B0 through B12 inputs providing that pin 19 is connected to ground.

Similarly, the "address" that will be required in order to input digital control information to the unit is defined by appropriate ground connections. For each "address" input bit that is to be recognized as "high", the corresponding address definition pin in the Logic Definition Field should be left open-circuited. Conversely, each "address" input bit that is to be recognized as "low" must have its corresponding address definition pin grounded. For instance, if the desired address of the unit is to be "101" (assuming a positive logic convention), the address definition pin number 21 should be connected to ground denoting the "0" or low signal is to be recognized and pins 20 and 22 should be left disconnected. Note that positive or negative logic convention for the address is purely a matter of the definition of the convention used in describing the connections to the Logic Definition Field in terms of the logic to be used. Thus, if all three pins in the Logic Definition Field are left ungrounded (open), this defines an address of "lll" using the positive logic definition and "000" when the negative logic definition is used.

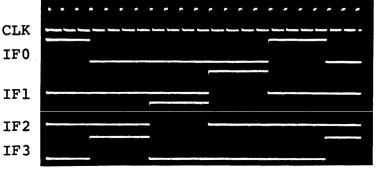

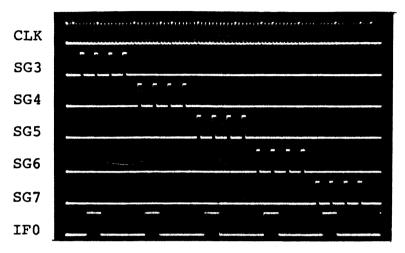

## 5.3.4 Control Timing

All digital inputs and outputs from the Model 8100 are regulated by two control signals: the output flag (FLG) signal and the input command CMD) signal. The FLG output signal indicates the output data status of the Model 8100 and acknowledges the acceptance of input data. The CMD input signal initiates the input data function. This is sometimes referred to as "data request-request honored" data exchange control.

In the following discussion, defining the FLG and CMD signals and their interrelationships, binary logic notation will be used, i.e. binary 0 (zero) and 1 (one) will be used to define the signals. The representation of these binary values as positive (high) or low electrical signals will be dependent upon the logic definitions on the appropriate pins in the Logic Definition Field (see discussion above).

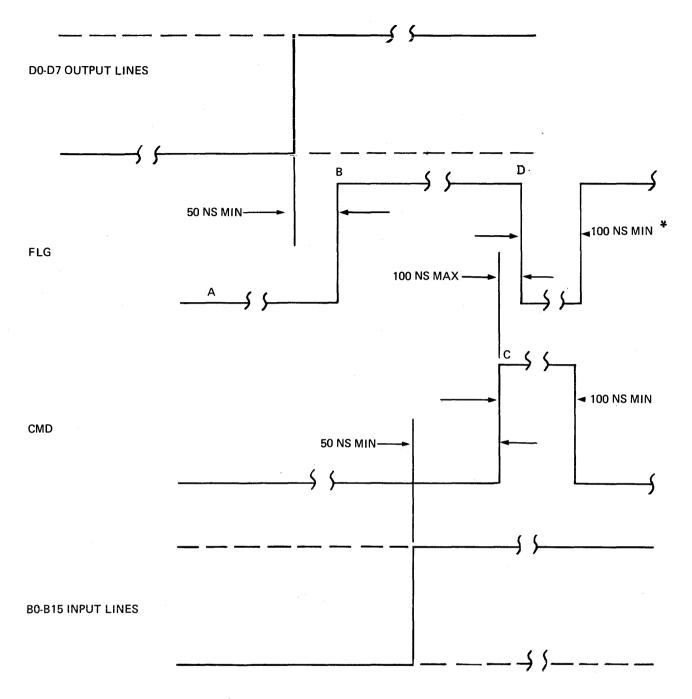

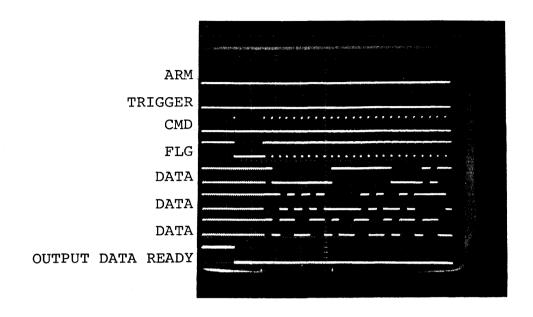

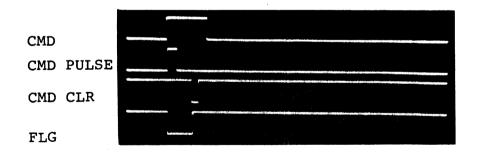

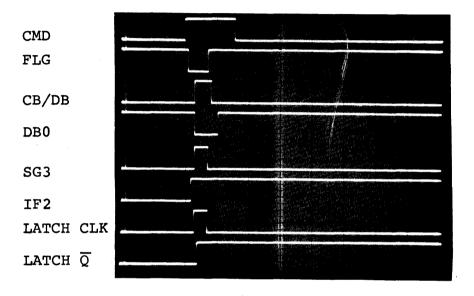

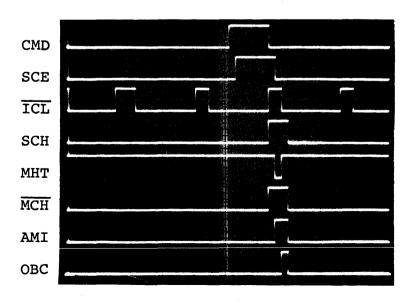

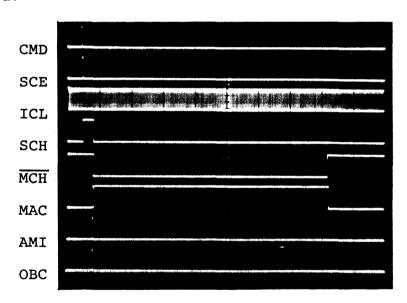

The timing and transitions for the FLG and CMD signals as well as their interrelationships and timing with respect to the input and output data are described in the following subparagraphs and the Data Exchange Timing Diagram, (Fig. 5.1).

- A. CMD signals not accepted when FLG is low.

- B. Record or previous instruction completed, ready for next instruction.

- C. Causes 8100 to execute the input (B0-B15) instruction and/or fetch the new (next) data output (D0-D7) word. Assumes that present 8100 data output has been read and/or a new data input word is ready.

- D. CMD accepted, 8100 busy.

\*Note: Nominal FLG width is 200 to 250 nanoseconds. Last FLG (2048th) in AUTO output mode is 100ns wide. Also the FLG low time may be as much as 1 millisec (latency) when data output interval exceeds  $100\,\mu sec.$

Figure 5.1 Data Exchange Timing Diagram

# 5.3.4.1 FLG level 1

When the FLG signal is a binary 1, a CMD can be input (0 to 1 transition) and it will be accepted and the input data instruction will be executed.

## 5.3.4.2 FLG 1 to 0 transition

The 1 to 0 transition of the FLG signal denotes that the CMD input has been accepted. The CMD signal may be returned to 0 (subject to a minimum "dwell" time of 100 nsec, see 5.346 below).

## 5.3.4.3 FIG level 0

When the FLG signal is a binary 0, the unit is "busy" and no command signals (CMD 0 to 1 transitions) or input data instructions will be accepted.

# 5.3.4.4 FLG 0 to 1 transition

The 0 to 1 transition of the FLG signal denotes that the input data instruction has been executed and that the unit is ready for another command. Any output data as a result of the input instruction is applied to the output data lines 50 nsec prior to this transition and the output data will be held as long as the input instruction data (which enables or "gates" the appropriate output data) is maintained and the next CMD (0 to 1 transition) has not occurred. If no output data is required, the input data may be changed. The CMD signal may be held at a binary 1 or it may be returned to 0 during this period with no effect on the output data.

## 5.3.4.5 CMD 0 to 1 transition

Causes the action or instruction defined by the input data to be executed (or initiates the specified action). The input data should be applied at least 50 nsec prior to the CMD transition and the data should be held until the resulting FLG 0 to 1 transition and until the resulting output data (if appropriate) has been received and stored by the digital controller.

# 5.3.4.6 Minimum pulse width

The minimum "dwell" time in either the binary 1 or 0 state for the CMD signal is 100 nsec. Narrower pulse width may result in failure of the unit to recognize the signal. Similarly, the FLG output signal will not be produced with binary 1 or 0 pulses of less than 100 nsec duration.

## 5.3.5 Output Data Rates

The signal data in the memory of the Model 8100 can be output asynchronously at rates up to 2 x  $10^6$  words/sec under the control of the Flag and Command signals. The output rate is influenced by the internal clock frequency and the need to refresh the memory between output words at low read rates. The former is evidenced by a 0.5 µsec latency in the output with respect to a 2 MHz synchronous clock. This latency does not reduce the average data rate of the unit but it does cause a cyclic "grouping" of the data which is particularly noticable at rates near the maximum rate of 2 x  $10^6$  words/sec. For instance, at an average output rate of 1.5 x  $10^6$  words/sec, the words would be spaced in time by alternating periods of 0.5 µsec and 1.0 µsec.

As the digital memory in the Model 8100 is made up of MOS shift registers, the memory must be cycled periodically in order to prevent loss of data. Thus, protective circuitry is provided in the unit to detect the need for cycling the memory and cause this to occur during the digital output whenever the output rate is low. During the time that the memory is being cycled, no additional output data is available. This leads to an output latency of up to the full memory cycle time (1 ms) whenever the output rate is at or below 10 KHz. This phenomenon is evidenced as follows: Average data rates are continuous from 1 x 10 to 2 x  $10^6$  words/sec. Data rates less than 1 x  $10^4$  words/sec will exhibit up to 1.0 ms latency, i.e., if more than 100 µsec. occurs between data request commands, delays of up to 1.0 ms will occur between output data words.

### 5.3.6 Cable Parameter Compensation

The Model 8100 is designed to facilitate rapid digital data transfer. For cable lengths up to about six feet between the Model 8100 and the digital controlling device, no special shielding, terminations or compensation is required on the data input or output lines. Any reflected signals, ringing and/or cross-coupling will normally be attenuated and "settled out" well within the 50 nsec settling time delay between the output data and the FLG signal or during the 50 nsec delay (specified above) between the input data word presentation and the CMD "zero" to "one" transition.

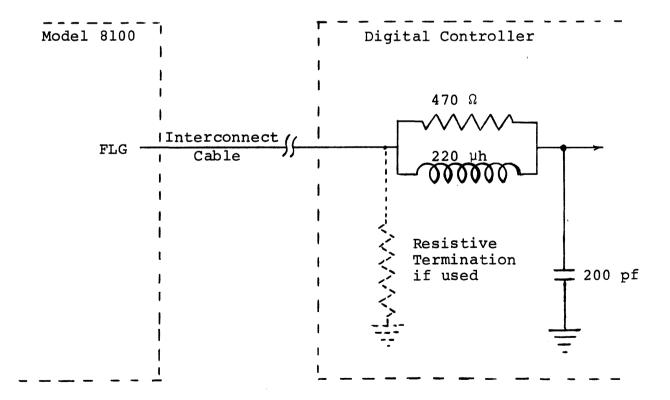

The FLG and CMD signals do, however, require some confiderations in order to insure immunity from line ringing and/or cross-talk phenomenon. For these reasons, the Command input to the unit incorporates a line filter which effectively prevents false or multiple signals due to cross-talk.

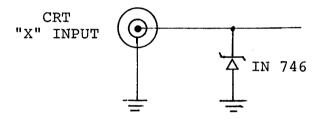

Similarly, it is recommended that a simple filter be utilized on the Flag signal at the cable termination on the digital controller. The circuit shown in the following sketch has been found to be particularly effective for this use.

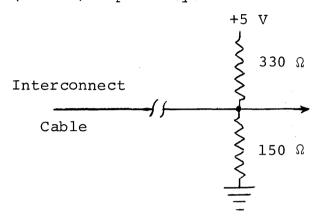

Cable lengths in excess of about six feet may require special considerations in order to insure error-free data transfer at high data rates. This is most easily accomplished by terminating the signal lines (twisted pairs) with 100 ohms.

The following recommended biased load network may be connected to each output line at the load end of the cable to provide a 100 ohm termination while preserving full far -out (30 TTL) capability.

The inputs on the digital input lines of the Model 8100 provide high impedances so that long cable lengths with data transfer rates near the maximum possible may require input line terminations. In these instances, the above network is recommended on each data input line at the digital interface connector of the unit (+5 V is provided on pin 34).

#### 5.3.7 Memory Data Output Code

When the data in the digital memory of the Model 8100 is transferred to the digital output (under control of the FLG signal and input signals), it is output in a binary code called "2's (two's) complement". This code is particularly useful and convenient for representing values which may range over positive and negative scales. Such is the case in the Model 8100. The value represented by each word in the memory represents an instantaneous voltage level of the input signal and the input signal may be any value between plus and minus the fullscale selected on the input attenuator (depending on the amount of input offset selected).

The "2's complement" binary code is arranged such that 00000000 is at midscale representing zero input volts (with no input offset). All positive values are scaled directly with pure binary digit weighting and a resolution of 1 in 128 (the most significant bit is always zero for positive polarity input values). All negative values are coded such that the most significant bit is always "one" and the absolute magnitude is obtained by complementing the binary number (changing all 1's to 0's and vice-versa) and adding a binary "1". This results in an output code that is very convenient and efficient for computation and/or analysis by a digital computer.

The following table presents representative examples of the "2's complement" output code.

|                     | 2's<br>Complement    | Decimal<br>Value | Equiv. Volts (+1 V Scale) |

|---------------------|----------------------|------------------|---------------------------|

| Positive Full Scale | 01111111<br>01111110 | +127<br>+126     | +0.992<br>+0.984          |

|                     | 01111101             | +125             | +0.976                    |

| Positive Half Scale | 01000000             | +64              | +0.500                    |

|                     | •                    |                  |                           |

|                     | 00000011<br>00000010 | +3<br>+2         | +0.023<br>+0.016          |

| Positive One Count  | 00000001             | +1               | +0.008                    |

| Zero                | 00000000             | 0                | 0.000                     |

| Negative One Count  | 11111111<br>11111110 | -1<br>-2         | -0.008<br>-0.016          |

|                     | 11111101             | -3               | -0.023                    |

|                     | •                    |                  |                           |

| Negative Half Scale | 11000000             | -64              | -0.500                    |

|                     | •                    |                  |                           |

|                     | 10000010<br>10000001 | -126<br>-127     | -0.984<br>-0.992          |

| Negative Full Scale | 10000000             | -128             | -1.000                    |

The decimal value in the above table is obtained by direct binary to decimal conversion for all positive values and by converting the negative values as described above and then conducting the binary to decimal conversion. The equivalent voltage is obtained by multiplying the ratio of the decimal value to 128 (the full scale count) by the full scale voltage. For instance, the negative half scale voltage is  $-64/128 \times 1.0 \text{ V} = -0.5 \text{ V}$  for a full scale voltage range of  $\pm 1 \text{ V}$ .

# 5.4 Data Output Only Operation

The Model 8100 can be readily configured to output digital data without resorting to complete computer control. This type of operation is particularly useful when it is desired to simply transfer the digitized signal data in the memory of the unit to another device or memory. Examples of this application include output of the digital data to punched tape or directly into the storage cells of a signal averager. The procedures to accomplish this type of operation are described in this section.

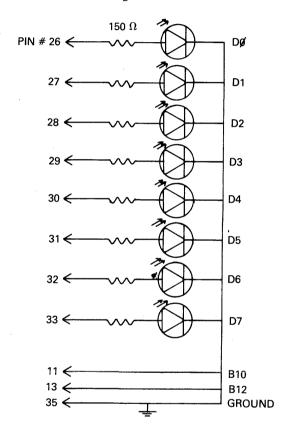

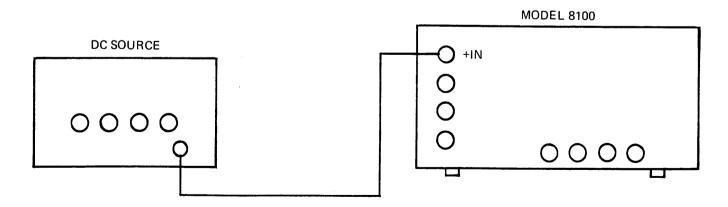

The connection of a few jumpers on the mating connector for the digital control interface (J1) will configure the Model 8100 to output the digital data under simple strobe type control. These jumpers should be connected as follows:

- (a) Connect jumper connections between pins 11, 13 and ground (pins 35-50).

- (b) Determine whether positive or negative logic is to be defined for the digital output, the FLG output and the CMD input and add the appropriate jumpers (if any) as described above for the Logic Definition Field connections (see 5.33). CAUTION:

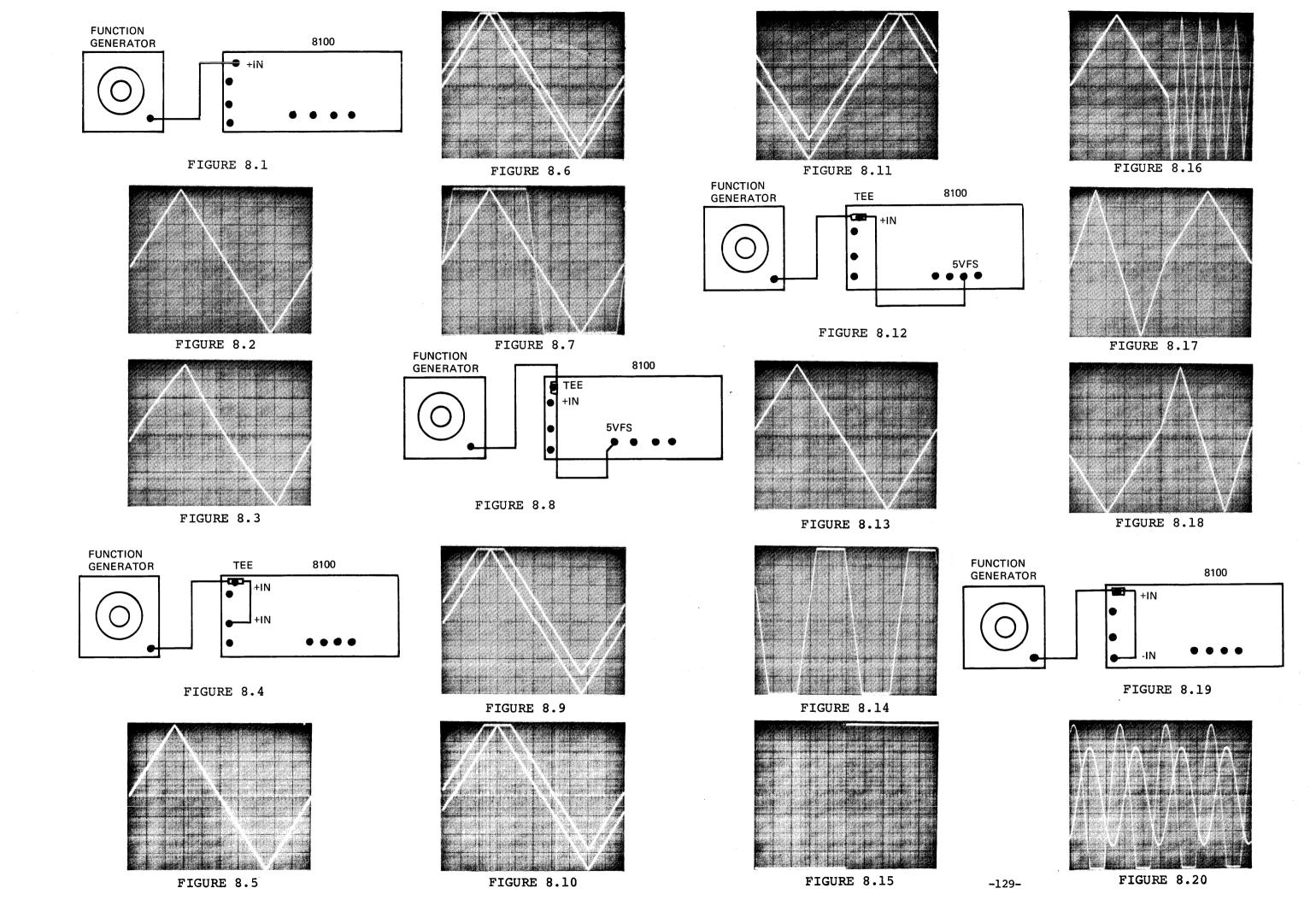

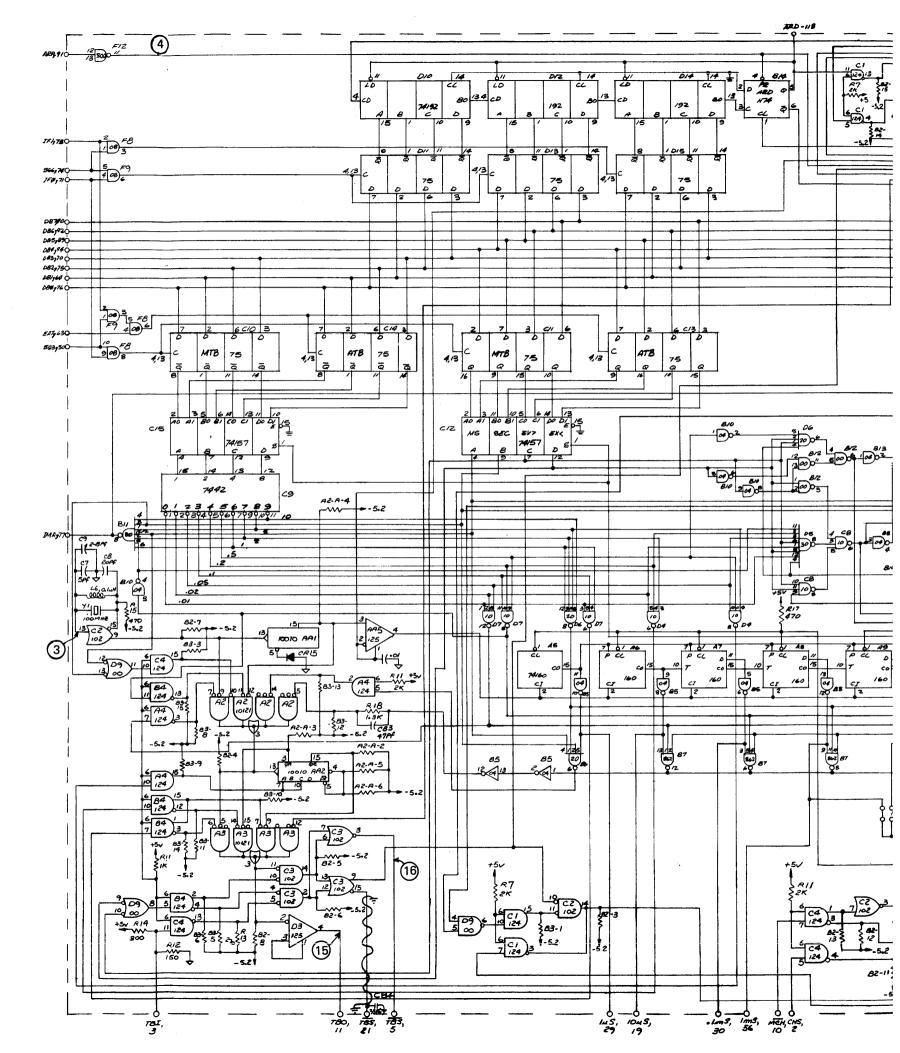

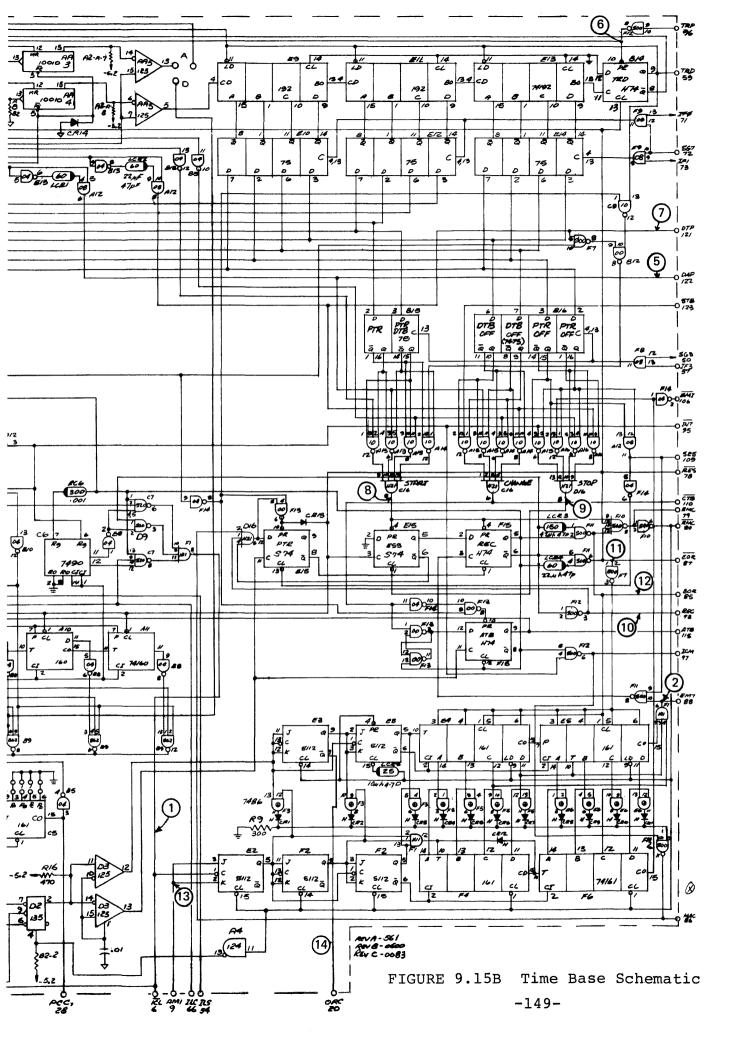

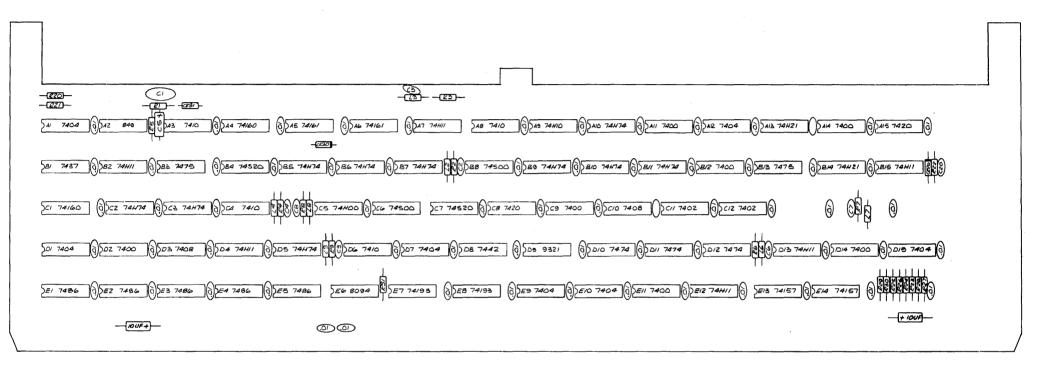

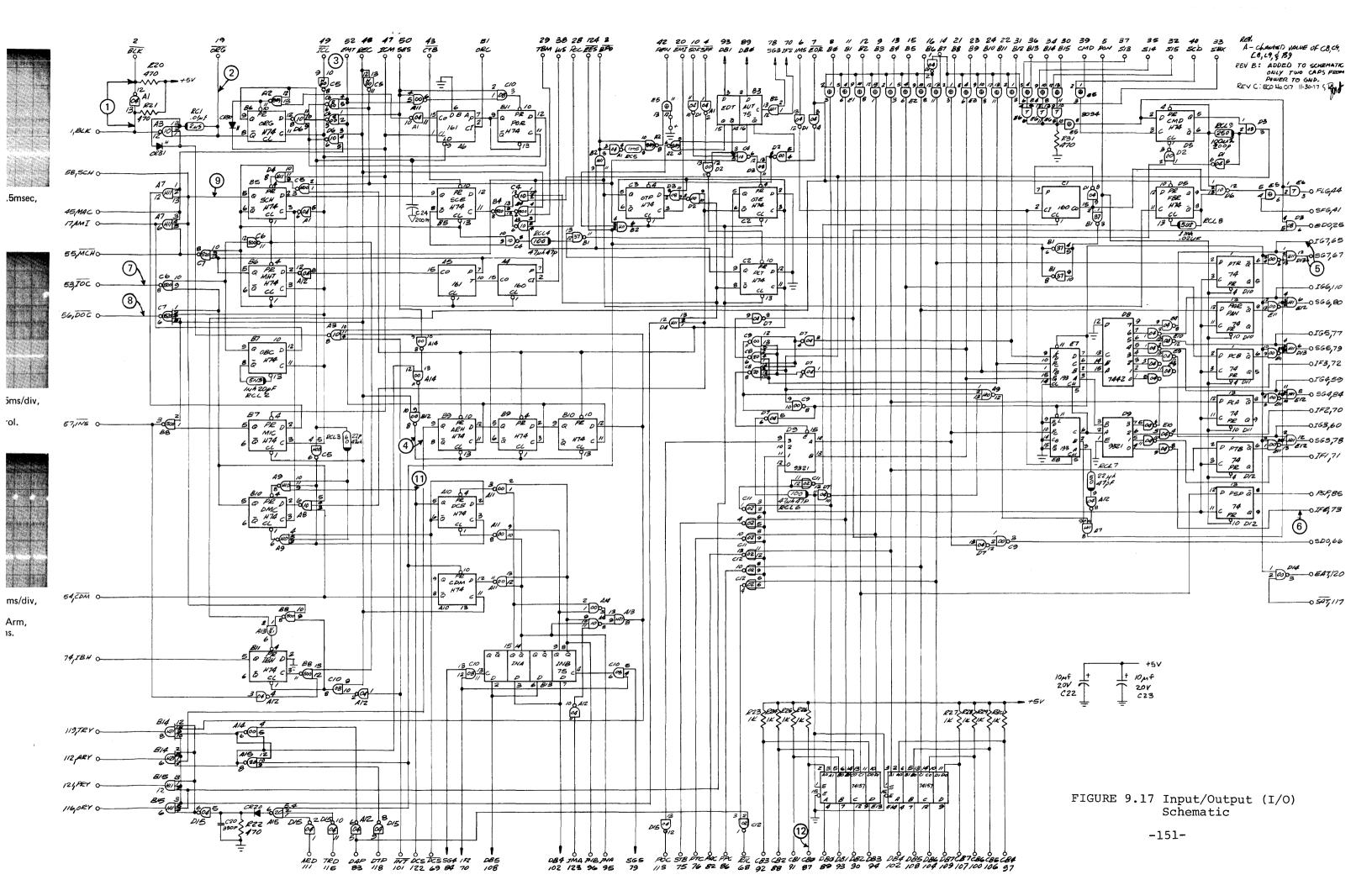

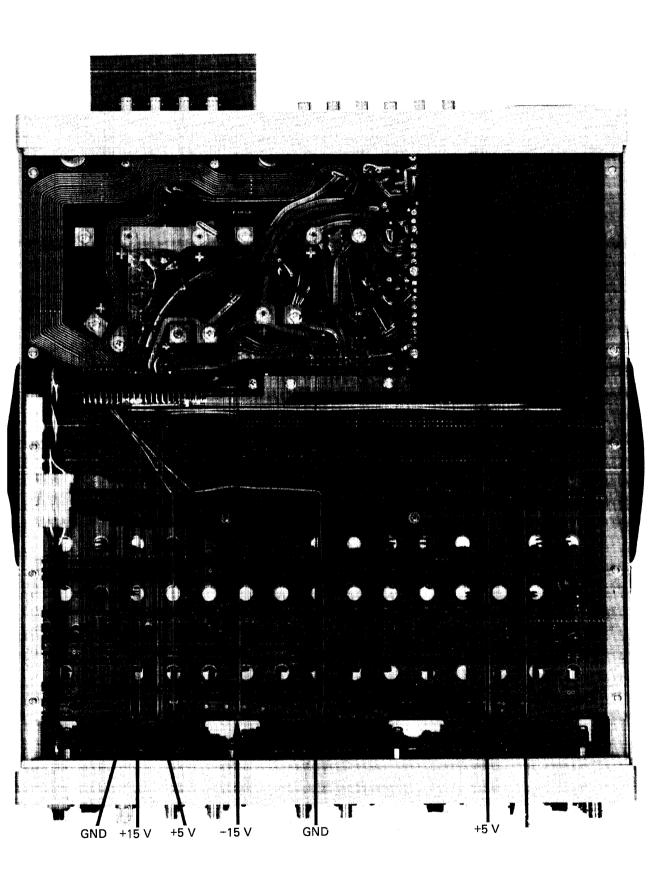

do not connect the Logic Definition Field to define negative logic for the data inputs (BO to BI5) as this will negate the jumpers in (a) above. In other words, pin 19 must be left open-circuited.