### Schematic Entry User Manual

# SYNARIO

Universal FPGA Design System

Synario is a Data I/O Product

August 1994 090-0602-001

Data I/O has made every attempt to ensure that the information in this document is accurate and complete. Data I/O assumes no liability for errors, or for any incidental, consequential, indirect or special damages, including, without limitation, loss of use, loss or alteration of data, delays, or lost profits or savings, arising from the use of this document or the product which it accompanies.

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose without written permission from Data  $\rm I/O$ .

Data I/O Corporation 10525 Willows Road N.E., P.O. Box 97046 Redmond, Washington 98073-9746 USA (206) 881-6444

Acknowledgments:

Data I/O is a registered trademark and Synario and ABEL-HDL are trademarks of Data I/O Corporation.

Data I/O Corporation acknowledges the trademarks of other organizations for their respective products or services mentioned in this document.

© 1994 Data I/O Corporation All rights reserved

### **Table of Contents**

### **Preface**

| Using This Manual                                                    | ii |

|----------------------------------------------------------------------|----|

| Synario Capture System Basics (Chapters 2 and 3) xi                  | ii |

| How to Use the Synario Capture System (Chapter 4 through Appendix B) | ii |

| Other Documents xi                                                   | ίi |

| Chapter Contents xi                                                  | V  |

| SCS Components                                                       | ⁄i |

| Getting Started                                                      |    |

| If You're a Current ECS User                                         | 1  |

| Installing SCS                                                       | 1  |

| Windows Installation                                                 | 1  |

| UNIX Installation                                                    | 7  |

| Inside SCS                                                           |    |

| Symbols                                                              | 1  |

| Symbol Libraries                                                     | 1  |

| What Does a Symbol Consist Of? 2-                                    | 2  |

| Attributes                                                           | 3  |

| Attribute Types                                                      | 4  |

| Attribute Components 2-                                              | 4  |

| Creating New Attributes 2-                                           | 5  |

| Schematic Elements                         |   | <br> |  | <br>           | 2-5 |

|--------------------------------------------|---|------|--|----------------|-----|

| Symbols                                    |   |      |  |                | 2-6 |

| Wires                                      |   |      |  |                | 2-7 |

| I/O Markers                                |   |      |  |                | 2-8 |

| Graphics                                   |   | <br> |  | <br>           | 2-8 |

| Text                                       |   |      |  |                | 2-8 |

| Schematics Relation to Netlists            |   |      |  |                | 2-9 |

| Using Netlists                             | • | <br> |  | <br>. <b>.</b> | 2-9 |

| 3. Introduction to Hierarchical Design     |   |      |  |                |     |

| What Is a Hierarchy?                       |   |      |  |                | 3-1 |

| Advantages of Hierarchical Design          |   |      |  | <br>           | 3-2 |

| Approaches to Hierarchical Design          |   |      |  |                | 3-2 |

| Top-Down Design                            |   | <br> |  | <br>           | 3-3 |

| Bottom-Up Design                           |   |      |  |                | 3-3 |

| Inside-Out ("Mixed") Design                |   | <br> |  |                | 3-3 |

| What is Hierarchical Organization?         |   |      |  | <br>           | 3-4 |

| Symbols, Schematics, and Hierarchy         |   |      |  |                | 3-4 |

| Hierarchical Design Structure              |   |      |  |                | 3-5 |

| Hierarchical Naming                        |   |      |  |                | 3-6 |

| Nets in the Hierarchy                      |   |      |  |                | 3-7 |

| Automatic Aliasing of Nets                 |   |      |  |                | 3-8 |

| 4. Basic Operation                         |   |      |  |                |     |

| What SCS Can Do                            |   |      |  |                | 4-1 |

| SCS Programs                               |   | <br> |  |                | 4-3 |

| Using the SCS Executive                    |   | <br> |  | <br>           | 4-4 |

| Running the Editors or Hierarchy Navigator |   |      |  |                | 4-4 |

| Editing Files                              | • |      |  | <br>           | 4-4 |

| Schematic Exchange/Conversion Utilities    |   | <br> |  | <br>           | 4-5 |

| Setup Utilities                            |   |      |  |                | 4-5 |

| Customizing the Executive with the pcshell.ini Fi | le . |   | <br> |   |      | 4-6  |

|---------------------------------------------------|------|---|------|---|------|------|

| pcshell.ini Format                                |      |   |      |   |      | 4-7  |

| The SCS Executive Command Line                    |      | • |      |   |      | 4-9  |

| SCS Command Structure                             |      |   | <br> |   |      | 4-10 |

| Using the Mouse                                   |      |   |      |   |      | 4-10 |

| Right Mouse Button Functions                      |      |   |      |   |      | 4-11 |

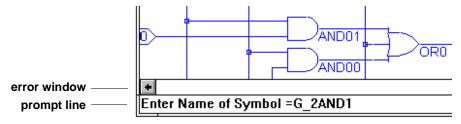

| Prompting and Error Messages                      |      |   | <br> |   |      | 4-11 |

| Error Recovery                                    |      |   |      |   |      | 4-12 |

| Network Operation                                 |      |   | <br> |   |      | 4-12 |

| Naming Design Files                               |      |   | <br> |   |      | 4-13 |

| Saving the Schematic or Symbol                    |      |   | <br> |   |      | 4-14 |

| Printing and Plotting                             |      |   | <br> |   |      | 4-14 |

| Windows                                           |      |   |      |   |      | 4-14 |

| UNIX/Motif                                        |      |   | <br> |   |      | 4-15 |

| The INI Editor                                    |      |   |      | • |      | 4-16 |

| 5. Using the Schematic Editor                     |      |   |      |   |      |      |

| Chapter Contents                                  |      |   | <br> |   |      | 5-1  |

| What Is a Schematic?                              |      |   |      |   |      | 5-2  |

| Schematic Sheets Versus Hierarchical Levels       |      |   |      |   | <br> | 5-3  |

| Schematic Components                              |      |   |      |   |      | 5-3  |

| Symbols                                           |      |   |      |   |      | 5-3  |

| Wires                                             |      |   |      |   |      | 5-3  |

| Attributes                                        |      |   | <br> |   |      | 5-4  |

| Graphics and Text                                 |      |   |      |   |      | 5-4  |

| Adding Schematic Elements                         |      |   |      |   |      | 5-5  |

| Selecting a Symbol                                |      |   |      |   |      | 5-5  |

| Placing the Symbol                                |      |   | <br> |   |      | 5-6  |

|                                                   |      | - |      |   |      |      |

| Wiring the Schematic                              |      |   |      |   |      | 5-9  |

| Drawing Wires                                     |      |   | <br> |   |      |      |

| Net Names                                    | 0 |

|----------------------------------------------|---|

| Entering Net Names                           | 1 |

| Placing the Net Name                         | 1 |

| Renaming a Net                               | 3 |

| Specifying Signal Direction                  | 3 |

| Buses                                        | 4 |

| Bus Pins                                     | 7 |

| Wiring Constraints                           | 9 |

| Modifying the Schematic                      | 0 |

| Clipboard Commands                           | 0 |

| Non-Clipboard Commands                       | 0 |

| Debugging and Verifying a Schematic 5-2      | 1 |

| "Unconnected Pin" Message                    | 2 |

| Schematic Editor Display Options             | 3 |

| Schematic Sheets                             | 3 |

| Grids                                        | 4 |

| Controlling Display and Graphics Options 5-2 | 4 |

| Setting Attribute Values                     | 6 |

| Pin Attributes                               | 6 |

| Symbol Attributes                            | 6 |

| Net Attributes                               | 7 |

| Attribute Windows                            | 8 |

| 6. Using the Symbol Editor                   |   |

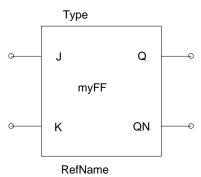

| Symbol Components                            | 2 |

| Graphics                                     | 2 |

| Pins                                         | 2 |

| Attributes                                   | 2 |

| Symbol Types                                 | 2 |

| Component and Gate Symbols 6-                | 3 |

| Cell Symbols 6-                              | 3 |

| Block Symbols                                       | 3 |

|-----------------------------------------------------|---|

| Pin Symbols                                         | 3 |

| Graphic Symbols                                     | 4 |

| Master Symbols                                      | 4 |

| Creating Symbols                                    | 4 |

| Starting the Symbol Editor 6-                       | 5 |

| Grids                                               | 5 |

| Drawing Graphics and Fixed Text 6-                  | 6 |

| Saving a Symbol                                     | 8 |

| Printing the Symbol                                 | 8 |

| Editing Symbols                                     | 8 |

| Preparing Symbols for Schematics 6-                 | 9 |

| Pins                                                | 9 |

| Bus Pins                                            | 1 |

| Attributes                                          | 2 |

| Checking Symbols                                    | 4 |

| "Unconnected Pin" Message 6-1                       | 5 |

| Creating Block Symbols in the Schematic Editor 6-1: | 5 |

| Making a Block Symbol for the Loaded Schematic 6-10 | 6 |

| 7. Using the Hierarchy Navigator                    |   |

| Hierarchy Navigator Functions                       | 2 |

| Navigating a Design                                 | 2 |

| Updating Schematics                                 | 3 |

| Push/Pop                                            | 3 |

| Tracing Signals                                     | 4 |

| Mark                                                | 4 |

| Query                                               | 4 |

| Setting and Overriding Attributes                   | 6 |

| Pin Attributes                                      | 6 |

| Symbol Attributes                                   | 7 |

| Net Attributes                                       | 7 |

|------------------------------------------------------|---|

| Attribute Windows                                    | 7 |

| Additional Hierarchy Navigator Features              | 8 |

| Analysis Tools                                       | 0 |

| ERC and PCB Checkers                                 | 1 |

| Types of Analysis Performed by the Checkers 7-1      | 4 |

| Operating the Electrical Rules Checker 7-1           | 5 |

| Operating the PCB Checker                            | 8 |

| The View Report Utility                              | 9 |

| Viewing Critical Paths                               | 0 |

| Netlists and Interfaces                              | 1 |

| The Packager                                         | 2 |

| O A44#!bastag                                        |   |

| 8. Attributes                                        |   |

| Attribute Functions                                  | 1 |

| Attribute Types                                      | 2 |

| Attribute Components                                 | 2 |

| Attribute Name                                       | 2 |

| Attribute Number                                     | 2 |

| Attribute Value                                      | 3 |

| Attribute Modifier                                   | 3 |

| Attribute Window                                     | 3 |

| Modifying Attributes                                 | 4 |

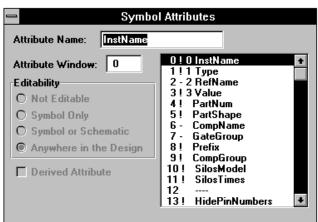

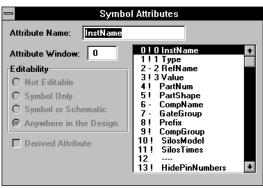

| Symbol Attributes                                    | 4 |

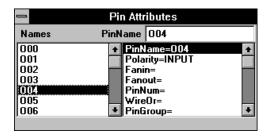

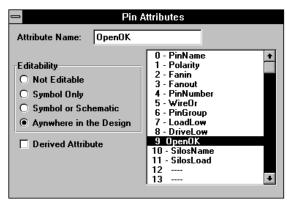

| Pin Attributes                                       | 4 |

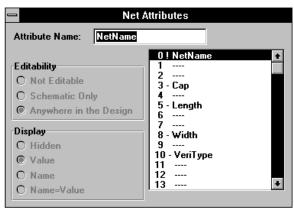

| Net Attributes                                       | 4 |

| Creating New Attributes                              | 4 |

| Attribute Names                                      | 6 |

| Attribute Modifiers                                  | 7 |

| Assigning Values to Simple Attributes 8-             | 8 |

| Changing Attribute Values in the Schematic Editor 8- | 9 |

| Removing Attributes from a Netlist 8-9         |

|------------------------------------------------|

| Displaying Attribute Values on a Schematic 8-9 |

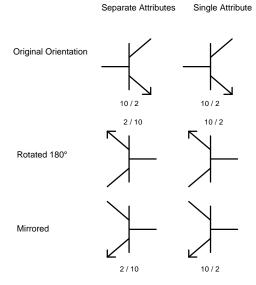

| Reassigning Attribute Windows 8-9              |

| Number Notation in Attributes                  |

| Derived Attributes                             |

| Example of Derived Attributes 8-18             |

| 9. The SCS INI Editor                          |

| The binary.ini File                            |

| Custom INI Files                               |

| INI Editor Menus                               |

| Controls Menu                                  |

| System Controls                                |

| Display Controls                               |

| Symbol Controls                                |

| Graphic Options                                |

| Sheet Layout                                   |

| Sheet Sizes                                    |

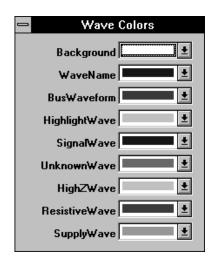

| Wave Controls                                  |

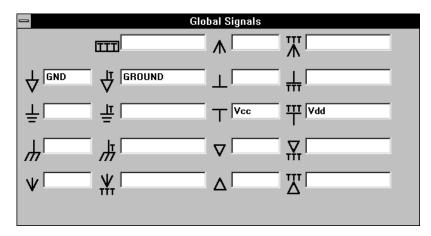

| Global Nets                                    |

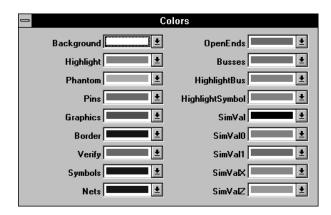

| Colors                                         |

| Wave Colors                                    |

| Print Controls                                 |

| Tools Menu                                     |

| Symbol Tools                                   |

| Schematic Tools                                |

| Navigator Tools                                |

| Navigator Processes                            |

| Attributes Menu                                |

| Symbol, Pin, and Net Attributes                |

| Evample Attributes 0.29                        |

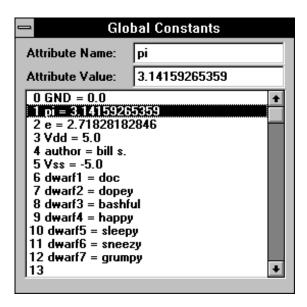

| Global Attributes                        | 0 |

|------------------------------------------|---|

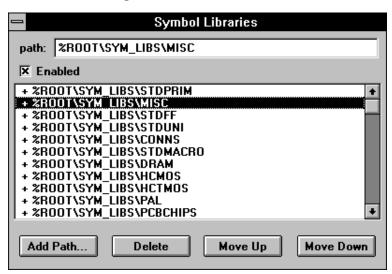

| Search Paths Menu9-3                     | 1 |

| Project, Model, and Symbol Libraries     | 1 |

| Libraries and Directory Structures       | 3 |

| Program Directories                      | 4 |

| User Directories                         | 4 |

| Library Directories                      | 4 |

| 10. PCB Design Considerations            |   |

| Configuring for PCB Design               | 1 |

| Differences between IC and PCB Design    | 2 |

| PCB Attributes                           | 2 |

| Symbol Attributes                        | 2 |

| Pin Attributes                           | 4 |

| Symbol Types                             | 5 |

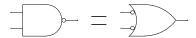

| DeMorgan-Equivalent Gates                | 6 |

| Instance Names and Reference Designators | 6 |

| Reference Designators                    | 6 |

| Instance Names                           | 7 |

| Assigning Reference Designators          | 8 |

| Gate Assignment                          | 0 |

| Pin Swapping                             | 1 |

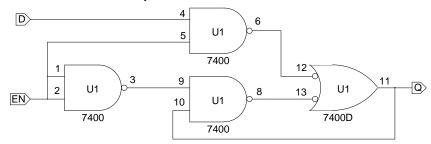

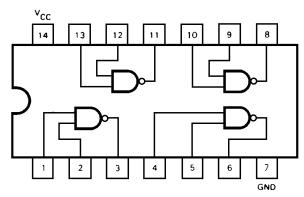

| Example PCB Design                       | 2 |

| System Configuration                     | 2 |

| Creating a Gate Symbol                   | 2 |

| Create the Latch Schematic               | 4 |

| Auto Packaging of PCB Devices            | 5 |

| Configuration Information                | 6 |

| Query Packaging                          | 6 |

| Check Packaging                          | 7 |

| Clear Packaging                          | 8 |

| Auto Package                           | 10-18 |

|----------------------------------------|-------|

| Reference Designator                   | 10-19 |

| Pin Number                             | 10-20 |

| PCB Back Annotation Interfaces         | 10-21 |

| The Back Annotation Programs           | 10-21 |

| PADS PCB-specific Features             | 10-23 |

| RINF-specific Features                 | 10-24 |

| PCB Netlisters                         | 10-25 |

| Features Common to All PCB Netlisters  | 10-26 |

| Attributes Needed for Netlisting       | 10-26 |

| Preparing Schematics                   | 10-28 |

| PCB Power Pins                         | 10-28 |

| View Report Facility                   | 10-30 |

| Error Messages                         | 10-30 |

| PADS PCB-specific Features             | 10-31 |

|                                        | 10-32 |

|                                        | 10-32 |

| CADNETIX-specific Features             | 10-32 |

|                                        | 10-33 |

|                                        | 10-33 |

|                                        | 10-33 |

| Non-Homogeneous Gates Example          | 10-34 |

| _                                      | 10-35 |

|                                        | 10-35 |

|                                        | 10-36 |

| ASCII Netlist Format                   | 10-36 |

| The Packlist Bill-of-Materials Program | 10-42 |

|                                        | 10-42 |

|                                        | 10-43 |

|                                        | 10 /2 |

### **Appendixes**

| A. | Generic Interfaces           |

|----|------------------------------|

|    | Archive Utility              |

|    | ASCII Interface              |

|    | EDIF Interfaces              |

|    | Generic Netlists             |

| В. | Simulator Interfaces         |

|    | SILOS                        |

|    | Timewave History File Format |

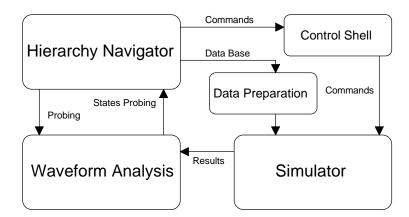

|    | Simulation Environment       |

|    | SPICE                        |

|    | SPICE Format Conversions     |

|    | Timemill                     |

|    | Verilog                      |

|    | VHDL Interface               |

|    | Exporting the Stimulus File  |

### Index

### **Preface**

This manual describes the *Synario Capture System™* (SCS™). It is divided into two sections. The first section presents the "what" of SCS, the last section the "how." You don't have to read the first section in order to use SCS. However, it has background information that should increase your understanding of SCS's features and let you take fuller advantage of them. Chapter 4, "Basic Operation," explains how to configure SCS.

### **Using This Manual**

### Synario Capture System Basics (Chapters 2 and 3)

This section gives a basic explanation of how SCS organizes symbol, schematic, and netlist files, and the ways in which SCS manages your designs as you enter them.

### How to Use the Synario Capture System (Chapter 4 through Appendix B)

This section explains how to use the various Capture System components: the Symbol and Schematic Editors, the Hierarchy Navigator, the INI Editor, and the netlister programs.

### Other Documents

See the *SCS Command Reference* for information on all commands available in the Schematic Editor, Symbol Editor and Hierarchy Navigator.

See the *Waveform Tools Manual* for information on the Waveform Viewer or Waveform Editor.

### **Chapter Contents**

The following is a brief outline of the contents of each chapter.

### **Chapter 1, Getting Started**

Explains how to install and license the SCS software for SCS (Windows) and ECS (Unix) product. If you have Synario, SCS is installed during Synario installation.

### Chapter 2, Inside SCS

Explains what an SCS symbol is, and how its characteristics and behavior are controlled by attributes. Describes the components that make up an SCS schematic and how they relate to netlists.

### **Chapter 3, Introduction to Hierarchical Design**

Shows how SCS schematics can be combined into a hierarchical structure, and describes the advantages of hierarchical design. Three approaches to hierarchical design are explained. Also describes the principles of hierarchical organization used in the Schematic Editor and Hierarchy Navigator.

### **Chapter 4, Basic Operation**

Discusses the interface and common features of the Schematic and Symbol Editors. Also explains how to configure SCS Executive program and explains the principal features of SCS.

### Chapter 5, Using the Schematic Editor

Covers most of what you need to know to add symbols and wiring to a schematic. Explains what nets and buses are, how to create them, and how to name them.

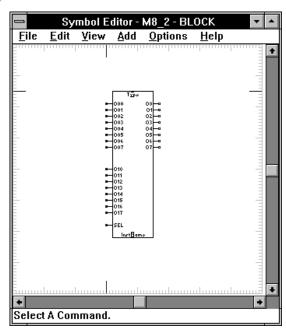

### Chapter 6, The Symbol Editor

Shows how to create your own symbols and attach attributes to them. Block symbols (symbols that represent modules or sub-circuits) are also described.

### **Chapter 7, Hierarchy Navigator**

Shows how to view and probe each level of a design using the Hierarchy Navigator. Explains the operation of the Electrical Rules Checker and the Critical Path Viewer.

### Chapter 8, Attributes

Explains what an attribute is, and how attributes are assigned to symbols, pins, and nets. Derived attributes, which permit dynamic modification of a design, are also described.

### Chapter 9, SCS INI Editor

Explains how the Schematic and Symbol Editors, Hierarchy Navigator, Waveform Viewer and Waveform Editor are configured by changing values and settings with the INI Editor.

### **Chapter 10, PCB Design Considerations**

Explains the differences between PCB and IC designs. Shows how to create netlist files in a variety of formats.

### **Appendix A, Generic Interfaces**

Describes the general-purpose interfaces that are most often used to move the design between systems.

### **Appendix B, Simulator Interfaces**

Describes the interfaces used to output the design to a simulator.

### **SCS Components**

This manual covers the following SCS/ECS components:

### **SCS Executive**

The Executive is a shell for SCS, usually used with the UNIX version, but available from Synario. You can run any of SCS components, as well as any additional design tools of your own choosing, by selecting them from the Executive.

### **Schematic Editor**

The Schematic Editor is SCS's schematic-capture tool. It creates schematic (.sch) files that can represent a complete design, or any component of a hierarchical design.

### **Symbol Editor**

SCS comes with a standard symbol library for IC or PCB design. The Symbol Editor is used to create symbols or primitive elements that represent an independent schematic module. You can also create decorative symbols (such as title blocks).

### **Hierarchy Navigator**

The Hierarchy Navigator combines all the components of a multi-level design for viewing and analysis. You can traverse the full design, viewing each component in its full hierarchical context.

### **INI Editor**

The INI Editor modifies SCS INI files, which control the appearance and behavior of SCS. Using the INI Editor, you can set your own preferences for how SCS environment looks and behaves. The INI Editor also manages attributes, which define the electrical behavior of symbols, pins, and nets.

### **Waveform Viewer**

The Waveform Viewer (optional with SCS/ECS standalone) is used to view the results of simulation. You can display the waveform of any net in your design. The Viewer is fully interactive with the Hierarchy Navigator; clicking on a net in the schematic automatically displays the waveform. Waveform Viewer operation is covered in the *Waveform Tools Manual*.

### **Waveform Editor**

The Waveform Editor (optional with SCS/ECS standalone) lets you create the stimulus waveforms for simulation graphically, by drawing directly on the screen. The stimuli can be edited graphically, or by modifying values in dialog boxes. The Editor then converts the waveforms into a stimulus file that your simulator recognizes. Waveform files are also useful as input to automatic test equipment, or as documentation of the circuit's expected behavior. Waveform Editor operation is covered in the *Waveform Tools Manual*.

### If You're a Current ECS User

If you're upgrading from a previous version of the Engineering Capture System (ECS), the Microsoft Write file **schnotes.wri** (in the Windows version) and the **schnotes** text file (in the UNIX/Motif version) has information about new and improved features, and anything you may need to take into account when working with existing projects under the new software. It also has any information that could not be included in the printed documentation.

### **Installing SCS**

The first part of this section covers Windows installation, the second UNIX/Motif installation.

**Note:** If you purchased SCS with Synario, SCS is installed during the base Synario installation. You do not need to install it separately.

### Windows Installation

### To install SCS or an SCS option:

- 1. Connect the SCS Security Device (or verify that it is connected).

- 2. Install the product software.

- 3. Create a Registration and Enable Code Request form.

- 4. Send the Registration and Enable Code Request form to Data I/O.

- 5. Enter the permanent Enable Codes after receiving them from Data I/O.

These steps are explained in the following sections.

### **Connecting the SCS Security Device**

On DOS/Windows machines, SCS products are licensed using a Security Device that attaches to your computer's parallel (Centronics) port and contains an identifier unique to your installation. In addition, each SCS product is individually licensed through its own Enable Code. SCS products can run only on computers that have the appropriate Security Device attached.

The Security Device comes with the SCS product.

### To connect the Security Device:

- Locate a parallel (Centronics) port on your computer. On a DOS machine, there may be more than one (LPT1:, LPT2:, LPT3:). SCS searches all the parallel ports, so you can connect the Security Device to any one of them. The Device does not have to be connected to the same port as the printer.

- 2. If you are connecting the Security Device to the same port as the printer, disconnect the printer cable.

- 3. Connect the male connector of the Security Device to the parallel port of your computer. Tighten the screws to firmly attach the Security Device.

- 4. If you disconnected your printer from this port, connect the printer cable to the female connector of the Security Device.

**Note:** If you have other security devices, add the Data I/O Security Device to the group. The Security Device for SCS does not replace any security devices you have for other Data I/O products.

If you have a Xilinx security device, it must be the farthest device from the computer. If you have the MAX/FLEX Device Kit or the MAX+plus II software, the MAX+plus II Software Guard must be the device closest to the computer.

**Note:** The Security Device works whether or not a printer is connected to it. However, on some computers, the printer must be turned on and be "on-line" while the program is running, or the Security Device will not be recognized. If you don't want the printer turned on all the time, you can put the Security Device and the printer on separate ports.

### Installing the SCS Software

### To install the software:

- 5. Insert Disk 1 into your disk drive.

- 6. From the Windows Program Manager, select Run from the File menu.

- 7. Enter

drive:setup

where *drive* is the letter of the disk drive in which you inserted the installation disk (A or B).

8. Follow the instructions on the screen. (They vary depending on which product is being installed.)

**Important!** The distribution disks include all Synario Capture Components, including options you may not have purchased. Do not install them if you are trying to maximize your free disk space.

**Note:** In general, you do not need to reboot your computer after installation. The installation program tells you if this is required.

### **User Notes and Comment Forms**

Important information about the product is placed in the installation directory during installation. These files are in Microsoft Write format (.wri) and can be found in the **readme** subdirectory of the installation directory.

The SCS **readme** file is installed as an icon in the Synario program group. This file contains last-minute release information and describes other files installed in the readme directory. Double-click on the icon to load it into Microsoft Write.

### Creating a Registration and Enable Code Request Form

You need to register your SCS products with Data I/O to obtain Enable Codes that permanently license your software. You use the Data I/O Registration Editor to register SCS products and enable a 30 day license while you wait for your permanent license codes. The Data I/O Registration Editor is installed as an icon labeled "Data I/O Registration" in the SCS program group.

You can install all the Synario products you purchased, then register them. You do not need to register them as they are installed.

### **Registering Your Synario Product**

All Synario Capture products are registered the same way, whether they come with your initial purchase, or you install them later:

- 1. Confirm that the Security Device is attached to the computer.

- 2. Select the "Data I/O Registration" icon from the program group. The Customer Information dialog box is displayed.

- 3. Click the down arrow in the Security Device combo box and highlight the Security Device Number you want to use. (There is normally only one number, unless you have more than one Data I/O Security Device connected to your computer.)

- 4. Enter the required information in the edit boxes (Name, Title, Company, and so on). All fields not marked "Optional" must be filled in. If you do not have a fax machine, type the word "None" in the Fax Number field.

The information you enter allows Data I/O to create the Enable Codes to permanently activate Synario products for your Security Device. The information also helps Data I/O provide better product support, timelier product information, and prompt information about upgrades and new releases.

**Note:** If your Shipping Address is different from your Mailing Address, be sure to enter it to ensure timely delivery of updates and upgrades.

**Note:** Be sure the information is complete and correct. If Data I/O needs to contact you for additional information, delivery of your permanent Enable Codes may be delayed.

- 5. When all required information has been entered, click the Licensing button. (If the button is not enabled, one or more required items are missing.)

- 6. The Product Information dialog box is displayed. The Product Description list box shows which products are currently installed (whether or not they are registered).

**Note:** If the installation directory is on a network and the directory is shared, products you have not purchased may be listed. However, without a Serial Number (described later) for those products, you cannot obtain the Enable Code for a Permanent license. You can, however, obtain a limited 30 Day license to evaluate those products.

- 7. Select the product to register. The fields in the Serial Number Card section change to match the Licensed Software title that appears on your Serial Number Card for that product.

- 8. Double-click on the product line or click the Enable button. The License Information dialog box appears.

- 9. Fill in the Serial Number field from the Serial Number Card included in your product documentation. This number is required by Data I/O to identify and verify the product that you purchased.

- 10. If you want to use the software immediately, select the 30 Day License from the License Type section and click the OK button.

**Note:** A 30 Day license can be used only once for each product with your Security Device: it cannot be renewed.

- 11. Repeat steps 7 through 10 until all Serial Numbers have been entered.

- 12. Some products require additional licensing information. When those products are selected from the product list, the Extended button is enabled. See the documentation for those products for instructions on the Extended License Information dialog box.

- 13. After registering all software, click the Close button to return to the Customer Information dialog box.

- 14. Click the Print button to print the Registration and Enable Code Request form.

- 15. Click the Close button to exit the Registration Editor.

### Sending the Registration Form to Data I/O for Processing

The Registration and Enable Code Request form contains all the information you entered into the Registration Editor. This form must be sent to Data I/O to obtain your Enable Codes. The methods are listed in order of increasing response time (that is, the first method is the fastest):

- Send the form by fax to the number at the top of the form. Data I/O returns your permanent Enable Codes to the fax number given in the Customer Information section.

- ◆ Call the telephone number at the top of the form during the hours listed with the form available. Data I/O will take the registration information over the phone and return your call with your permanent Enable Codes.

- Send the form by mail to the address at the top of the form. Data I/O will

process the form and return the permanent Enable Codes by return mail to

your Mailing Address.

### **Entering Permanent License Codes**

Once you receive your Enable Codes from Data I/O, enter them as follows:

- 1. Confirm that the Security Device is attached to the computer.

- 2. Run the Data I/O Registration Editor from the program group.

- 3. Select the Licensing button to display the Product Information dialog box.

- 4. Highlight the product you want to enable. Double-click on the product name or select the Enable button. The License Information dialog box is displayed.

- 5. Click the "Permanent License" radio button in the License Type section.

- 6. Enter the Enable Code in the Enable Code Entry field.

- 7. Click the OK button to exit the License Information dialog box and return to the Product Information dialog box.

**Note:** If the Enable Code does not match the other licensing information, you will receive a warning that the Enable Code is invalid. Return to the License Information dialog box and check that the Enable Code was entered correctly and for the correct product.

- 8. Repeat steps 4 through 7 until all Enable Codes have been entered. The Enable Code Status in the product list will change to Permanent. After all codes have been entered, select the Close button to return to the Customer Information dialog box.

- 9. Select the Close button to exit the Registration Editor.

### **UNIX Installation**

Follow these steps to install the Engineering Capture System:

1. Create a directory for ECS.

```

mkdir /usr/ecs

```

2. Make the new directory the working directory.

```

cd /usr/ecs

```

- 3. Insert the distribution tape in the tape drive.

- 4. Copy the contents of the tape with a command similar to the following example:

```

tar xv /dev/rst0

```

The following directories are created:

**bin** Motif executable files

data Help files and master ecs.ini file

examples Example circuitssym\_libs SCS symbol librariesmod libs SCS model libraries

**xfonts** Motif fonts

**license** SCS security files

5. Add the **bin** directory to your search path. You can make a temporary assignment with the following command:

```

set path=($path /usr/ecs/bin)

```

You can make the assignment permanent by setting the path in the .cshrc file.

6. Add the environment variable ECS\_ROOT pointing to the main directory:

```

setenv ECS_ROOT /usr/ecs

```

You can make the ROOT variable permanent by adding it to the .cshrc file.

7. The **license** directory contains the following files:

ImgrdLicense Manager daemondataioApplication Licensing daemon

8. Request a license from Data I/O. See the ECS User Notes.

When you receive your license codes, you should create a **license.dat** file in the /**usr/local/flexlm/licenses** directory on each machine that will be running ECS. If you would rather locate it elsewhere, add a setenv command to the **.login** or **.cshrc** file that defines the path as:

```

setenv LM_LICENSE_FILE full_path

```

If you are using other software that uses the Highland Digital network licensing scheme, you can combine the ECS **license.dat** file with the **license.dat** file from the other software.

- 9. Install the License Manager daemons on the server machine. The server machine's *hostid* should be listed on the SERVER line of the **license.dat** file.

- 10. Copy the daemons to the /etc directory on the server machine, as shown below. You need to be logged in as "root" to be able to write to this directory.

```

cp -p lmgrd /etc/lmgr

cp -p dataio /etc/dataio

```

11. Start the daemon by issuing one of the following commands:

```

/etc/lmgrd > /dev/null &

```

(license.dat in /usr/local/flexlm/licenses)

```

/etc/lmgrd -c full_path_license.dat > /dev/null &

```

(license.dat in other directory)

12. Add the following lines at the end of the startup file /etc/rc.local:

13. You must unpack the symbol and model libraries before using them. They are shipped in the "ar" format to reduce space and loading time. The **listall** and **expand** scripts in the **mod\_libs** and **sym\_libs** directories are used to list and set up the libraries. Read the comments in the script files for additional information.

Installation is now complete. Exit the root directory and log on as a user.

### Chapter 2 Inside SCS

SCS is a schematic capture system. Unless you're using SCS just for documentation, the schematics are actually the starting point of the development process, not the goal. The schematic will eventually be used to analyze the device's behavior (using a simulator and the Waveform Viewer) or to create a printed circuit board.

The schematic file describes your circuit in terms of the components used and how they connect to each other. The schematic is in SCS's own format, and can be used to create netlists in different formats that are read by other development tools, such as simulators and board layout programs.

Symbols are the most basic elements of a schematic. Symbols represent primitive design elements, whether those elements are individual transistors, complete gates, or a complex IC. A symbol can also be the hierarchical representation of a subcircuit (a "Block" symbol).

This chapter explains what an SCS symbol is, and how symbols are combined with wiring (connectivity) to produce useful schematics. It covers the following topics:

- Symbols

- Attributes

- Schematic elements

- ♦ Schematics relation to netlists

### **Symbols**

In this discussion, "symbol" refers to an electrical symbol, such as a gate or a subcircuit. You can draw graphic-only symbols (such as title blocks) with the Symbol Editor, but these have no electrical meaning.

### **Symbol Libraries**

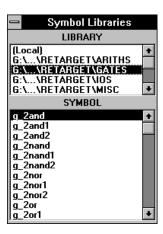

Symbol files are usually organized into libraries or library directories. The basic SCS package comes with libraries of "generic" symbols. Any optional device kits you purchase may come with their own symbol libraries.

Any symbols you create are usually stored in the same directory as the project for which they were created. However, you might want to create your own library directories for symbols used in more than one design. These libraries can be added to the Symbol Libraries Search Paths using the INI Editor.

### What Does a Symbol Consist Of?

Each SCS symbol is a file ending with a .sym extension, and may be included in a library file with a .lib extension. The symbol file contains four types of information: graphics, text, pins, and attributes.

- *Graphics* are instructions that tell the Symbol Editor, Schematic Editor, and Hierarchy Navigator how to draw the symbol.

- *Text* labels the symbol, or adds supplemental information.

- Pins provide electrical connection between the symbol and the schematic's wiring.

- Attributes are parameters that describe the symbol's electrical behavior, the symbol's component parts (for example, its pins), and a number of other useful characteristics.

The following sections explain graphics, pins, and attributes in more detail.

### **Graphics**

Graphics are pictures of the symbols. Symbol graphics have no electrical meaning, showing only the position of the component in the circuit. The electrical behavior of a symbol is defined by its attributes and pins, not the graphics that represent it. Explanatory or descriptive text displayed with a symbol is also considered "graphic" information without electrical meaning.

### **Pins**

Symbol pins are the connecting points between the symbol and the schematic wiring. If the symbol represents an individual component, the symbol pin represents the physical pin where a conductor can be attached. If the symbol represents a subcircuit (block symbol), the symbol pin represents a connection to an internal net of the subcircuit.

### **Attributes**

Attributes associate data items with symbols, pins, and nets. ("Nets" are schematic wiring. Net attributes are explained in more detail later in this manual.) The data items describe the electrical characteristics (or other properties) of the symbols and their pins.

An attribute has a name and a value. You can assign or change the values of most attributes at any point in the development process. You can assign some attributes fixed values that cannot change (for example, part numbers). Some attribute values, such as the vendor's part number and the simulation model, are assigned when a symbol is created. These values are automatically applied to all instances of that symbol. You can assign, change, or override other attributes later in development. You can change individual attribute values to achieve a more accurate simulation, since the model can reflect the exact circuit conditions (such as loading and delay) of separate device instances.

A symbol's attribute set is its single most important component. Without attributes, simulation and modeling programs would know nothing about the electrical behavior of the symbol. The second section of this chapter, "Attributes," introduces the characteristics of attributes and their use. For a full discussion of attributes and attribute use, see the following pages and Chapter 8, "Attributes."

### **Attributes**

An attribute is a characteristic or property associated with a symbol, pin, or net. Attributes can describe:

- ♦ Width or length of transistors

- Price of a resistor

- ♦ Size of a chip or a cell

- Number of connections to a Block symbol

- Delay from input to output

- Number of pins on a package

- Dielectric material of a capacitor

- Length of time taken to design a symbol

- Paint color of a resistor

In short, attributes can describe anything in a design.

### **Attribute Types**

There are four attribute types:

**Global** Global attributes are constants such as feature size, supply

voltage, or identification codes. These attributes are accessible from every sheet of every schematic at every

level of hierarchy.

**Symbol** Symbol attributes describe features related to the whole

symbol. Examples are the width and length parameters of transistors, or SPICE model characteristics. Symbol attributes apply only to the symbol on which they appear. Global attributes (which define such characteristics as

supply voltage) apply to all symbols in a design.

**Pin** Pin attributes describe features related to individual pins.

Polarity, lead number, drive capability, and loading are

typical pin attributes.

Net Net attributes describe characteristics associated with nets.

A good example is the stray capacitance of a net routed across a chip. (Nets are part of schematics, not symbols.

Net attributes apply only to schematics.)

### **Attribute Components**

An attribute has five components.

### Name

An attribute's *name* identifies it to the user. Width, Length, ReferenceDesignator and PinNumber are examples of attribute names.

### Number

The attribute's *number* identifies it to the Editors and the Hierarchy Navigator. SCS uses the number—*not* the name—to reference an attribute. This allows a different name to be assigned without changing the meaning or use of the attribute. (Attributes 0–99 are reserved for SCS, the Editors, the Hierarchy Navigator, and simulation. Most of them have predefined meanings.)

### Value and Value Modifier

Any attribute can be assigned a *value*. A value is usually a number or a text string.

An *attribute modifier* specifies the conditions under which an attribute's value can be changed. Attribute modifiers are fully described in Chapter 9, "The SCS INI Editor."

### Window

Attribute values are displayed in attribute windows. Attribute values cannot be displayed unless a symbol has at least one attribute window.

You add attribute windows to a symbol when you define it. Each window is assigned a unique number and the default attribute that will be displayed in that window. When the symbol is placed in a schematic, the value of the assigned attribute appears in the window.

**Note:** Attribute windows do not have visible outlines. Rather, they are predefined areas on or near the symbol.

### **Creating New Attributes**

The generic symbols supplied with SCS (as well as device-specific symbols) have all required attributes defined and given appropriate values.

In addition, each symbol has about 100 undefined attributes. You can define these attributes for any purpose, such as providing additional information to a netlister, or displaying device data in an attribute window.

If you create your own primitive symbols, you must define the attributes needed by the netlister or simulator. Chapter 8, "Attributes," and Chapter 9, "The SCS INI Editor," cover this in detail.

### **Schematic Elements**

A schematic is composed of the following five items:

| • | Symbols | These can be symbols from the standard SCS libraries, |

|---|---------|-------------------------------------------------------|

|   | -       | symbols representing other schematics you have drawn  |

|   |         | (Block symbols), or symbols you have created from     |

scratch.

Wires Wires connect the symbols. They can be single-signal

("nets") or multiple-signal ("buses").

I/O Markers I/O markers show where signals enter or exit the

schematic, and the direction ("polarity") of the signal (that

is, whether it's an input, output, or bidirectional).

**Graphics &** Graphics and text are usually added to display

Text

explanatory data. They are optional and have no electrical

meaning.

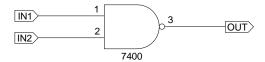

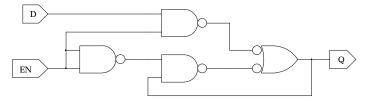

A schematic must contain the first three components—symbols, wires, and I/O markers. A single, isolated component symbol cannot be the only element in a schematic. The schematic must include I/O markers for the external connections to the schematic, and these markers must be connected to the symbol with wires. Figure 2-1 and Figure 2-2 are examples of valid and invalid schematics, respectively.

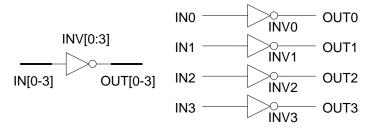

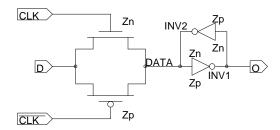

Figure 2-1 Valid Schematic

Figure 2-2

Invalid Schematic (no wires or I/O markers)

The following sections discuss schematic elements in more depth.

### **Symbols**

Symbols are graphic representations of components. They have no electrical meaning.

As you place each symbol, the Schematic Editor automatically gives the symbol a unique *instance name* of the form I\_nn (where nn is an integer). The instance name identifies the symbol to the Schematic Editor and netlister programs. You can change the instance name, but the Editor won't let you repeat an existing name.

Some schematics (such as bit-slice designs) use repeated arrays of symbols (such as registers or inverters). The Schematic Editor lets you define an *iterated instance* in which a single symbol represents many instances of that symbol.

### **Symbol Attributes**

Each symbol has a number of predefined attributes that describe its part number, component type, and other unchanging characteristics. (These were discussed briefly in the preceding section, "Symbols.")

Other attributes can be given values after the symbol is placed in the schematic. These attributes can have different values for each symbol instance. This permits detailed customization of a design.

A good example of an attribute that permits customization is the attribute that controls the speed/bandwidth characteristics of a macro cell. Cells driving internal nodes might be set for full speed, whereas cells driving heavily loaded external nodes might be set for a narrower bandwidth, to obtain greater drive capability.

### Wires

Wires are the lines that electrically connect the symbol pins. Symbol pins are the only connection points for wires. You cannot connect wires to the symbol body itself.

There are two types of wires: single-wire *nets* and multiple-wire *buses*. Buses allow more than one signal to be routed as single line. (Nets and buses are explained in more detail in Chapter 5, "Using the Schematic Editor.")

### **Wire Names**

Wires have names. These names identify the wires to the Schematic Editor and netlister programs.

You would normally name all wires that connect to inputs or outputs and any "internal" nets with signals you want to view during simulation. You can use any name you like, but you usually choose a name that suggests the name or function of the signal carried by that wire. If you don't give a wire a name, the Schematic Editor automatically supplies one, of the form N\_n (where n is an integer).

Multi-wire buses are created by giving a single wire a compound name. You can then tap off any signal you want anywhere along the bus.

Buses are most often used to group related signals, such as a 16-bit data path. However, a bus can be any combination of signals, related or not. Buses are especially useful when you need to route a large number of signals from one side of the schematic to the other.

Buses also make it possible for a single I/O marker to connect more than one signal to a Block symbol. The signal names don't have to match, but both pins must carry the same number of signals.

### **Net Attributes**

Like symbols and symbol pins, nets (the wiring that connects symbols to each other and makes external connections) can also have attributes. These attributes include the net's name (as assigned in the schematic), plus the net's length, width, unit capacitance, and so on. There are also net attributes that pass parameters to other programs such as simulators or PCB layout programs.

### I/O Markers

I/O markers mark the points at which signals leave or enter the schematic. They are required. Any unconnected wire without an I/O marker will eventually be flagged as an error when you try to create a netlist, run the simulator, or load the design into the Hierarchy Navigator.

The I/O marker automatically takes the name of the wire it is attached to. If the wire is a bus, the marker will have the same compound name as the bus.

When a Block symbol and its matching schematic are created, the I/O markers for the signals that enter and leave the schematic must have the same names as the corresponding pins on the Block symbol. The matching names identify which signal attaches to which pin.

### **Graphics**

Although symbols, wires, and I/O markers are visible, graphical items, they also have a functional or electrical meaning. In this context, "graphics" refers to the non-functional graphical parts of the schematic.

For example, you might add graphics showing the expected waveforms at different points in the circuit. Or, you could draw the company's logo and add it to each schematic for identification.

The most common use of graphics is to create a title block. The block shows the name and address of your company, and can include the company logo and blank spaces for the project name, schematic sheet number, and so on.

### **Text**

Text, like graphics, can provide additional information about the schematic or its project. Text can be placed anywhere on a schematic, even if it overlaps symbols or wires.

### **Schematics Relation to Netlists**

A *netlist* is a file listing all the components (symbols) in a schematic, and their *connectivity* (how they are wired together).

There is no single, universally accepted netlist format. The Schematic Editor stores a schematic in its own proprietary connectivity database format. This database format can be converted to almost any netlist format. However, data and data structures not supported by the target format will not appear in the converted file.

The conversion is performed with netlister programs. SCS comes with several that can convert schematics to and from a number of standard formats: ASCII, EDIF, and a generic human-readable format. (Additional netlisters are optional.) The ASCII format retains all the information in the original schematic file.

### **Using Netlists**

The netlist is the "interface" between your design and any other software that needs to read or use the design. These programs include

- **♦** Simulators

- PCB layout programs

- ♦ IC place-and-route software

- Synthesis software

- Signal integrity tools

## Chapter 3 Introduction to Hierarchical Design

SCS supports full hierarchical design. Hierarchical structuring permits a design to be broken into multiple levels, either to clarify its function or permit the easy reuse of functional blocks. This chapter covers the following topics:

- ♦ What is a Hierarchy?

- Advantages of Hierarchical Design

- Approaches to Hierarchical Design

- What is Hierarchical Organization?

- Symbols, Schematics, and Hierarchy

- Hierarchical Design Structure

- Hierarchical Naming

- Nets in the Hierarchy

### What Is a Hierarchy?

A large, complex design does not have to been drawn as a single schematic. The Schematic Editor lets you add as many sheets as needed, so that a design can extend beyond the original sheet. However, regardless of how many sheets you add, all the components of the design are still at a single level.

Another way to organize a design is to break it up into components or modules. Circuitry for a specific function or interface can be drawn as a separate schematic. A Block symbol is then created for this schematic, which can be placed in other schematics as a single symbol.

The schematic represented by the Block symbol is said to be at one level *below* the schematic in which the symbol appears. Or, the schematic is at one level *above* the Block's schematic. Regardless of how you refer to the levels, any design with more than one level is called a *hierarchical* design. In SCS, there is no limit to the number of hierarchical levels a design can contain.

### **Advantages of Hierarchical Design**

The most obvious advantage of hierarchical design is that it encourages modularity. A careful choice of the circuitry you select to be a module will give you a Block symbol that can be reused.

Another advantage of hierarchical design is the way it lets you organize your design into useful levels of abstraction and detail. For example, you can begin a project by drawing a "top" schematic that consists of nothing but Block symbols and their interconnections. This schematic shows how the project is organized, but does not display the details of the modules (Block symbols).

You then draw the schematic for each Block symbol. These schematics can also contain Block symbols that you have not yet drawn schematics for. This process of *decomposition* can be repeated as often as required until all components of the design have been fully described as schematics.

Breaking the schematic into modules adds a level of abstraction that lets you focus on the functions (and their interaction) rather than on the hardware that implements them. At the same time, you are free to view or modify an individual module.

Although there are many ways of "breaking apart" a complex design, some may be better than others. In general:

- Each module should have a clearly defined purpose or function and a well-defined interface.

- Look for functions or component groupings that can be reused in other projects.

- The way in which a design is divided into modules should clarify the structure of the project, not obscure it.

When trying to decide what a module should contain, consider what Albert Einstein might say: "A module should be as complex as it needs to be, but *no more* complex."

### **Approaches to Hierarchical Design**

The Schematic Editor supports full hierarchical design. Project components can be created in any order, then combined into a complete design. You can draw a schematic first, then create a Block symbol for it, or specify the Block first, then create the schematic for it later.

Hierarchical entry is a convenient way to enter a large design "one piece at a time." It is also a way of organizing and structuring your design and the design process. The choice of the appropriate methodology can speed the design process and reduce the chance of design or implementation errors.

There are three basic approaches to creating a multi-module hierarchical design:

- ♦ Top-Down

- ♦ Bottom-Up

- ♦ Inside-Out ("mixed")

The following three sections explain the philosophy and techniques of each approach.

### **Top-Down Design**

In top-down design, you do not have to know all the details of your project when you start. You can begin at the "top," with a general description of the circuit's functionality, then break the design into modules with the appropriate functions. This approach is called "stepwise refinement"—you move, in order, from a general description, to modularized functions, to the specific circuits that perform those functions.

In a top-down design, the uppermost schematic usually consists of nothing but Block symbols representing modules (plus any needed power, clocking, or support circuitry). These modules are repeatedly broken down into simpler modules (or the actual circuitry) until the entire design is complete.

### **Bottom-Up Design**

In bottom-up design you start with the simplest modules, then combine them in schematics at increasingly "higher" levels. Bottom-up design is ideal for projects (such as interfaces) in which the top-level behavior *cannot* be defined until the low-level behavior is established.

### Inside-Out ("Mixed") Design

Inside-out design is a hybrid of top-down and bottom-up design, combining the advantages of both. You start wherever you want in the project, building "up" and "down" as required.

SCS fully supports the "mixed" approach to design. This means that you can work bottom-up on those parts of the project that must be defined in hardware first, and top-down on those parts with clear functional definitions.

Regardless of the approach you choose, you start from those parts of the design that are clearly defined and move up or down to those parts of the design that need additional definition.

# What is Hierarchical Organization?

The Schematic Editor uses a hierarchical system to organize complex designs. Like a series of increasingly detailed maps, a hierarchy of schematics lets the designer move from a general view (the entire country) to more-detailed views (counties, cities, and neighborhoods).

At the top level in the hierarchy, the full design is represented as a complete (but relatively undetailed) schematic. As you descend the hierarchy, you see more-detailed views of smaller circuit elements. Primitive elements (library symbols) are visible at the lowest level.

Although hierarchical designs are created in the Schematic Editor, a schematic can be viewed in its full hierarchical context only from within the Hierarchy Navigator. The Navigator lets you view each circuit component in its hierarchical context, and move up and down in the hierarchy. See Chapter 7, "Using the Hierarchy Navigator," for a detailed explanation.

# Symbols, Schematics, and Hierarchy

In the Schematic Editor's hierarchy, a symbol at one level (a "functional block") represents a more-detailed schematic at the next-lower level. Hierarchical symbols must meet the following three requirements:

- The symbol must have the same base name as the schematic containing the underlying circuitry. This associates the schematic with the symbol representing it.

- 2. The pin names on the symbol must match the I/O marker names in the underlying schematic.

- 3. The symbol should be a Block symbol. If the symbol used is in a model directory, it can also be a Cell symbol.

The Block symbol is associated with its schematic by giving the schematic nets the same names as the corresponding symbol pins. For example, a wire connected to a pin named  ${\bf Q}$  on the symbol is also connected to the net named  ${\bf Q}$  in the underlying schematic. The Consistency Check command of the Schematic Editor and the ERC Check command in the Hierarchy Navigator flag an error if a Block symbol has a pin without a corresponding net in the related schematic.

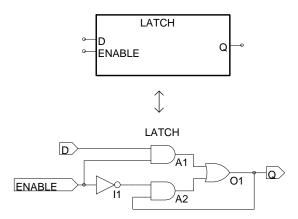

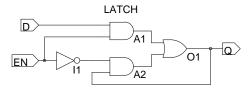

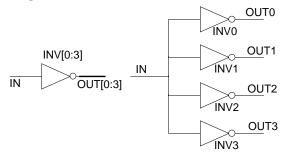

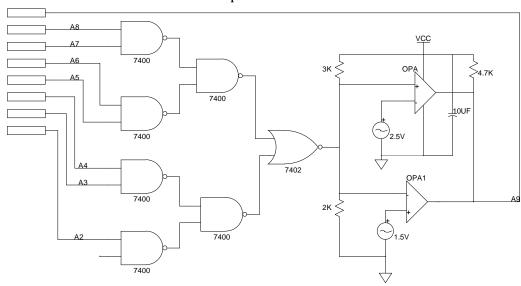

In Figure Figure 3-1, pin D on the Block symbol corresponds to the net in the schematic, which is named D. The other pins, Q and ENABLE, also correspond to named nets in the schematic.

Figure 3-1

A Block Symbol and Its Underlying Schematic

# **Hierarchical Design Structure**

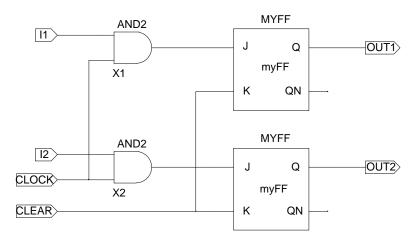

When a symbol is placed in a schematic, the component or sub-circuit the symbol represents is added to the circuit. When you place a latch symbol (for example) you are actually including the OR gate, inverter and two AND gates from the latch's schematic.

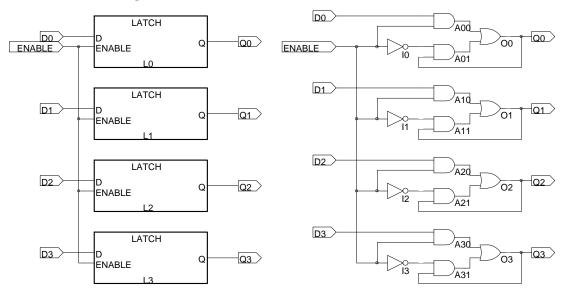

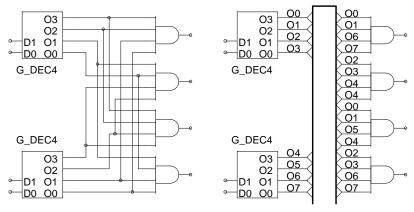

Figure 3-2 shows (on the left) a 4-bit register (REG4) constructed from four latch symbols (**latch.sym**). The right side of the figure shows the underlying components. The four **latch** symbols represent a total of eight AND gates, four OR gates, and four inverters.

This hierarchical building process could be repeated by using the Schematic Editor's Matching Symbol command to create a symbol for schematic **reg4**, then placing the **reg4** symbol in a higher-level schematic. If you created a schematic for a 16-bit register, **reg16**, by placing four copies of symbol **reg4**, you would be defining a circuit with a total of 64 gates. But instead of having to view 64 gates on a single level, you can work with symbols that represent gates, at the appropriate level of detail.

Figure 3-2 Circuit REG4 and its Equivalent Circuit

# **Hierarchical Naming**

In the **latch** schematic (Figure 3-2), the inverter has the instance name I1. In schematic **reg4**, four copies of the symbol **latch** are placed and assigned instance names L1 through L4. Schematic **reg4** therefore contains four copies of inverter I1.

The Hierarchy Navigator distinguishes among these otherwise identical inverters by combining the inverter's instance name with the instance name of the latch containing it. The four inverters are therefore named (in the Hierarchy Navigator):

- L1.I1

- L2.I1

- L3.I1

- L4.I1

If we created a 16-bit register by combining four **reg4** symbols (as suggested previously), the resulting schematic would represent a new hierarchical level, containing four copies of **reg4** (named R1 through R4). Each copy of **reg4** contains the four inverters as named above. The Hierarchy Navigator would then name the 16 inverters by combining the instance names of the four **reg4** symbols with each of the four instance names of the inverters as follows:

```

R1.L1.I1, R1.L2.I1, R1.L3.I1, R1.L4.I1

R2.L1.I1, R2.L2.I1, R2.L3.I1, R2.L4.I1

R3.L1.I1, R3.L2.I1, R3.L3.I1, R3.L4.I1

R4.L1.I1, R4.L2.I1, R4.L3.I1, R4.L4.I1

```

When you view an individual latch schematic in the Schematic Editor, you see the instance names of the gates, without the hierarchical context. When the schematic becomes part of a larger design and is viewed in the Hierarchy Navigator, the instance names include the hierarchical path (as shown above) to assure their uniqueness.

# **Nets in the Hierarchy**

The schematic definition for the latch circuit contains both *local* and *external* nets. The output of the inverter is connected to the AND gate with a local net. Two other local nets connect the outputs of the AND gates to the inputs of the OR gate. Assume these nets have been named N1, N2, and N3. When the 16 copies of this circuit are combined in **reg16**, 16 copies of these local nets are created.

The 16 local nets named N1 are individual nets, *not* branches of the same net, so the Hierarchy Navigator creates a unique name for each. The local net name (N1) is prefixed with the instance name of the schematic where the net is defined. A dash separates the net and instance names. The 16 N1s then become:

```

R1.L1-N1, R1.L2-N1... R4.L3-N1, R4.L4-N1

```

The **latch** schematic contains three external nets, D, ENABLE, and Q. The symbol pins on the latch connect these nets to the hierarchical level above.

#### **Automatic Aliasing of Nets**

When a design is loaded into the Hierarchy Navigator, nets take the name of the highest ("top") net in the design. That is, the name of top-level net propagates downward through the hierarchy to override the "local" name. By forcing all nets to the same name, this "aliasing" feature greatly speeds signal tracing in a multi-level design.

In the preceding example, the net name D from the latch is overridden by the higher-level external reference to become D1, D2, D3.... This override becomes the reference at all levels of the hierarchy. If, in the suggested 16-bit register the D0, D1, D2... inputs were connected to wires named and marked Bit0, Bit1, ... Bit15, these new names take precedence and the D0, D1, D2... names would no longer be accessible at any level of the hierarchy.

# Chapter 4 Basic Operation

This chapter has basic information about the Synario Capture System. It covers the following topics:

- What SCS Can Do

- SCS Programs

- Using the SCS Executive

- SCS Executive Features

- Schematic Exchange/Conversion Utilities

- Customizing the Executive with the pcshell.ini File

- SCS Command Structure

- Using the Mouse

- Prompting and Error Messages

- **♦** Error Recovery

- Network Operation

- Naming Design Files

- Saving Files

- Printing and Plotting

- The INI Editor

# What SCS Can Do

SCS is a design entry and analysis package for schematic-based IC and PCB designs. It features:

Schematic Capture — The Schematic Editor captures your design logic (either IC or PCB) in schematic form. You can use the schematic files solely for documentation, or as sources for other software that fits your design into ASICs or creates printed circuit boards.

The schematic file is continuously updated as you draw, so it is always ready for analysis.

- Netlist Generation Your design can be converted into industry-standard EDIF or ASCII netlists for use by other design tools. Additional netlisters are available as an option.

- Consistency Checking You can check your schematics at any time for such errors as unconnected wires or shorted nets. These checks greatly increase the likelihood your design will be correct.

- Electrical Rules Checking Electrical rules checks catch such errors as

having too many loads connected to one output. This checking prevents

electrical incompatibilities that would keep your design from working.

- Hierarchical Design Designs are not limited to a single schematic. Block symbols can represent a complete schematic or any subsection of a schematic. These symbols can be used to create a hierarchical design, or to create reusable function modules. There is no limit to the number of hierarchical levels a design can contain.

- Hierarchical Viewer The Hierarchy Navigator lets you view a multi-level design in its full context. Back annotations can be added as comments or modifications to the design.

- Symbol Creation You can create your own electrical (or decorative) symbols and give them whatever characteristics you want. Or, you can convert a schematic into a Block symbol to make your design easier to understand, or for reuse in other projects.

- Documentation SCS comes with a complete set of generic symbols. You

can create schematics to document your design, or produce netlists (in

standard EDIF or ASCII formats) for use by other design tools.

- PCB Interface and Packaging SCS can also be used for printed circuit board design. Its packaging features include automatic package assignment, consistency checking, and the ability to back annotate a design with modifications or notes.

- ♦ **Simulator Interface** Most simulators can be used with SCS. EDIF and ASCII netlist generation is a standard feature. Optional netlisters for a variety of simulator formats are available.

- Waveform Tools The Waveform Viewer lets you view the results of simulation. The waveform at any node in your design can be displayed.

Full cross-probing with the Hierarchy Navigator is supported. Click on a node in the Navigator to view its waveform in the Viewer.

- The *Waveform Editing Tool (WET)* lets you create input stimulus waveforms for your design graphically, by clicking and dragging directly on the screen. The waveform tools are described in the *Waveform Tools Manual*.

# **SCS Programs**

SCS is a program for entering and analyzing schematic-based designs. Designs can be single-level ("flat") or multi-level ("hierarchical"). In all cases, the full design can be converted to a variety of netlist formats for use with other design and production software.

SCS consists of the following principal components:

- The SCS Executive (SCS/ECS Only) This shell program calls the other SCS programs as you need them, and passes any required command line options. It also executes a number of utilities, such as the initialization file editor and netlist converters. You can customize the Executive.

- ◆ The Schematic Editor Your schematic designs are captured by this tool. Schematics can be drawn on multiple "sheets" and be of any size.

- The Symbol Editor If you need a symbol that is not in the SCS library, you can create it with the Symbol Editor. You can also design special purpose non-component symbols (such as logos and title bars). The Symbol editor can also create a symbol for any existing schematic, so that that schematic can be used as a module in other schematics.

- The INI Editor The INI Editor configures the initialization ("INI") file for SCS. All default settings and user preferences for the Editors, Hierarchy Navigator, Waveform Viewer, and Waveform Editing Tool are set with the INI Editor. It is also the editor for symbol, pin, and net attributes.

- The Hierarchy Navigator All the elements and levels of a design are combined by the Hierarchy Navigator for viewing and analysis. Analysis is fully interactive. You can back annotate a design, then view the effects of your changes.

- The Waveform Viewer The Waveform Viewer works with the Hierarchy Navigator to display the internal operation of your design. Once you have simulated the design, you can display waveforms from any schematic, at any level in the hierarchy. "Crossprobing" lets you jump at any time between a signal line in the schematic (as displayed by the Navigator) and the signal itself (as displayed by the Viewer).

- Waveform Editing Tool The Waveform Editing Tool (or WET) lets you create the stimulus waveforms for simulation graphically, by drawing them directly on the screen. The stimuli can be edited graphically, or by modifying values in dialog boxes. The WET then converts the waveforms into a stimulus file that your simulator recognizes. Waveform files are also useful as input to automatic test equipment, or as documentation of the circuit's expected behavior.

# **Using the SCS Executive**

(SCS/ECS Only) The SCS Executive is the first thing you see when you run SCS. You can launch the Schematic Editor, Symbol Editor, or Hierarchy Navigator directly from the Executive. The Executive also gives you easy access to a number of utility programs, including schematic exchange/conversion utilities and the INI Editor.

#### **Running the Editors or Hierarchy Navigator**

The most common use of the SCS Executive is to launch one of its three principal applications.

- Click the appropriate radio button: Navigate Hierarchy, Edit Schematic, or Edit Symbol. The label of the edit box changes accordingly, as does the default file extension (\*.tre, \*.sch, \*.sym). The list box shows the corresponding files in the current directory.

- 2. If you want a different file extension (or a specific file name), type it into the edit box and press ENTER. The contents of the list box change to reflect the new specification.

- 3. If you want a different directory, double-click on a directory or the double dot [..] in the list box to change the directory.

- 4. Double-click on the file name you want to work with. Or highlight the name and click on RUN. If you want to create a new schematic, symbol, or hierarchy file, click on NEW instead.

You don't have to use the SCS Executive; you can run these applications from the command line or File Manager. However, the Executive simplifies the process by automatically passing the selected file name to the program.

#### **Editing Files**

The SCS Executive can be used to search for a file you want to edit and load it into the Notepad editor.

- Choose the View menu. A list of wildcards for various file types is displayed, along with the universal wild card (\*.\*).

- 2. Click on the file type you want to edit. The contents of the list box are immediately updated to show files of the type you selected.

- 3. If the file you want is not in the current directory, double-click on a directory or the double dot [..] in the list box to change the directory.

4. Double-click on the file name you want to edit. Or highlight the name and click on RUN. The Notepad is invoked and the selected file is loaded. If you want to create a new text file (of any type), click on NEW instead.

**Note:** When you select one of the utility programs (such as the Notepad editor, or the utilities described below), the radio button at the bottom of the window changes from "Utilities" to the name of the selected utility. The name remains there until you select another utility. You can call the Editors or Hierarchy Navigator, then click the bottom button to return to the last-used utility without having to reselect it from the menus.

#### Schematic Exchange/Conversion Utilities

The conversion utilities work in much the same way as loading or editing a file.

- 1. Choose the Utilities menu.

- 2. Select the type of conversion you want to perform. The contents of the list box change immediately to show only files of the appropriate source type.

- 3. If the file you want is not in the current directory, double-click on a directory name or the double dot [..] in the list box to change the directory.

- 4. Highlight the name of the file you want to convert, then click on ONE. To convert all files in the current directory, click on ALL. The converted files are placed in the same directory as the source files.

#### **Setup Utilities**